1.时钟/时钟树的属性

一般的时钟,我们都指的是全局时钟,全局时钟在芯片中的体现形式是时钟树。

时钟树,是个由许多缓冲单元(buffer cell)平衡搭建的时钟网状结构,如下图所示:

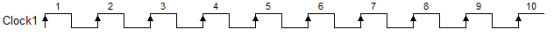

实际的时钟除了周期/频率、相位、沿、电平属性外,还有其他的属性,也就是:不是下面这样子规规整整的:

实际的时钟属性(“实际的buff”):

①时钟的偏移(skew):

时钟分支信号在是指同样的时钟产生的多个子时钟信号之间的延时差异。skew通常是时钟相位上的不确定。由于时钟源到达不同寄存器所经历路径的驱动和负载的不同,时钟边沿的位置有所差异,因此就带来了skew。完成布局布线后,物理路径延时是固定的,所以在设计中考虑到时钟偏移,就可以避免偏移带来的影响。

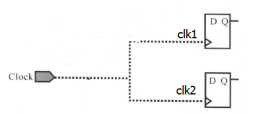

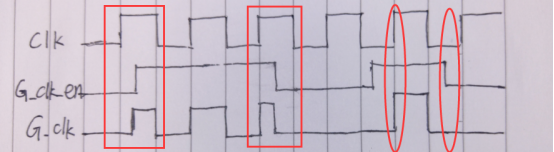

到达寄存器的时钟端口过程中,都存在有线网等延时,由于延时,到达寄存器时钟端口的时钟信号存在有相位差,也就是不能保证每一个沿都对齐,这种差异称为时钟偏移(clock skew),也叫时钟偏斜。时钟的偏移如下图所示:

②时钟抖动(jitter):

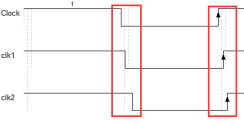

指的是时钟周期的变化,两个时钟周期之间存在的差值,也就是说时钟周期在不同的周期上可能加长或缩短。这个误差是在时钟发生器内部产生的,它是一个平均值为0的平均变量。和晶振或者PLL内部电路有关,布线对其没有影响。在设计中无法避免它能带来的影响,通常只能在设计中留有一定的margin.

相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动,如下图所示:

时钟的抖动分为随机抖动(Random Jitter)和固有抖动(Deterministic jitter):

·随机抖动的来源为热噪声、Shot Noise和Flick Noise,与电子器件和半导体器件的电子和空穴特性有关,比如ECL工艺的PLL比TTL和CMOS工艺的PLL有更小的随机抖动;

·固定抖动的来源为:开关电源噪声、串扰、电磁干扰等等,与电路的设计有关,可以通过优化设计来改善,比如选择合适的电源滤波方案、合理的PCB布局和布线。也就是说:jitter与时钟频率无直接关系。 时钟的偏移和时钟的抖动都影响着时钟网络分枝的延迟差异(相位差异),在Design Compiler里面,我们用时钟的不确定性(uncertainty)来表示这两种情况的影响。

③时钟的转换时间(transition) :

时钟的转换时间与单元的延时时间(也就是器件特性)还有电容负载有关。

时钟的上升沿跳变到下降沿或者时钟下降沿跳变到上升沿的时间,这个时间并不是如左下图所示那样完全没有跳变时钟的,而是像右下图那样,时钟沿的跳变时间就是时钟的转换时间。

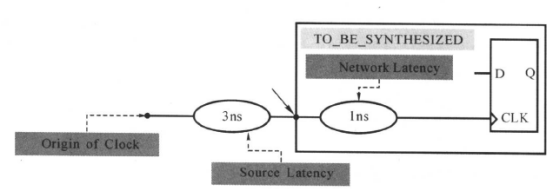

④时钟的延时(latency) :

时钟从时钟源(比如说晶振)出发到达触发器时钟端口的延时,称为时钟的延时,包含时钟源延迟(source latency)和时钟网络的延迟(network latency),如下图所示:

时钟源延迟(clock source latency),也称为插入延迟(insertion delay),是时钟信号从其实际时钟原点到设计中时钟定义点(时钟的输入引脚)的传输时间,上图是3ns。

时钟网络的延迟( clock network latency)是时钟信号从其定义的点(端口或引脚)到寄存器时钟引脚的传输,经过缓冲器和连线产生的延迟(latency),上图是1ns。

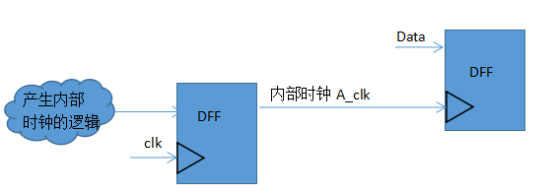

2.内部时钟

在verilog代码中,经常使用内部产生的时钟,也就是用内部的一个信号充当另外一个always块的时钟沿敏感列表,如下图所示:

实际上,这种内部时钟不建议使用,一个是因为产生内部时钟的逻辑是有延时的,导致A_clk产生也会延时,Data与A_clk会有延时,就会有亚稳态的稳压;另外一个就是由触发器生成A_clk的驱动能力问题.

3.多路复用时钟

在一个系统里面,很有可能会用到多个时钟轮流驱动一些触发器,为了适应不同的数据速率要求,进行时钟切换。有时为了节约功耗,也会把高速时钟切换到低速时钟,或者进行时钟休眠操作,多路时钟如下图所示:

这样的时钟一般情况下也会导致一些问题,比如时钟切换时导致后面驱动的寄存器建立时间不足,当满足一定的条件时,这种多路复用器的时钟也是可以使用的,要满足的要求有:

·时钟复用电路一旦上电工作之后,就不要对复用逻辑进行更改,以免更改之后产生不确定错误。

·在测试的时候,设计电路绕过时钟多路逻辑来选择普通的时钟,也就是使用普通的时钟进行测试。

·在时钟进行切换的时候,寄存器要处于复位的状态,以免在切换之后建立时间不够而进入亚稳态。

·在时钟切换的时候,可能会产生一些短暂的错误,但是这些错误对整个系统没有影响。

对于系统要求非常严格的,比如时钟切换很频繁,有不能够在复位的时候切换,而且也不允许有短暂的错误,那么时钟就不能这样子进行切换了,就要使用其他的时钟切换方案或者进行时钟同步了。

4.门控时钟

门控时钟就是在使能信号有效的时候,把时钟打开;使能信号无效的时候,时钟关闭。时钟关闭之后,它所驱动的寄存器就不会翻转,因此也就降低了动态功耗。

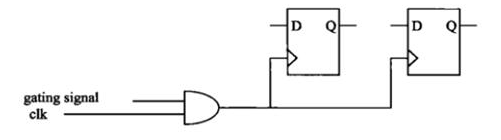

- 门控时钟开始电路

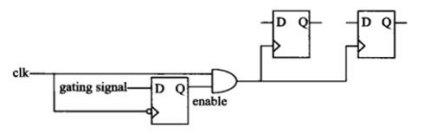

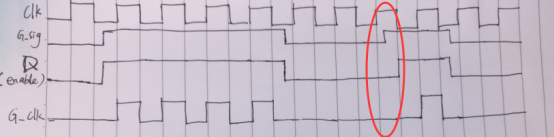

从波形图中可以看到,门控使能信号如果在时钟的高电平的时候开启或者关闭,就会导致产生的门控时钟高电平被截断,变成毛刺;门控使能信号对在时钟低电平时跳变对产生的门控时钟没有影响。因此我们的针对点就是高电平时的翻转。 - 改进的门控时钟电路

让门控使能信号在通过这个逻辑电路之后,仅仅在时钟低电平的时候进行翻转,而在时钟高电平的时候,不能翻转也就是保持。从而我们就想到了低电平触发的锁存器,使能信号通过低电平的锁存器之后,如果使能信号在高电平跳变,锁存器的输出信号是不会改变的,电路图如下所示:

当门控使能信号是高电平有效的时候,也就是高电平打开门控时钟,低电平关闭门控时钟,那么就使用上面的电路,也就是:低电平触发的锁存器+与门。

当门控使能信号是低电平有效的时候,那么就要换成:高电平触发的锁存器+或门。

PS:当涉及毛刺的问题的时候,特别是由于使能信号与时钟而产生的毛刺,锁存器起很大的作用。

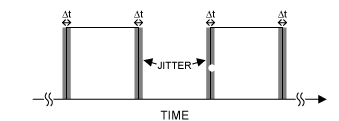

5.行波时钟

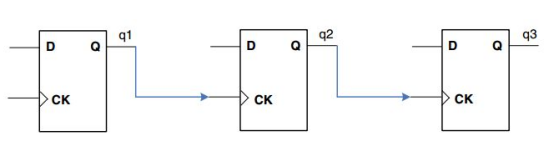

行波时钟,也就是一个触发器的输出用作另一个触发器的时钟输入,经常用在异步计数器和分频电路设计中,如下图所示:

异步计数器/分频时钟虽然原理简单、设计方便,但级连时钟(行波时钟)最容易造成时钟偏差,级数多了,很可能会影响其控制的触发器的建立时间和保持时间,使设计难度加大;转换的方法是采用同步计数器。

6.双边沿时钟

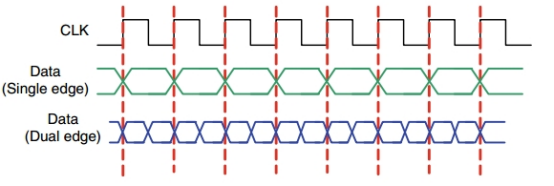

双边沿时钟的系统是指在时钟的上升沿和下降沿都进行数据传输:

很显然,这样子数据的传输速率就增加一倍了。DDR就是采用双边沿传输数据的技术。

然而一般情况下,我们不建议使用双边沿时钟,这是因为:

·由于上下沿都用,要求时钟的质量很高,一般的时钟源很难达到,成本高。

·由于时钟的抖动等不确定因素的存在,容易使时钟的占空比发生改变,因此容易引起建立时间和保持时间的违规。

·当使用的双沿时钟之后,时钟的约束变得复杂,此外当某处发生违规之后,违规的路径的查找难度比单沿时钟大。

·还有一点就是测试难度比较大,双沿电路的测试电路必定有别与单沿的测试电路。进行扫描测试时,上下沿的时钟先都得插入多路复用器进行选择。