新建一个ISE工程,然后创建一个Ip核。

![image_1cvl8o3srroo1fmc1ohn1e4c66i9.png-84.6kB][1]

选择MIG Virtex-6的ip,双击。

1.双击打开IP核设置的界面。

点击next

2.第二个界面

然后点击next

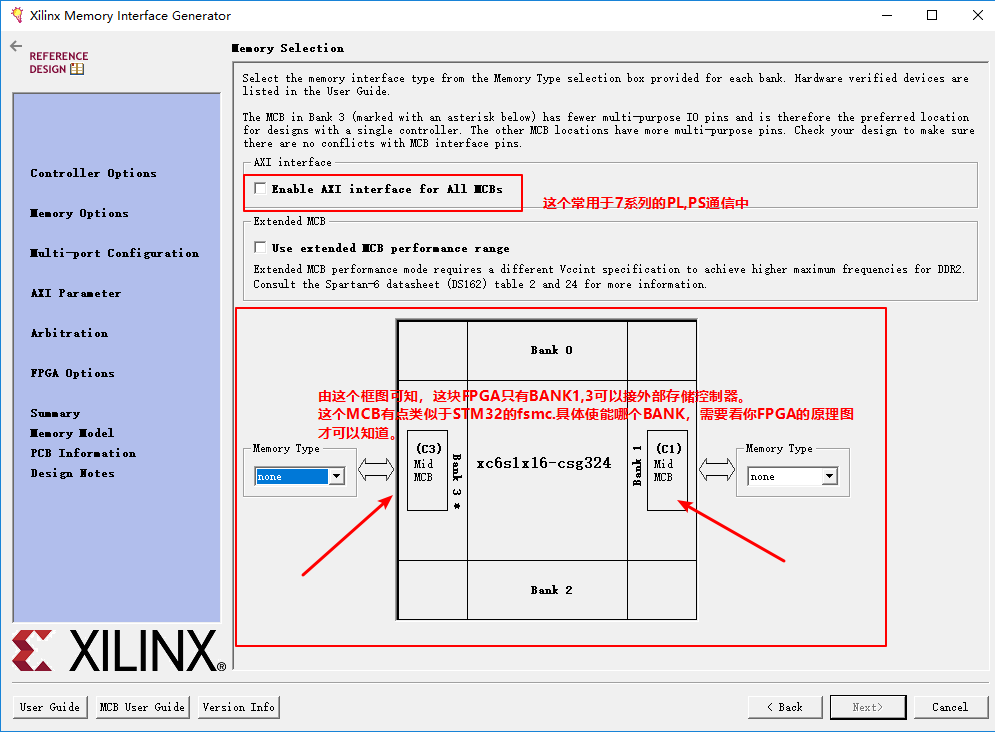

3.第三个界面

我们这里不勾选,直接next

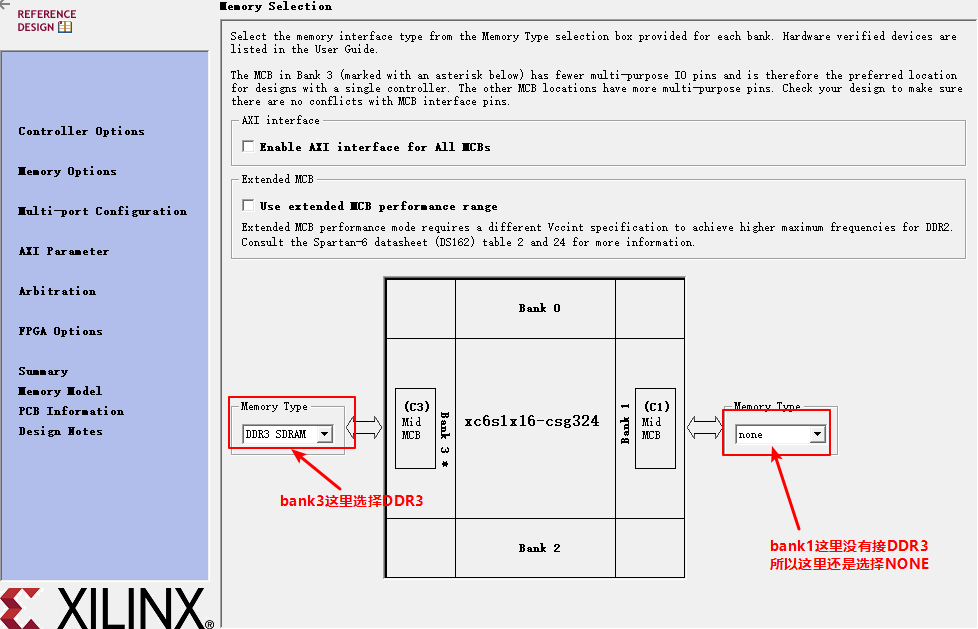

4.

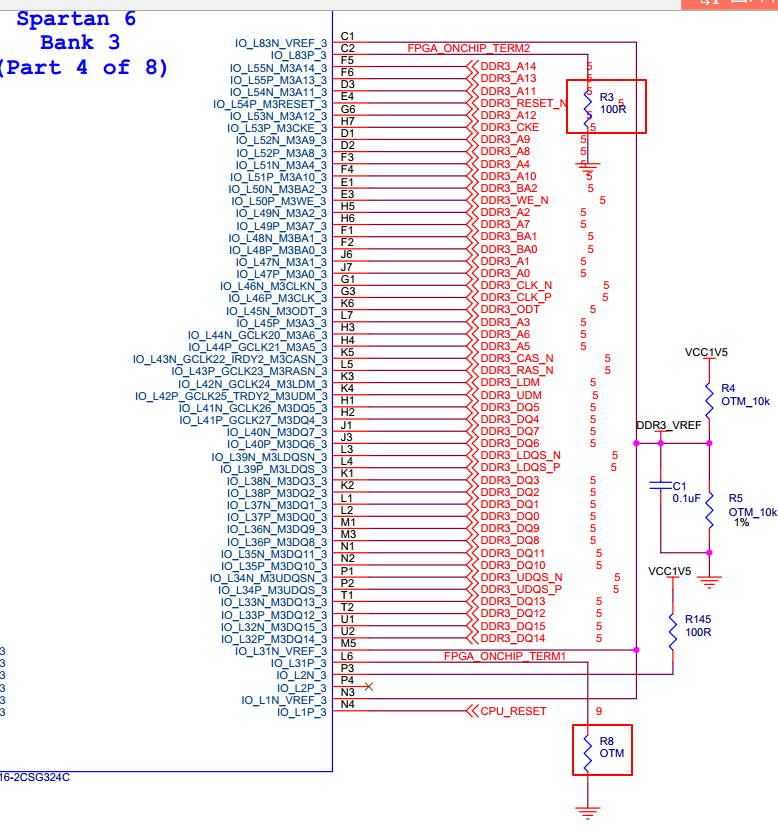

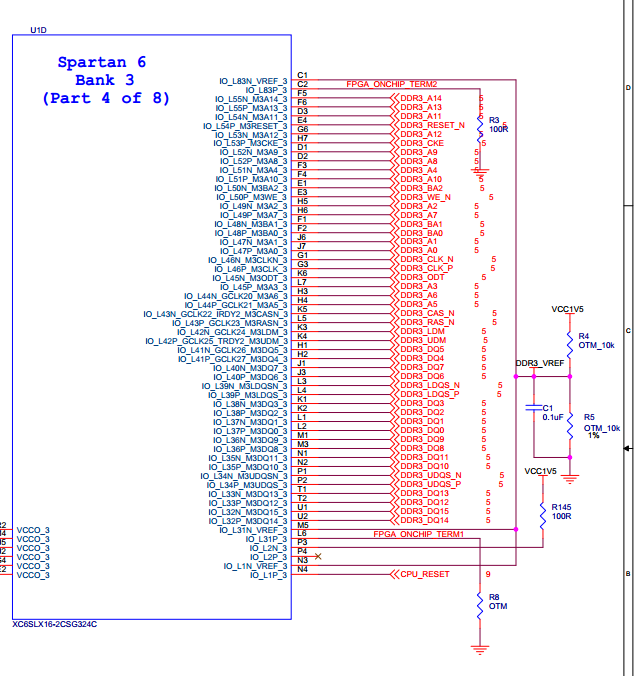

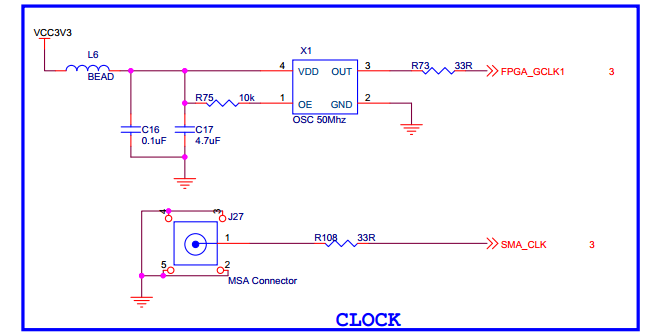

FPGA的原理图,由图可知这块板子的DDR3接着FPGA的BANK3

最后IP核的设置

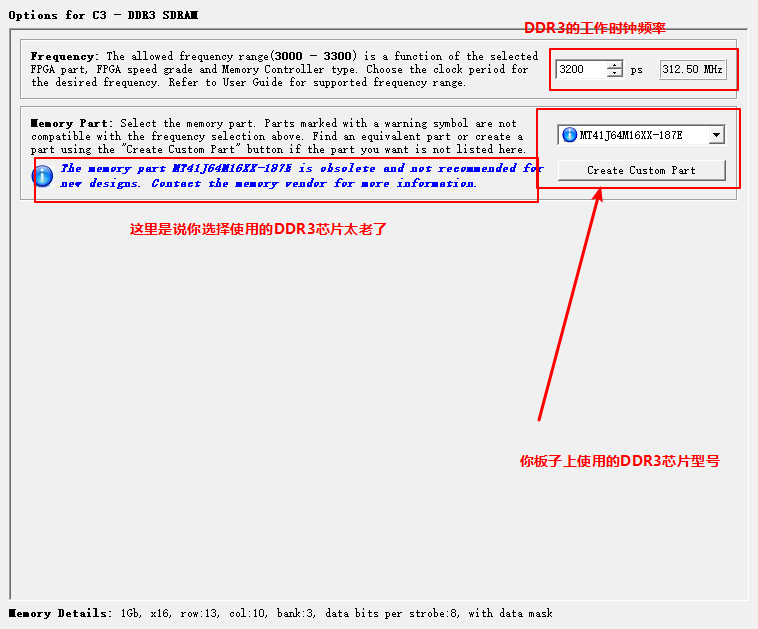

5.选择DDR3时钟的工作频率

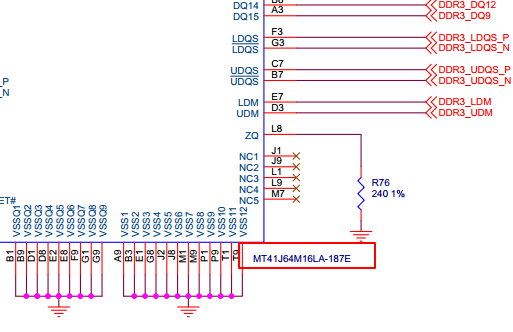

开发板上的DDR3芯片MT41J64M16LA-187E对应上就行。

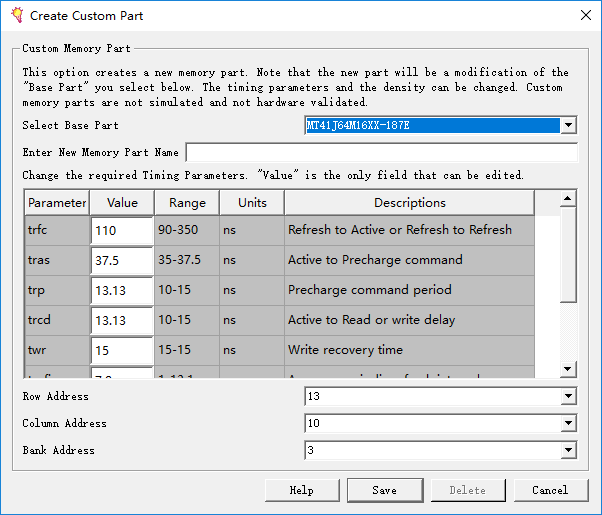

如果你板子上的DDR3芯片型号没有,那么先选择与你板子上DDR3最相近的信号,然后点击Creat custom part

看你DDR3芯片手册,将这些时序参数写进去。

填好之后,继续点击NEXT。

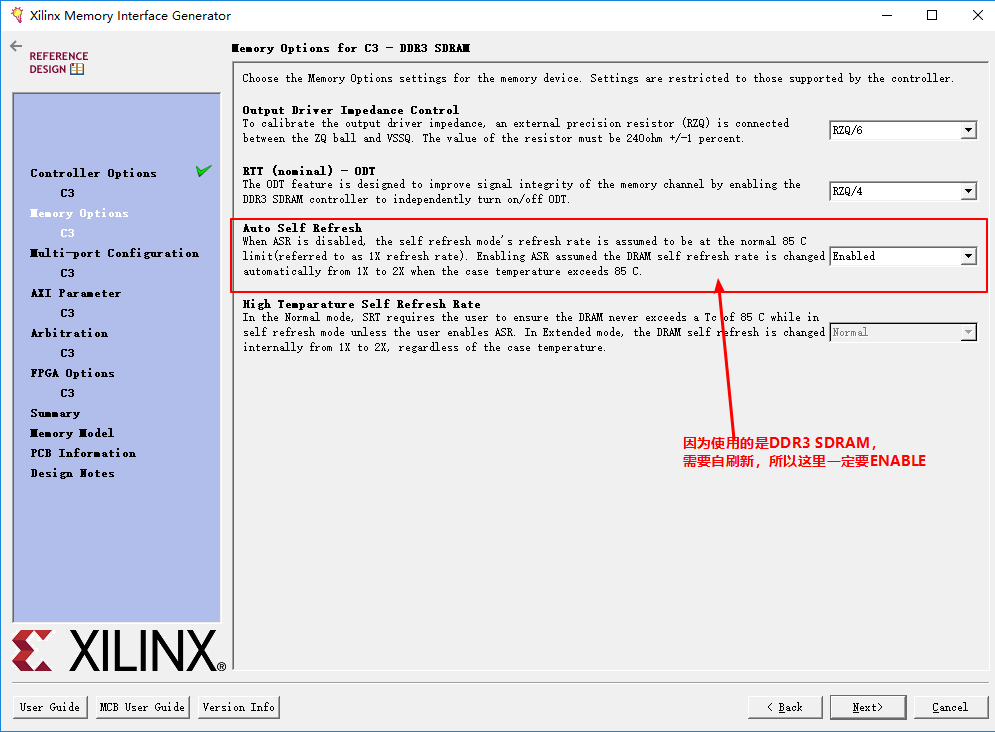

6.memory options 设置,什么都不用变,直接next

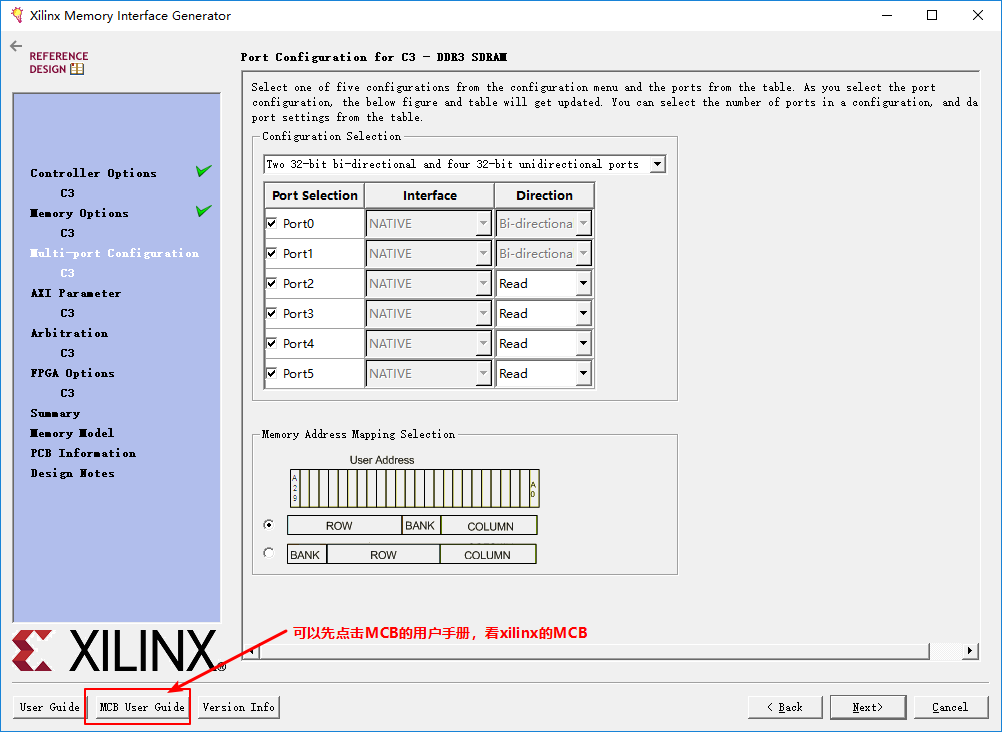

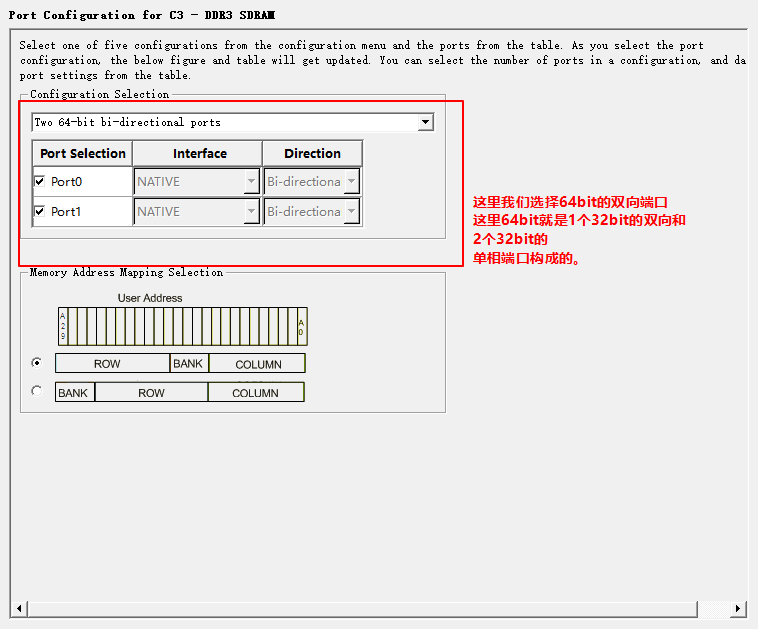

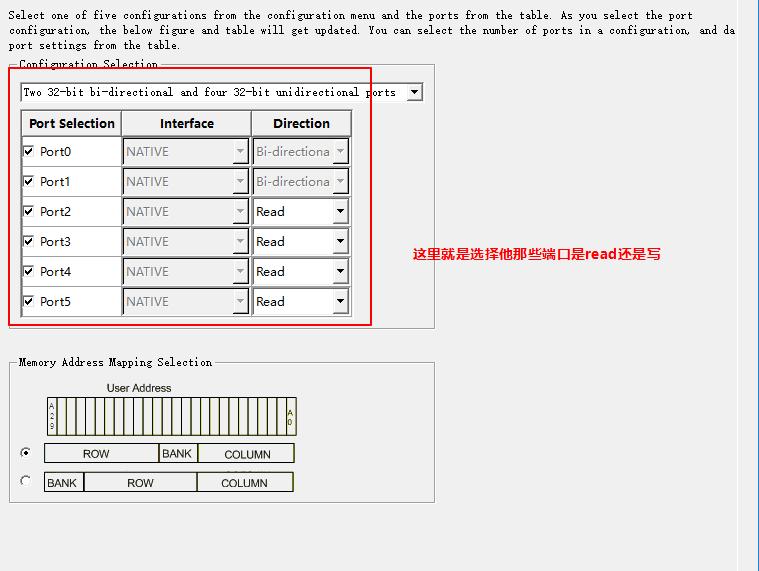

7.选择Memory port的方式。

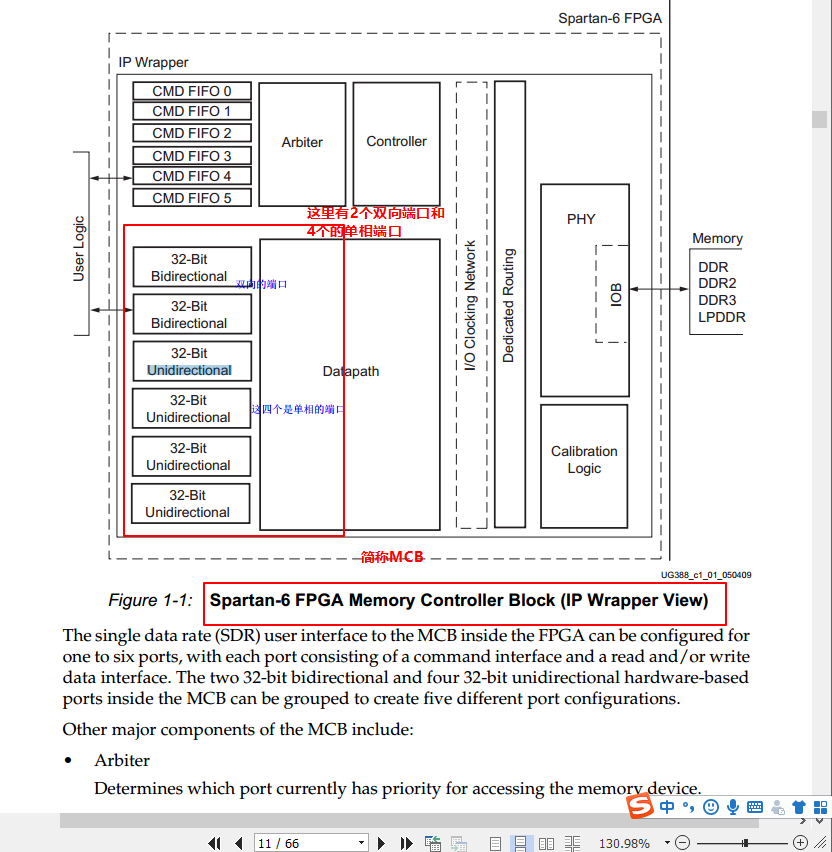

先打开MCB的用户手册

MCB的全称: Memory Controller Block

他有2个32bit双向的端口和4个32bit单相的端口组成。

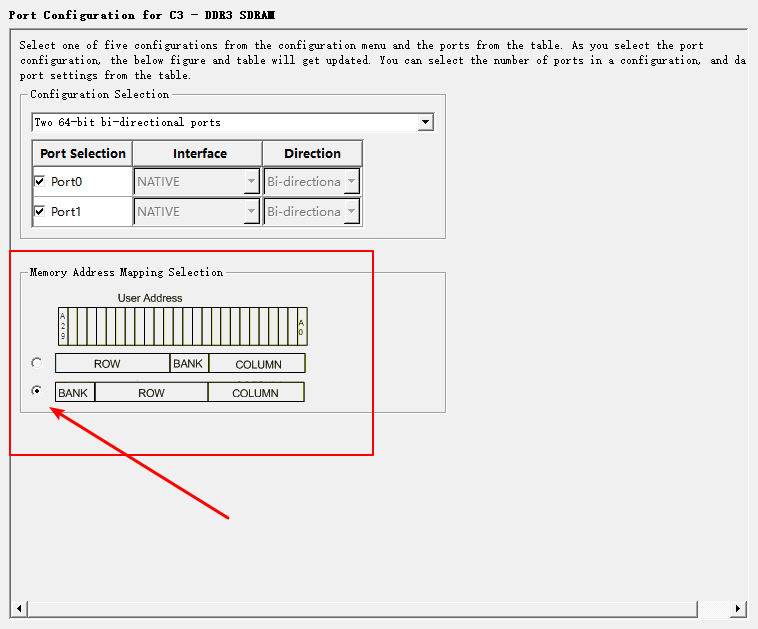

Memory Address mapping selection这里我们选择

bank row col这种形式。

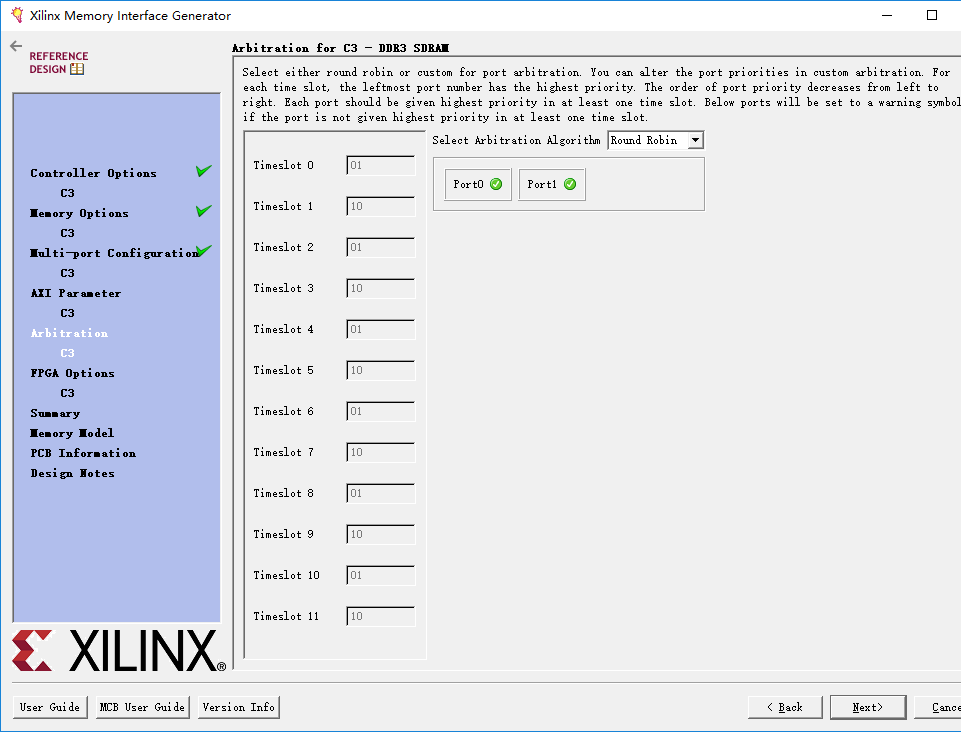

8.优先级的设置

因为我们前面有设置到我们使用了两个64bit的端口,这两个端口是可以同时进行读写的,但是DDR3芯片,一个时间只能读或者写,所以这里就需要有个优先级。

我们这里保持默认,直接点击next.

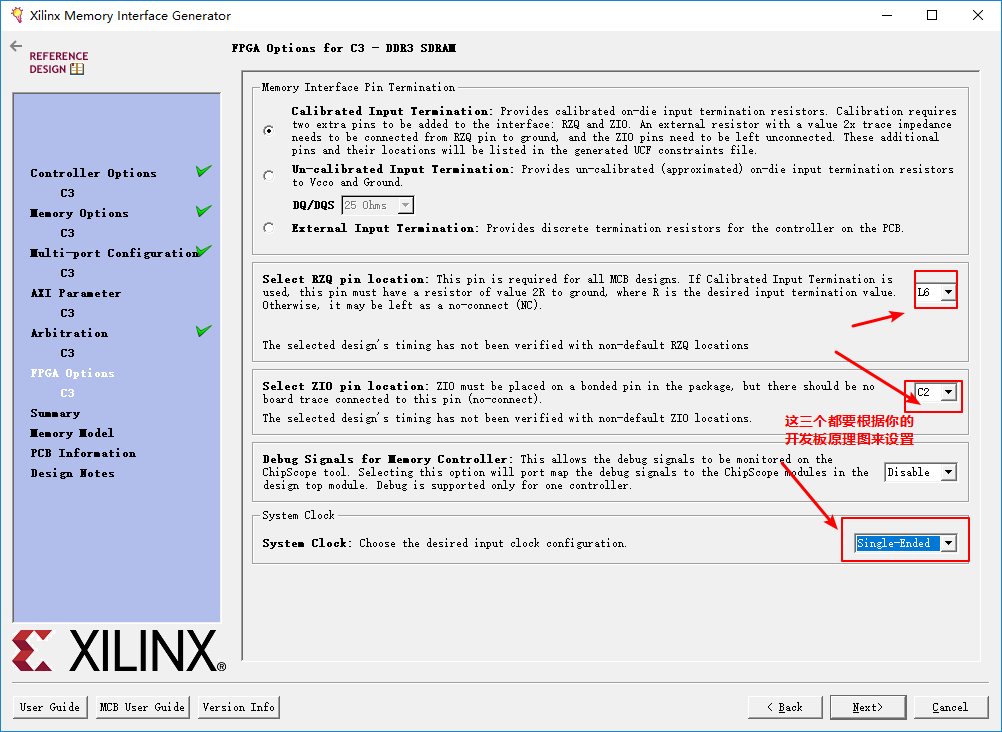

9.

这块开发板的时钟采用的是单端的时钟

所以这里设置成single-ended

RZQ和ZIO引脚时钟,看原理图中,有带下拉电阻的引脚一般是为RZQ和ZIO

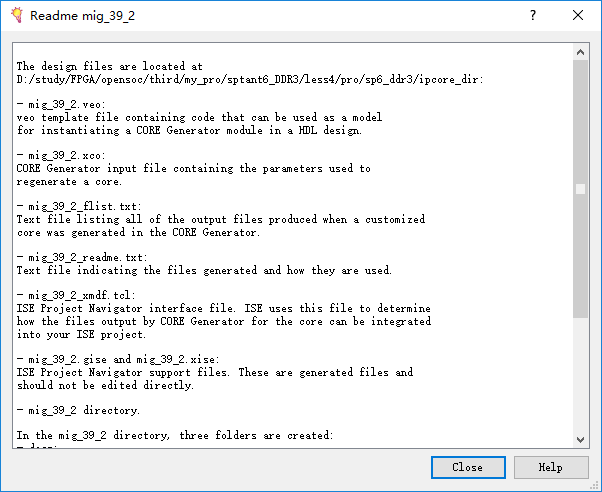

10.之后的设置一路next就行。最后生成的信息

点击close.

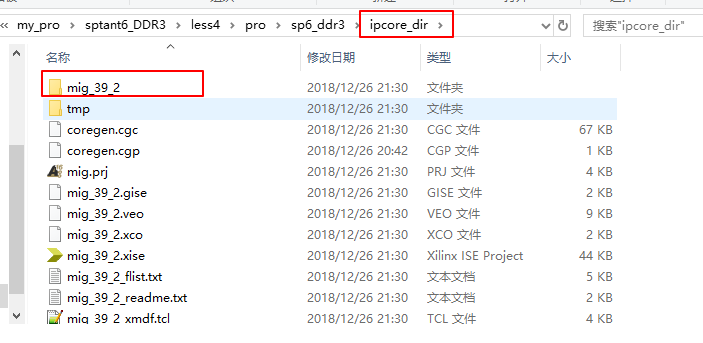

生成后再工程目录下的IP核目录下面

有mig_39_2这个文件夹。