DDR是个好东西啊,基本上每家公司都会用到这个,首先还是先来给出XIlinx官网手册ug586_7Series_MIS地址吧:

1.https://china.xilinx.com/support/documentation/ip_documentation/mig_7series/v4_2/ug586_7Series_MIS.pdf

官方手册内容好多,看起来实在是有点费时间,在上网上又搜集了其它的一些资料:

2.https://blog.csdn.net/Gdadiao123/article/details/79253626(Xilinx 7系列例化MIG IP core DDR3读写)

感觉这篇文章提炼的重点还不错,里面提到的链接在这里再链接一次,直接点进去就能看,方便一些

3.https://wenku.baidu.com/view/63e8c92d195f312b3069a5ea.html(基于Xilinx MIS IP的DDR3读写User Interface解析)

4.http://blog.chinaaet.com/chinaaetwoaini/p/5100050615(转 AC701的DDR3测试读写(2))

5.https://blog.csdn.net/qq_20091945/article/details/53862467)(Win8/Win8.1/Win10下Vivado例化MIG报错的解决办法)

6.https://blog.csdn.net/qq_20091945/article/details/53940712(在Nexys4 DDR上实现的DDR2读写例程)

7.https://blog.csdn.net/zhipao6108/article/details/81570681(Xilinx DDR IP详解与时序分析)

8.https://blog.csdn.net/DdiIcey/article/details/78517125(

Xilinx基于MIG IP Core的DDR3设计【1】 – 建立仿真平台)

9.https://blog.csdn.net/u012923751/article/details/83241169(转载xilinx-DDR3 ip 核:DDR3调试总结)

下面这个链接是下载的

https://download.csdn.net/download/zhiyoushiwo/10820592

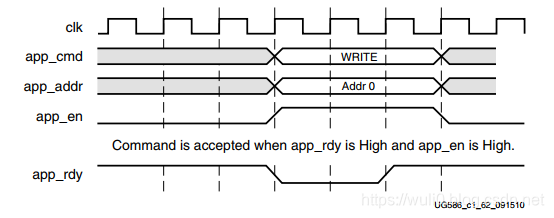

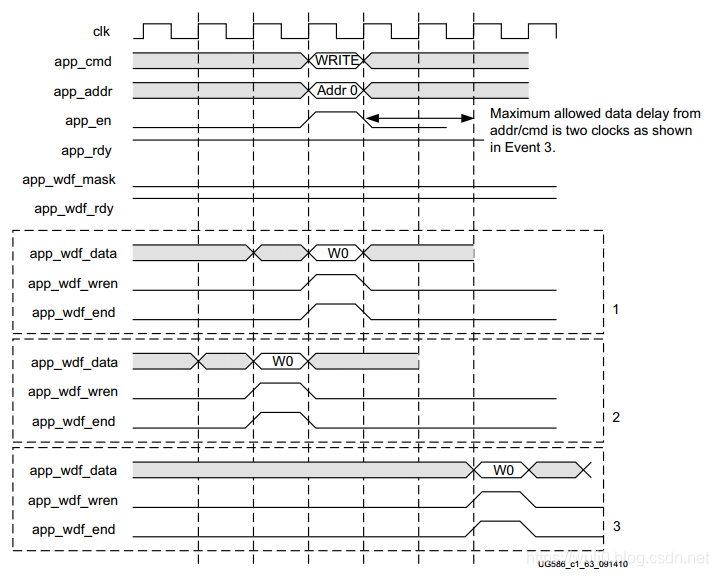

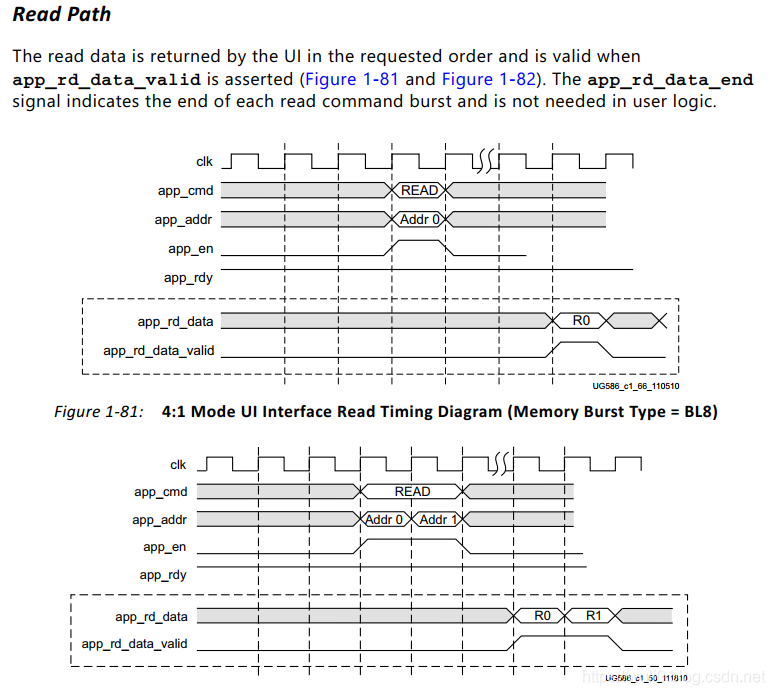

看完上面的资料,基本上都描述的都差不多,就是描述地址域和数据域的时序关系,下面我要讲的就是我的设计思路,关于时序我不多说,上面的链接里面都有。

一般来讲我们都是需要将存储的IP核封装成项目中需要的时序接口,可以是FIFO接口,视频时序接口或者其它总线接口等等,7Series_MIS读写是共用一个地址总线,不能同时进行读写操作。

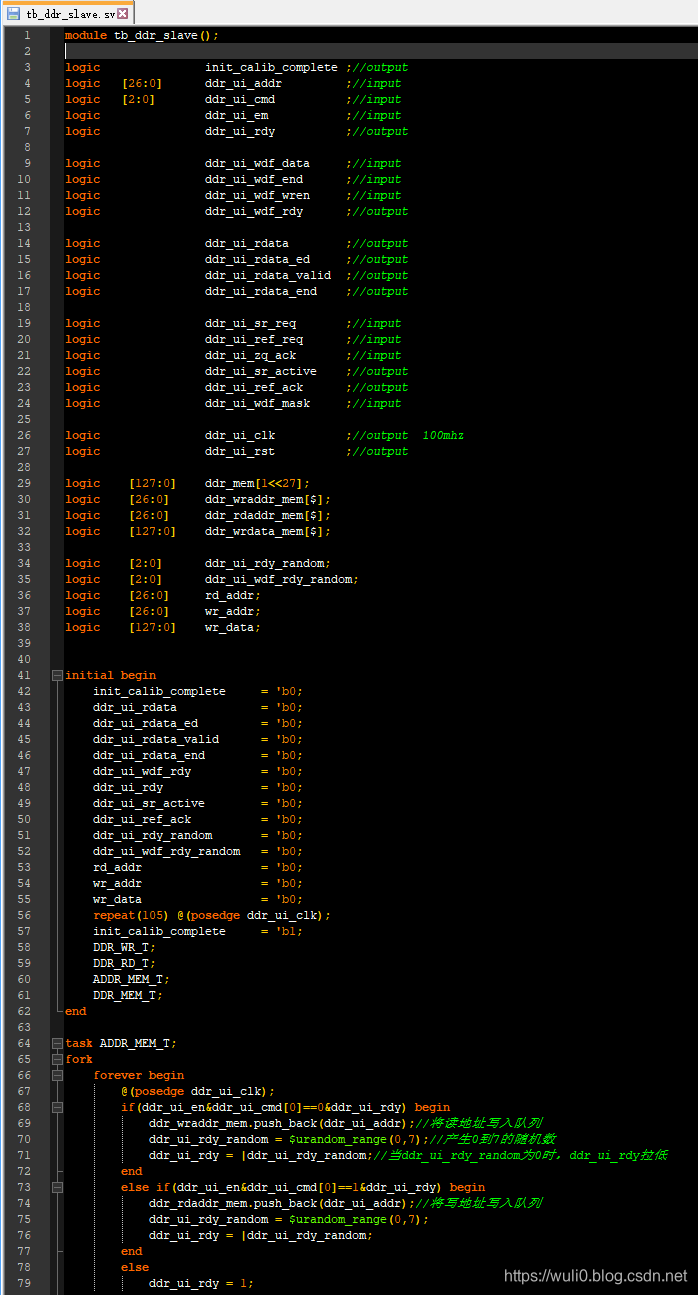

但是项目中我们通常有可能需要在读数据的时候也在写数据,另外一个DDR可能不止缓存一种数据,也有可能缓存PCIE过来的数据、缓存网口过来的数据、缓存本地摄像头的数据,这样就有三路数据的读写。此时我们需要将ddr内部的地址进行分区存放和读取,这就牵扯到ddr地址的管理,读写操作的管理。需要我们在封装的驱动里面进行读写操作控制和数据预读取,我自己的操作方法是将每一路的读写操作指令写入指令fifo,按先后顺序读写DDR,存入后级的异步fifo,此部分代码还是有点复杂的,需要自己去慢慢调试,这部分代码最好用上状态机,这样思路清晰,不会容易出错,我对我自己的源码在这里不太方便公开。但是我自己写的ddr仿真模型可以拿出来给大家看看。

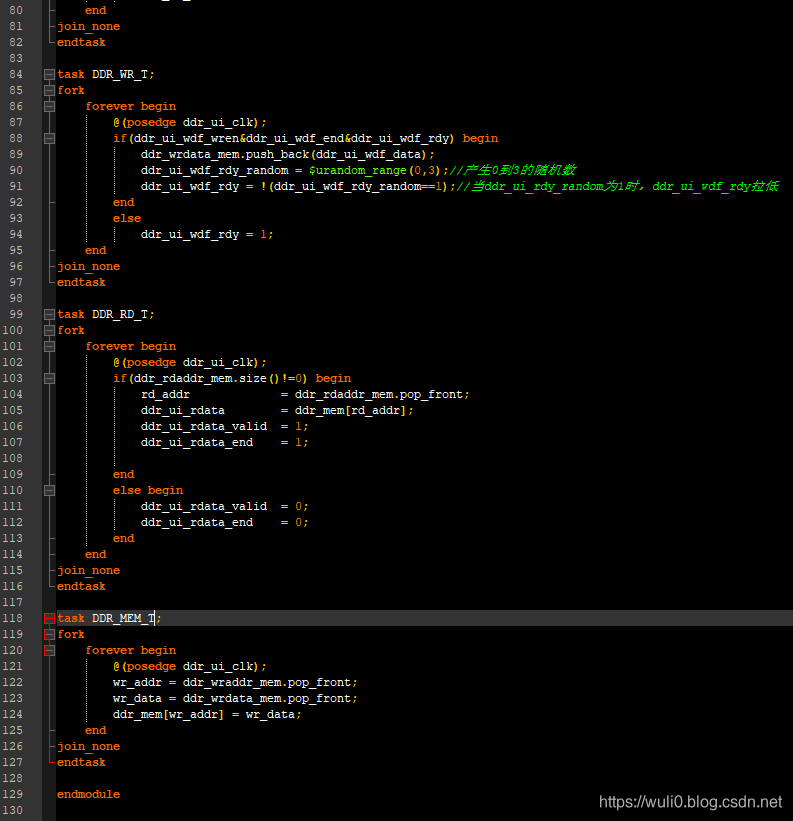

对于7Series_MIS IP的仿真模型,官方生成的Example里面也有,通过查看官方的仿真tcl脚本,我们也可以用他们的模型放在自己的工程系统中仿真,但是用上官方的模型仿真起来速度太慢啦,于是我就自己写了一个简单的,如下图,大家可以自行参考,语言是System Verilog,只用了里面的的一些简单的语法,这个只是一个slave文件,需要放到testbench工程中搭配中一起用,端口处没有input和output,是因为我都是在顶层通过force对这面的信号进行连线。force这条语句我一直都觉得很好用,哈哈,我觉得你们感兴趣的化也可以去研究一下force。

在写数据操作的时候,一般建议app_rdy和app_wdf_rdy都为高电平的时候 送数据和地址,驱动内部用的fifo建议使用First Word FIFO这样时序简单一点。还需要注意的是app_addr低3bit是0啊,最好写成add_addr={wr_rd_addr,3’b0};这样就不会容易搞错了。

写的不是很多,也没有分享太多东西,这个主要还是得靠自己去研究,网上得资料都只能说算是参考,搞明白了就简单,没搞明白就是大脑一片空白,哈哈

声明:所有文章属于个人在工作中所记下和搜集的笔记,不得转载