声明

依公开知识及经验整理,如有误请留言。

个人辛苦整理,付费内容,禁止转载。

所在专栏 《深入理解SSD:固态存储特性与实践》

内容摘要

RAM 概念

RAM 全称为 Random Access Memory(随机存储器),是计算机中一种临时存储设备,用于临时存储计算机正在运行的程序和数据。 RAM 是一种易失性存储器,也就是说,当计算机关闭或断电时,存储在 RAM 中的所有数据都会被清除。 RAM 的读写速度非常快,大大提高了计算机的运行速度。 RAM 通常被认为是计算机的短期记忆,与计算机的硬盘等长期存储设备相对应。计算机的性能和 RAM 的大小和速度密切相关。

RAM(随机存储器)种类包括

-

SRAM(静态随机存储器):能够快速读取,但相对较昂贵,通常用于高速缓存。

-

DRAM(动态随机存储器):速度较慢,但是相对便宜,适合用于主存储器。

-

SDRAM(同步动态随机存储器):与计算机主板同步工作,可以提高数据传输速度。

-

DDR SDRAM(双倍数据率同步动态随机存储器):比SDRAM更快,可以同时读取和写入数据。

-

DDR2 SDRAM(双倍数据率二代同步动态随机存储器):比DDR SDRAM更快,功耗更低。

-

DDR3 SDRAM(双倍数据率三代同步动态随机存储器):比DDR2 SDRAM更快,功耗更低。

-

DDR4 SDRAM(双倍数据率四代同步动态随机存储器):比DDR3 SDRAM更快,功耗更低,容量更大。

RAM 的位宽是多少

RAM 位宽是指 RAM 内存数据总线的宽度,也就是指 RAM 内存单元与外部总线之间的数据传输宽度。它决定了 RAM 内存可以同时传输多少位数据,也就决定了 RAM 内存的数据传输速度和最大传输容量。一般来说,RAM 位宽越宽,其传输速度越快,其最大传输容量也越大。常见的 RAM 位宽有 8 位、16 位、32 位和 64 位等。

| RAM | 位宽 |

| DDR4 SDRAM | 64位 |

SRAM

SRAM(Static Random Access Memory)全称为静态随机存储器,是一种存储器件,可以存储数字数据和指令,被广泛应用于微处理器、数字信号处理器、网络路由器等各种计算机和电子设备中。

SRAM 的结构

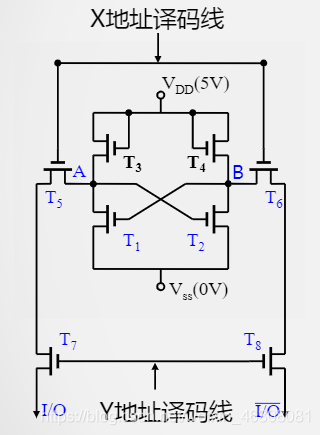

图片来源:静态存储器(SRAM)工作原理_sram工作原理_比奇堡咻飞兜的博客-CSDN博客

SRAM内部结构具有以下几个主要部分:

-

存储单元:SRAM 的存储单元包括一个存储器单元和一个使能电路,用于控制访问该存储单元的状态。一个存储单元通常由 6 个晶体管组成,其中 4 个用于存储数据(两个用于存储每个位),另外 2 个用于控制读写操作。

-

地址译码器:SRAM 的地址译码器用于将 CPU 发出的地址信号转化为存储器单元的地址,使得读写命令能够精确地访问所需的存储单元。

-

数据输入输出线:SRAM 的数据输入输出线用于将数据输入到存储单元中,或从存储单元中读出数据,并将数据传送给 CPU。

-

内部控制逻辑:SRAM 的内部控制逻辑用于控制存储器读写操作的时序和时钟,以及对存储器单元的写入和读出等操作。

SRAM的基本原理

说明:

T1、T2为工作管,用来保存\存储数据

T3、T4为负载管,用于为T1、T2提供电荷

T5、T6、T7、T8为门控管,用于控制开关

SRAM是一种基于触发器的存储器,它使用6个晶体管构成一个存储单元。每个存储单元都有一个位线,用于向存储单元写入数据或读取数据。当位线被激活时,就会将数据写入存储单元或从存储单元读取数据。

SRAM的存储单元由两个逻辑门和两个电容器组成。其中一个门被称为存储门(存储器单元),另一个门被称为传递门。当存储门的控制线被激活时,传递门被打开,将存储器单元的值传递到位线上。如果控制线不被激活,则传递门关闭,存储器单元的值不会被传递到位线上。

SRAM的工作原理

SRAM的工作原理基于电容器和晶体管的特性。当电容器充电时,它可以存储电荷,而晶体管可以控制电流的流动。在SRAM中,晶体管控制电荷的流动,从而实现数据存储和读取。

SRAM的工作主要分为读取和写入两个步骤。

读操作

在读取数据时,CPU将地址线上的地址送到SRAM中,SRAM会将该地址映射到存储芯片中对应的存储单元。然后,SRAM将存储单元中的数据传递到位线上,CPU通过位线读取数据。

module sram_read (

input [7:0] addr, // 地址输入

output [7:0] data // 数据输出

);

reg [7:0] mem [0:255]; // 建立一个8位宽、256个单元的SRAM

assign data = mem[addr]; // 将地址输入作为内存索引,将数据从SRAM中读出

endmodule

首先定义了一个8位宽、256个单元的SRAM,然后通过一个地址输入端口来确定需要读取哪个单元的数据。Verilog中的索引方式是使用方括号([])将索引值包含在信号名之后,例如“mem[addr]”将使用地址输入值作为索引来获取SRAM中的数据。最后,将读取到的数据输出到数据输出端口。

module sram_write(

input [7:0] data_in, // 要写入的数据

input [9:0] address, // 写入地址

input write_en, // 写入使能信号

output reg [7:0] sram_out // SRAM 输出数据

);

reg [7:0] sram [1023:0]; // 1K x 8 bits 的 SRAM

// 用 address 选择将数据写入 SRAM 数组中

always @(posedge clk) if (write_en) sram[address] <= data_in;

// 从 SRAM 数组中提取数据

always @(address or sram) sram_out <= sram[address];

endmodule说明:

- sram 数组是由 1024 个 8 位元素组成的 SRAM。

- 当写入使能信号 write_en 为高电平时,在时钟上升沿时,将 data_in 写入到 sram 数组中的给定地址。

- 当时钟信号 clk 上升沿发生或 sram 数组或地址 address 发生变化时,sram_out 从 sram 数组中选择所需的数据并输出。

在写入数据时,CPU将地址线上的地址和要写入的数据送到SRAM中,SRAM将地址映射到存储芯片中对应的存储单元。然后,SRAM将数据写入存储单元中。

SRAM的特点

-

速度快:相对于DRAM,SRAM的速度更快,因为它不需要定期刷新存储器单元。

-

功耗低:由于SRAM的速度较快,需要的工作时间较短,因此SRAM的功耗相对较低。

-

寿命长:SRAM的寿命长,因为它不需要定期刷新存储器单元。

-

抗干扰能力强:由于SRAM使用静态存储单元,所以它的抗干扰能力较强。

-

容量小:由于SRAM使用的存储单元比DRAM更复杂,因此它的容量相对较小,而成本较高。

SRAM的应用

由于SRAM具有速度快、功耗低、寿命长和抗干扰能力强等优点,它被广泛应用于高速缓存、存储器控制器、DSP芯片、嵌入式系统、交换机等高速数据交换设备中。

SRAM 位宽

SRAM(静态随机存储器)的位宽通常是8位、16位、32位、64位等。

SRAM 频率

SRAM的频率取决于系统总线的频率和SRAM的规格和性能。

SRAM 延迟

SRAM延迟大小指的是存储器单元从访问请求发出到响应产生所需的时间。SRAM(Static Random Access Memory)延迟大小通常在几纳秒(ns)到数十纳秒之间,这与DRAM(Dynamic Random Access Memory)相比具有更快的访问速度和更高的带宽。SRAM的延迟大小取决于许多因素,如技术节点、电源电压、温度等。SRAM延迟大小的减少可以通过优化电路设计和工艺改进来实现。

SRAM 的延时取决于多个因素,包括:

-

存取时间:这是从发出存取请求到读或写操作完成所需的时间。速度更快的 SRAM 芯片通常具有更短的存取时间。

-

延迟线:SRAM 的延迟线是数据从输入写入 SRAM 中之前的时间延迟,或者是从 SRAM 输出到系统之前的时间延迟。这个延迟可以受到设计、工艺和电压等因素的影响。

-

延迟变化:SRAM 延迟可能会随着时间、温度和电压的变化而发生变化。

总线访问 SRAM

AHB(Advanced High-performance Bus)由ARM(Advanced RISC Machines)公司开发,旨在在SoC(System-on-Chip)和嵌入式系统中使用。AHB总线主要用于连接处理器、存储器、外设控制器等内部模块,是现代嵌入式系统中最常用的系统总线之一。在ARM Cortex-M系列的微控制器中,AHB总线是连接处理器、内存和外设控制器的核心总线。

AHB-SRAM介绍

SRAM在整个系统中作为缓存,SRAM控制器实现SRAM存储器与AHB总线的数据信息交换,其一端连接AHB总线,另一端连接SRAM(8k*8两个bank),将AHB总线上的读写操作转换成标准的SRAM读写操作(将控制信号和地址信号及数据信号进行转化,并将其发送给相应的SRAM存储器,进行实际的数据存取)。

AHB-SRAM通过使用高速缓存技术,将常用的数据存储在高速缓存中,从而减少CPU访问SRAM的次数,提高SRAM读取效率和速度。

AHB-SRAM读取SRAM的步骤如下:

-

CPU将读取请求发送到AHB总线。

-

AHB总线控制器将请求转发到AHB-SRAM接口。

-

AHB-SRAM接口将请求转换成SRAM访问请求,并将其发送到SRAM。

-

SRAM将请求的数据返回给AHB-SRAM接口。

-

AHB-SRAM接口将返回的数据存储在高速缓存中,并将其返回到AHB总线控制器。

-

AHB总线控制器将数据传输到CPU中

AHB-SRAM缓存大小是可变的,通常是根据具体的应用需求来决定的。

AHB-SRAM 读 SRAM 实现

// @Verilog

module ahb_sram_read (

input ahb_hclk,

input ahb_hsel,

input ahb_htrans,

input [31:0] ahb_haddr,

output [31:0]ahb_hdata

);

reg [31:0] sram[0:1023]; // SRAM 数据存储

always @(posedge ahb_hclk) begin

if (ahb_hsel && ahb_htrans == 2'b10) begin // 读数据操作

ahb_hdata <= sram[ahb_haddr[9:0]];

end

end

endmodule

sram数组存储 SRAM 中的数据。

always块监测ahb_hclk信号上升沿并执行读操作。当ahb_hsel信号为高电平且ahb_htrans信号为2'b10(表示读操作)时,将从ahb_haddr指定的地址读取 SRAM 中的数据,并输出到ahb_hdata数据总线上。

AHB-SRAM 写 SRAM 实现

module ahb_sram_write(

input HCLK, // 常规高速系统时钟

input HRESETn, // 异步低电平重置信号

input HSELx, // 模块选择信号

input [31:0] HADDRx, // 地址线

input HWDATAx, // 写入数据线

input HWRITE, // 写使能信号

input HSIZE, // 大小码

input HBURST, // 突发传输信号

input HM1x, // 突发传输信号

input HPROTx, // 保护模式信号

output HRDY, // 读写忙信号

output HRESPx, // 响应信息

output [31:0] HRDATAx // 读取数据线

);

// SRAM 内存模块

reg [31:0] sram[0:1023];

// 记录当前访问的地址

reg [31:0] current_addr;

// 解码突发传输信息

reg [1:0] burst_count;

wire [31:0] burst_start_addr;

reg burst_start;

// 记录当前传输的数据

reg [31:0] current_data;

reg data_changed;

// 处理突发传输信息

always @(*) begin

if (HBURST && HM1x && HSIZE == 2'b11) begin

burst_count = HADDRx[1:0];

burst_start_addr = {HADDRx[31:2], 2'b00};

burst_start = 1'b1;

end else begin

burst_start = 1'b0;

end

end

// 处理写入操作

always @(posedge HCLK) begin

// 每次传输完成后,将地址增加到下一个字

if (HRDY && !HWRITE && !burst_start) begin

current_addr <= current_addr + 4'b1000;

end

// 处理突发传输写入

if (burst_start) begin

for (int j = 0; j < 4; j = j + 1) begin

sram[burst_start_addr + j] <= HWDATAx[31-j*8:24-j*8];

end

burst_start_addr <= burst_start_addr + 4;

burst_count <= burst_count - 1;

if (burst_count == 0) begin

burst_start <= 1'b0;

end

data_changed <= 1'b1;

end else begin

if (!HWRITE) begin

HRDATAx <= sram[current_addr];

end else begin

sram[current_addr] <= HWDATAx;

data_changed <= 1'b1;

end

end

end

// 处理响应信息

always @(*) begin

if (HWRITE && data_changed) begin

HRESPx <= 2'b00; // 正确的写响应

HRDY <= 1'b0;

end else if (!HWRITE) begin

HRESPx <= 2'b00; // 正确的读响应

HRDY <= 1'b1;

end else begin

HRESPx <= 2'b10; // 错误的写响应

HRDY <= 1'b0;

end

end

endmodule

DRAM

// TODO

DDR4 SDRAM

DDR4 SDRAM(Double Data Rate 4 Synchronous Dynamic Random Access Memory)是第四代同步动态随机存储器技术,采用64位宽总线和点对点拓扑结构传输,其主频最高可达3200MHz。在相同时钟速度下,DDR4内存的数据传输速度比DDR3内存更快。

DDR4内存在结构和工作原理上与DDR3内存类似,但是DDR4内存的最小电压降至1.2V,相比DDR3内存的1.5V更为低能耗。此外,DDR4内存还具有更高的时钟频率,可实现更高的数据传输速率和更低的延迟时间,使得它在数据处理和运算任务中表现出更好的性能。

除了性能提升,DDR4内存还具有更高的可靠性和可用性。DDR4采用了一种新的错误检测和纠错机制,称为CRC(Cyclic Redundancy Check),可提高数据传输的稳定性和可靠性。此外,DDR4还支持更高的容量和更低的功耗,使得它成为高端计算机和服务器系统的首选内存技术。

DDR4 SDRAM 特性

DDR4 SDRAM比之前的DDR3 SDRAM在带宽、时钟频率、功耗和容量等方面有了显著的改进。下面是DDR4 SDRAM的详细特性:

-

速度更快:DDR4 SDRAM的时钟频率比DDR3 SDRAM高,目前最高能达到3200 MHz,传输速率最高达到25.6 GB/s,相比之前的DDR3 SDRAM有着明显的提升。

-

更高的容量:DDR4 SDRAM的每个芯片的容量可以更高,目前市面上有16 GB和32 GB的DDR4 SDRAM芯片,使得整个系统的内存容量变得更大。

-

更低的电压:DDR4 SDRAM的工作电压比DDR3 SDRAM低,频率较低的DDR4 SDRAM工作电压仅为1.2 V,比DDR3 SDRAM低20%。

-

更高的带宽:DDR4 SDRAM从数据读取到输出的延迟时间缩短到20纳秒,比DDR3 SDRAM的延迟时间缩短了33%。

-

更强的容错性:DDR4 SDRAM具有更好的容错性,能够更好地保护系统免受数据错误的影响。

DDR4 SDRAM 工作原理

DDR4 SDRAM通过电容来存储数据。当电容被充电时,表示存储的是二进制数字1;当电容被放电时,表示存储的是二进制数字0。内存单元组成一个字节,可以存储8位二进制数字。

内存的读写操作是基于时钟信号的。读操作发起时,内存控制器向内存发送读命令和地址信息,内存将数据返回给控制器。写操作发起时,内存控制器向内存发送写命令、地址信息和数据,内存将数据存储到指定的地址中。

DDR4 SDRAM 延迟

DDR4 SDRAM的延迟取决于其速度等级和时钟速度。DDR4 SDRAM的速度等级通常以“PC4-XXXX”形式表示,其中“XXXX”是时钟速度(以MHz为单位)。以下是一些常见的DDR4 SDRAM速度等级及其延迟:

- PC4-19200(2400 MHz):CAS延迟为17

- PC4-21300(2666 MHz):CAS延迟为19

- PC4-24000(3000 MHz):CAS延迟为15

- PC4-25600(3200 MHz):CAS延迟为16

DDR4 SDRAM的延迟通常在CL14至CL19之间,取决于具体型号和速度等级。 CL表示CAS延迟,CAS是内存开始接收到请求后所需的时钟周期数。因此,较低的CL值意味着更快的响应速度。