学习记录之用。

一、DDS概念

DDS(Direct Digital Frequency Synthesizer)直接数字频率合成器本文主要介绍如何调用Xilinx的DDS IP核生成某一频率的Sin和Cos信号。

二、频率选择

打开IP核配置,parameter Selection选择System Parameters,有两种选择,

选择System Parameters时,输出频率可以在IP核中直接输入。

选择Hardware Parameter时,可以在IP核中或者程序中输入频率控制字PINC来确定,

如图,

PINC选择的是 1101000110110111 = 53687

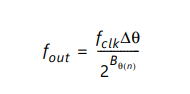

由手册公式,

f = (53687*100*10^6)/(2^16) = 81.91986 MHz

我们再看IP核的信息。

另外,我们也可以在程序中控制PINC。

top.v 如下。

`timescale 1ns / 1ps

module sin_20M(

input clk,

input config_tvalid,

input rst_n,

input [15:0] config_data_poff,config_data_pinc,

output [7:0] dds_data_sin_0,dds_data_cos_0

);

wire m_axis_data_tvalid;

wire m_axis_phase_tvalid;

wire [15:0]m_axis_phase_tdata;

dds_compiler_0 dds_init (

.aclk(clk), // input wire aclk

.s_axis_config_tvalid(config_tvalid), // input wire s_axis_config_tvalid

.s_axis_config_tdata({16'd0,config_data_pinc}), // input wire [31 : 0] s_axis_config_tdata

.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid

.m_axis_data_tdata({ dds_data_sin_0,dds_data_cos_0}), // output wire [15 : 0] m_axis_data_tdata

.m_axis_phase_tvalid(m_axis_phase_tvalid), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata(m_axis_phase_tdata) // output wire [15 : 0] m_axis_phase_tdata

);

endmodule

tb文件如下。

`timescale 1ns / 1ps

//

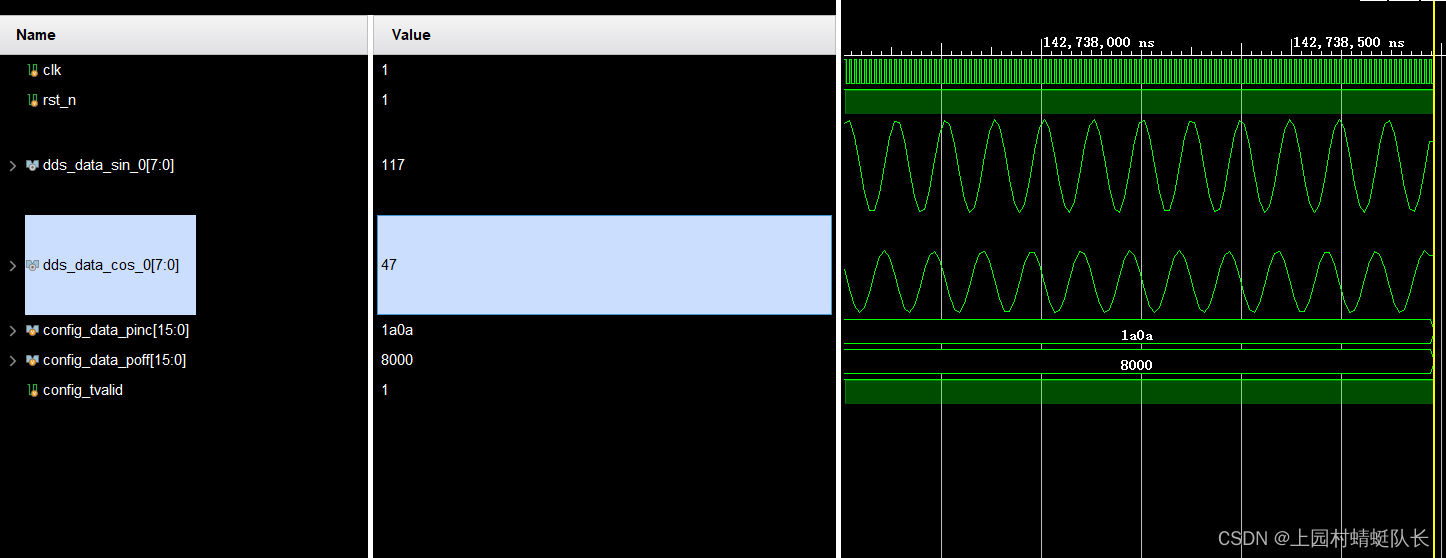

// 该tb文件中直接输入控制字 66 ----6666

// f=(PINC*fclk)/(2^phase width)=6666乘100000000/2的16次方=10.17MHz

//

module sintb(

);

reg clk;

always #5 clk<=~clk;

reg rst_n;

wire [7:0] dds_data_sin_0,dds_data_cos_0;

reg [15:0] config_data_pinc,config_data_poff;

reg config_tvalid;

sin_20M dds_001_Init

(

.clk(clk),

.rst_n(rst_n),

.dds_data_sin_0(dds_data_sin_0),

.dds_data_cos_0(dds_data_cos_0),

.config_data_poff(config_data_poff),

.config_data_pinc(config_data_pinc),

.config_tvalid(config_tvalid)

);

initial

begin

clk = 0;

rst_n = 1;

config_data_poff = 16'h4000;

config_data_pinc = 16'd66;

config_tvalid = 1'b1;

#100000

config_data_pinc = 16'd6666;

#100000

config_data_poff = 16'h8000;

$stop;

end

endmodule

输出的波形。