FPGA设计之vivado封装ip核

更多内容请关注微信公众号“FPGA科技室”

将已有的FPGA功能模块封装成IP,方便在Vivado中使用。

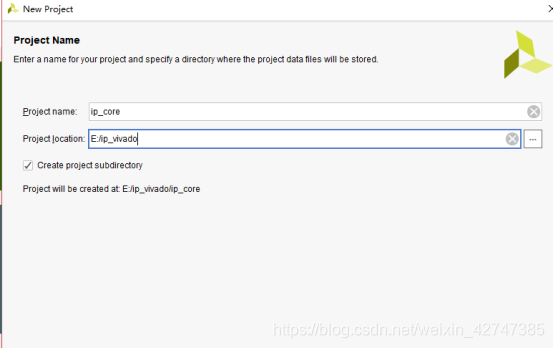

1.打开vivado,新建工程

2.一开始不添加任何程序模块代码文件

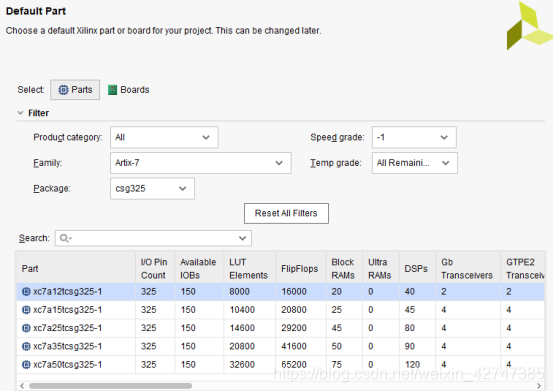

3.选择芯片型号(zynq7000)

二,IP封装流程

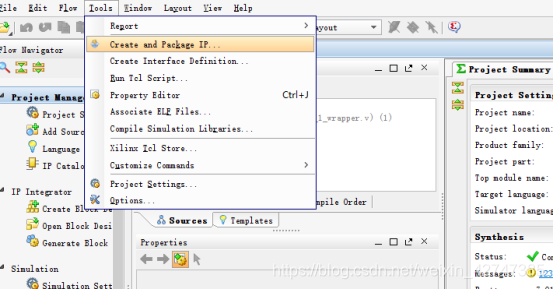

1.在Vivado工程中,选择菜单栏中的Tools,然后再下拉菜单中选择Creat and Package IP… 。如图所示

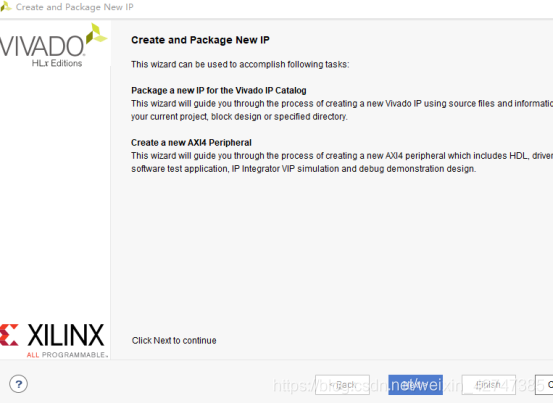

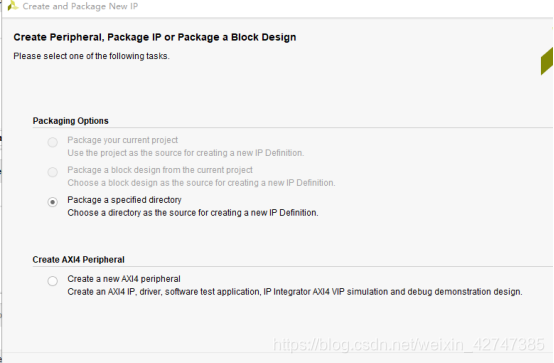

2.然后弹出向导,在本例中选择对特定文件夹内的代码进行封装

3.选择打包代码所在的文件夹

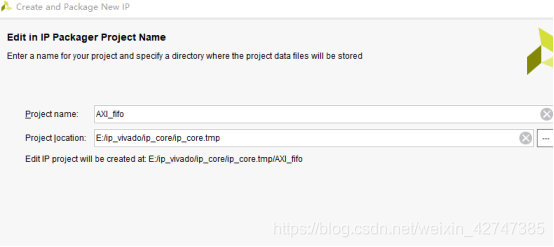

4.向导提示需要为IP工程制定一个名字和存储地址,如图所示,这个工程是临时的,IP封装完之后就会消失,再次编辑IP时才会再重新建立

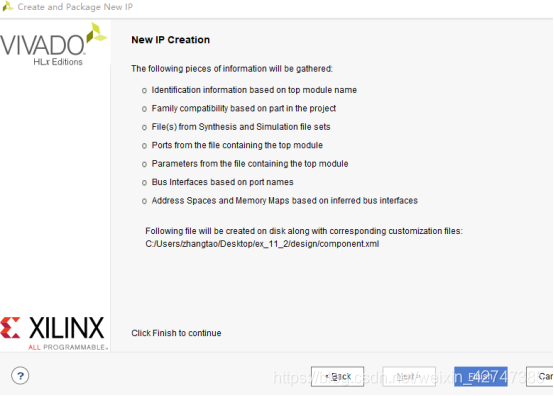

三,设置IP参数

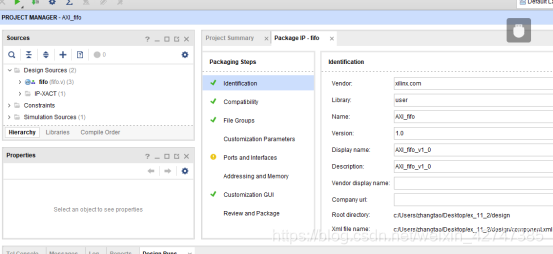

设置IP的信息,例如名称,版本,功能描述等,如图所示。

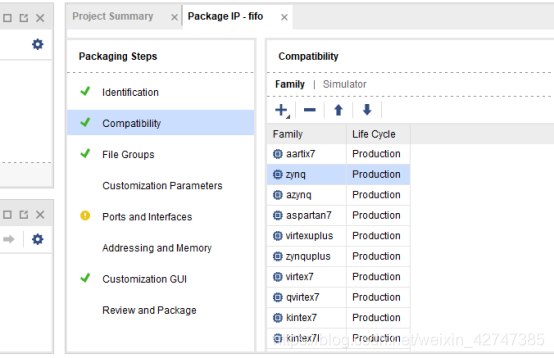

1.配置IP的兼容性,一般选择默认就可以了,如图所示

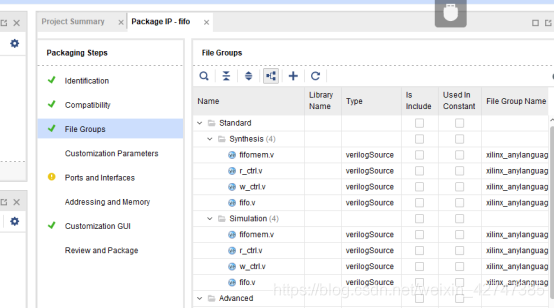

2.配置IP的文件系统,一般选择默认就可以了,如图所示

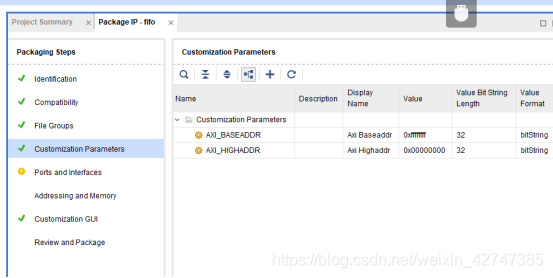

3.配置IP的参数,为了方便系统能识别该IP的AXI4-Lite总线,需要顶层文件中定义2个参数,分别是:AXI_BASEADDR和AXI_HIGHADDR,为32bit数据,用来作为该AXI4外设的地址空间,如图所示。

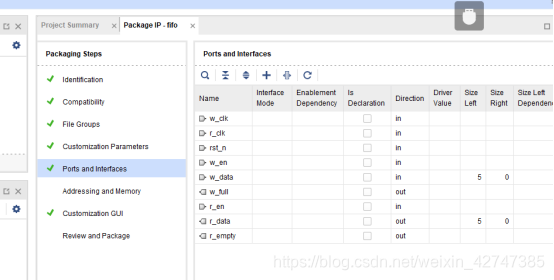

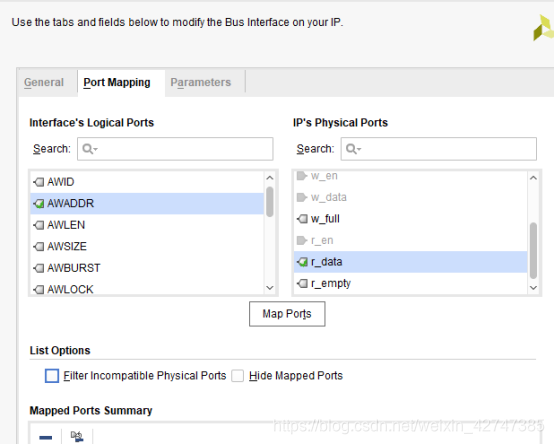

4.配置IP的端口,由于IP自动添加的总线端口一般都有问题,所有在配置前,需要将自动添加的总线端口去掉,然后再配置端口。

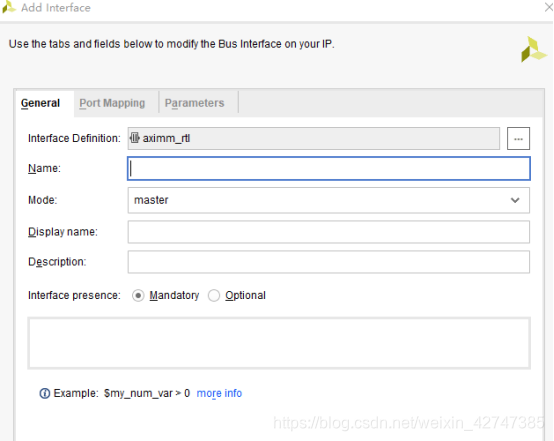

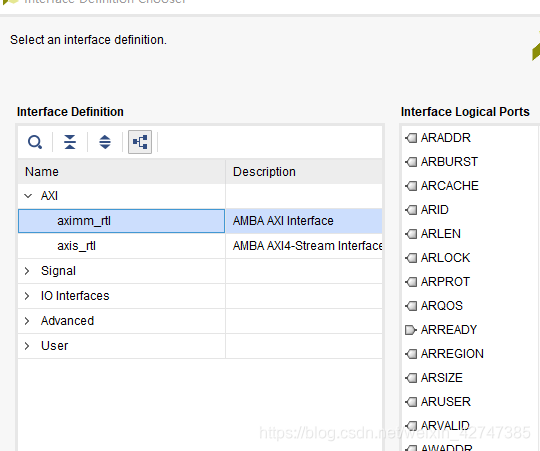

5.添加AXI总线

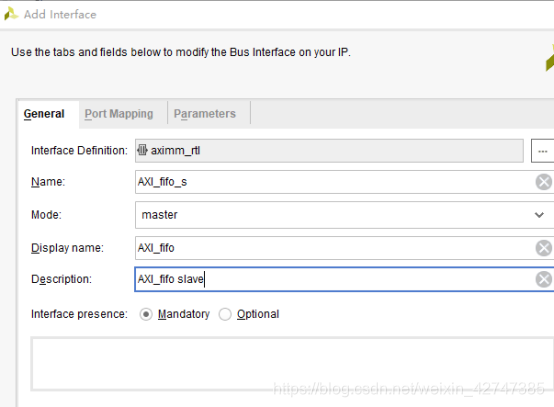

.6.配置AXI总线信息

7.配置IP的界面,可以根据自己的需要进行配置。如图所示

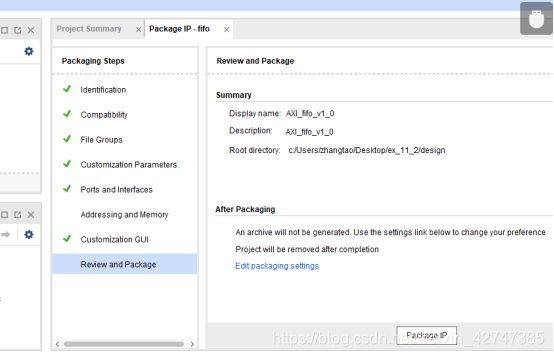

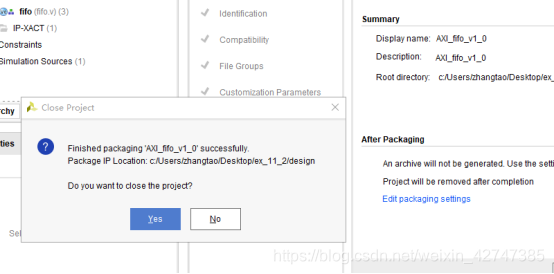

8.最后生成IP

三,测试

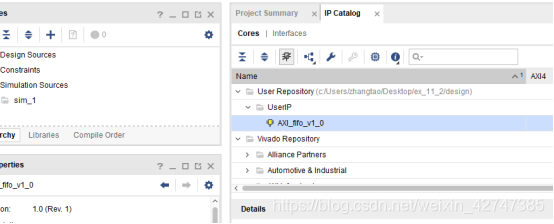

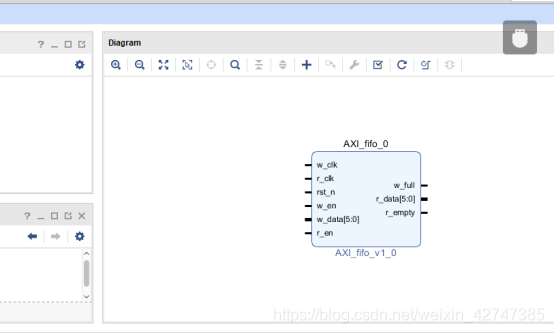

打开一个Vivado工程,进入IP Catalog,然后右键调出下拉菜单,即可显示之前编辑的ip

欢迎大家转发关注。。。