对于参考手册中经常出现的一些时序图,经常会让我摸不着头脑。比如对于Flash的时序图来说,要看懂的话,里面的每一个参数都得系统地学一遍,而且时序图中的一些符号也不太懂是什么意思。前一段时间调HyperRAM的时候,因为那些参数不懂,也无从用示波器对波形进行分析,软件上也不知道改哪里合适,最后都是乱试着调出来的。本篇文章以74HC595芯片为例,介绍时序图的一些基础概念。

1 常见时序图符号

首先来看一些时序图中会经常遇到的一些常用时序,需要注意的是时序图并没有一个统一的标准,所以下面列举的时序在不同的手册上可能会有略微的不同,但这些时序都是非常典型的。

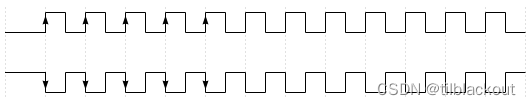

(1)方波

(2)上升/下降沿:箭头表示信号被触发

(3)斜坡(Ramping)

通常表示一个连续变化的信号,其数值随时间逐渐增加或减小。它被用来表示一种渐进的变化或模拟信号的过渡过程,或者用来清楚地表示两个信号是相反的。

(4)白色交叉

该信号是上图中的横向交叉。它表示对应信号的值在对其进行采样的时钟周期内可以是高值或低值,它的值由外部事件决定,数据在上升或下降沿采样。

(5)灰色交叉

在时序图中,可以有几个与灰色部分相关的定义,表示芯片不关心值是多少。比如I2C一次传输8位,但是只使用了MSB的3位,所以前3位是白色交叉,剩下5位是灰色交叉。还有一种情况,就是高阻态时也可以这样表示,参考下面74HC595的时序。

(6)省略

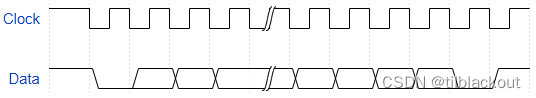

下面时序图中的小空隙表示有大量的数据正在传输,这里就不把每一个字节的时序图显示出来,而是省略掉。比如Flash一次可以传输256字节,就不太可能一个时序中给你展示256个字节的时序。

(7)位标记

位标记就是提供了详细的数据流指示,比如刚刚说的256字节,这里显示出时序图中的每一个字节。

(8)箭头:两个在时间上不对齐的两个点,如果用一个单向箭头相连(一般是弯的),就表示前面时序的产生会导致后面时序的产生。比如外部中断的一个上升沿,在若干指令周期后会导致中断标志位的时序从低变高,在时序图中就会有一个箭头从外部中断上升沿处指向中断标志位的上升沿处。

2 74HC595

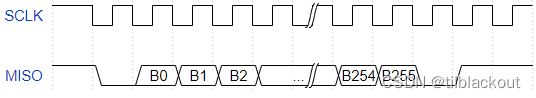

2.1 74HC595封装

这里以74HC595芯片为例,介绍时序图的相关概念。74HC595是一个8位串行输入、并行输出的移位缓存器。封装如下:

- QA~QH:并行数据输出

- SER:串行数据输入端

- QH’:串行数据输出端

- RCLK:输出存储器锁存时钟线

- SRCLK:数据输入时钟线

- SRCLR ‾ \overline{\text{SRCLR}} SRCLR:复位,高电平清空输出寄存器

- OE ‾ \overline{\text{OE}} OE:输出使能,低电平有效

2.2 时序图

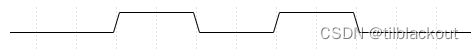

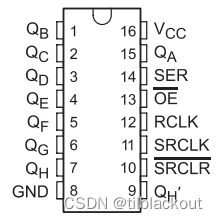

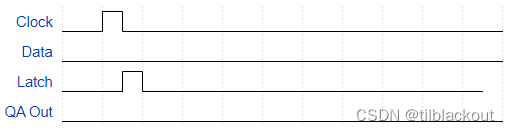

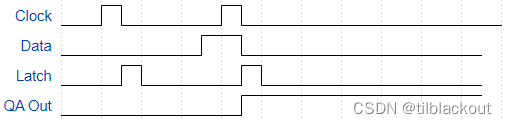

首先来看一下,当时钟脉冲信号来临的时候,输入数据线Data(SER)为0的情况:

可以看到锁存信号在时钟信号之后产生,Data一直为0,这里似乎什么事都没有做,所以我们继续延伸这个时序图,把Data拉高。

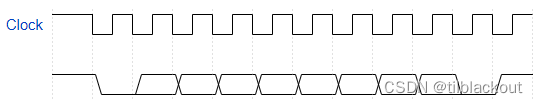

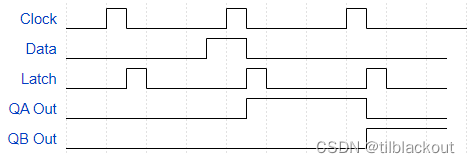

我们可以看到,在后面一段时序中,在CLOCK的上升沿,Data是高电平。然后在CLOCK和Data输出完后,锁存信号就改变了输出QA。

由于这是一个移位芯片,所以现在再把QB Out加到时序中看看:

在下一个时钟周期中,又输入了一个0,所以在锁存后,QA的输出被移位到QB,而QA保存本次的0。

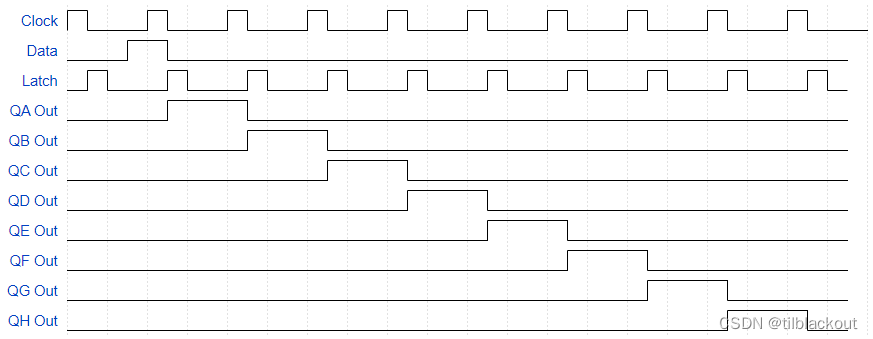

然后我们把剩余的输出引脚都补上,后面的时钟周期的Data都输出0:

可以看到第一个时钟周期输入的1,被一个个移位到

可以看到第一个时钟周期输入的1,被一个个移位到QH。

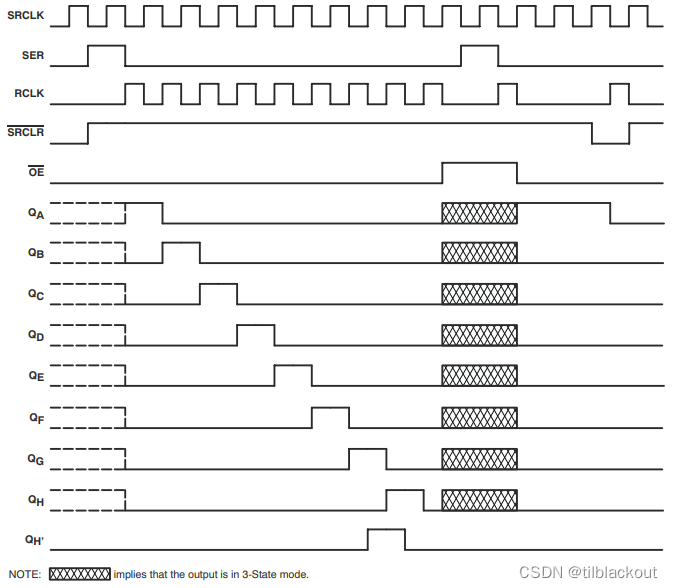

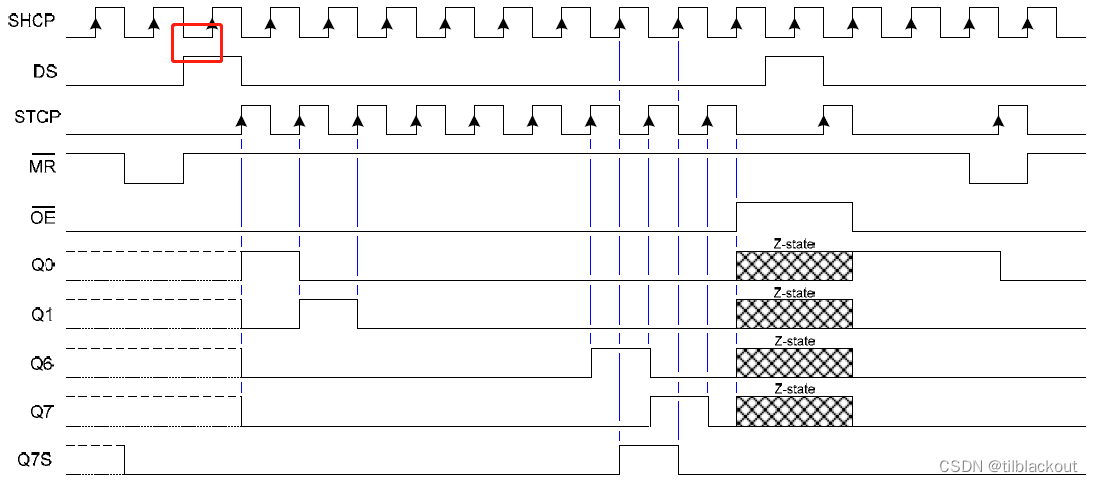

现在我们简单地知道了时序图的工作原理,我们就来看看真正手册中的时序图,以下是TI的SNx4HC595手册中给出的时序图:

图中列出了所有引脚的时序,其中QA~QH最开始的虚线表示当前输出为未知状态,因为此时 SRCLR ‾ \overline{\text{SRCLR}} SRCLR为低电平,之前的状态我们不知道,而当它被拉高时,寄存器内部的数据会被清零,并将输出引脚恢复到默认状态。最后还有一个网状的时序,这表示在输出不使能,即 OE ‾ \overline{\text{OE}} OE为1的时候,输出变为高阻抗的第三状态。

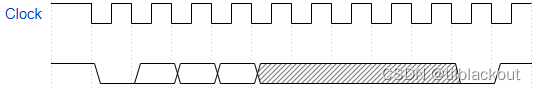

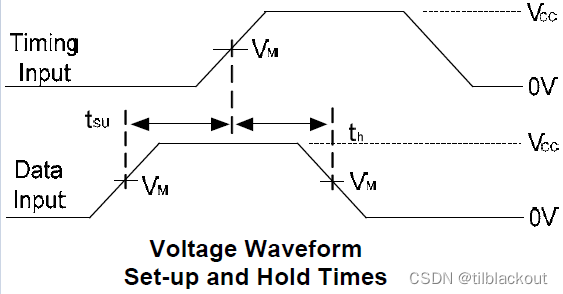

前面有说到,时序图没有一个标准,所以对于74HC595来说,不同厂商生产的74HC595的时序图都有一点不同,下面来看一下DIODE的74HC595的时序来分析一下数据的建立时间:

图中用红框标出的部分表示在时钟上升沿时,数据进行采样,此时DS应该保存稳定。那红框这一段时间(时钟的下降沿到上升沿),就被称为建立时间。在手册的后面有列出数据的建立和保持的时序详细的时序:

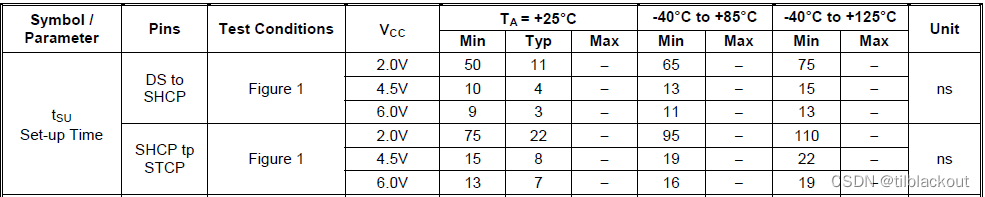

其中tsu为数据的建立时间,表示你要在时钟信号来临之前,需要保证数据线上的数据至少已经稳定tsu。同时在时钟变为高电平之后之后,至少还要将数据保持th,这样锁存器才能正常地保存数据。以建立时间tsu为例,如果我们没有满足这个时间要求,数据就可能出现异常,现在我们就需要来看看手册中tsu的要求:

这里看DS to SHCP(Data set to SHCP)这一行,在VCC为4.5V、温度为25℃的情况下,数据建立时间的典型值为4,它只是一个具有代表性的值,实际上我们设置不应该低于最小值10。

3 总结

这篇文章简单地介绍了一下时序图的基础知识,但如果我们现在打开一个芯片手册中的时序图,我们会发现还是读不懂,因为实际比这些复杂多了,我们就需要理解手册中每一个时序参数的含义,然后再来分析时序图。