目录

1.算法仿真效果

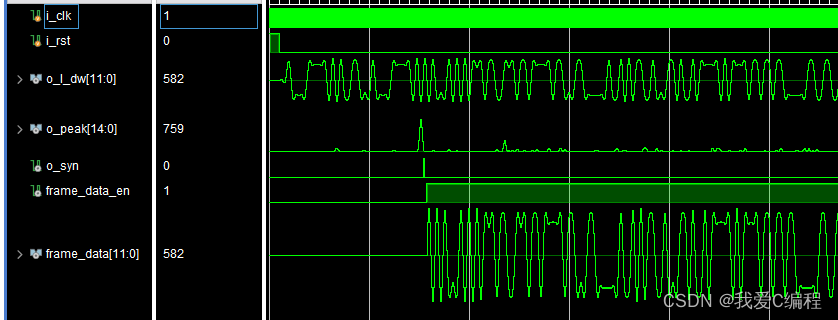

本系统进行了Vivado2019.2平台的开发,其中Vivado2019.2仿真结果如下:

2.算法涉及理论知识概要

在数据通信系统中,数据帧检测与帧同步是一项重要的任务,用于确定数据传输中数据帧的起始位置和边界,以正确解析数据。基于PN(Pseudo-Noise)序列的帧同步技术是一种常用的实现方法,它通过检测PN序列在接收信号中的匹配来实现帧同步。在本文中,我们将详细介绍基于PN序列的数据帧检测与帧同步Verilog实现,包括数学原理、实现过程、应用领域以及实现难点。

2.1 PN序列

PN序列是一种特殊的伪随机序列,具有良好的自相关性和互相关性。PN序列可以通过线性反馈移位寄存器(LFSR)或者Gold码生成器等方式产生。PN序列具有周期性,周期长度为$N$。在数据通信中,发送端和接收端预先约定好PN序列,并将其作为帧同步标记插入数据帧中。接收端利用接收信号与预知的PN序列进行匹配,以找到数据帧的起始位置。

2.2 互相关检测

在帧同步过程中,接收端需要通过互相关检测来确定接收信号中PN序列的匹配位置。互相关是一种常用的信号处理技术,用于衡量两个信号之间的相似程度。在基于PN序列的帧同步中,接收信号和预知的PN序列进行互相关运算,当两者匹配时,互相关峰值达到最大,从而可以确定数据帧的起始位置。

2.3 帧同步算法

基于PN序列的帧同步算法主要包括以下步骤:

接收信号采样:接收端对信号进行采样,得到数字信号序列。

PN序列生成:接收端使用与发送端相同的方法生成PN序列。

互相关运算:将接收信号与PN序列进行互相关运算,得到相关性序列。

峰值检测:检测相关性序列中的峰值,找到PN序列在接收信号中的匹配位置。

2.4 实现过程

Verilog实现的基于PN序列的数据帧检测与帧同步主要包括多个模块,其中顶层模块负责将输入信号传递给帧同步模块,并将帧同步模块的输出传递给输出模块。顶层模块主要包括以下步骤:

输入数据读取:从外部输入读取接收信号的样本数据。

帧同步模块调用:调用帧同步模块对接收信号进行帧同步检测。

输出数据传递:将帧同步模块的输出传递给输出模块,进行输出。

帧同步模块是实现基于PN序列的帧同步的核心模块,使用Verilog描述帧同步算法。帧同步模块主要包括以下步骤:

PN序列生成:使用LFSR或Gold码生成器产生预知的PN序列。

互相关运算:将接收信号与预知的PN序列进行互相关运算,得到相关性序列。

峰值检测:检测相关性序列中的峰值,找到PN序列在接收信号中的匹配位置。

输出模块

输出模块将帧同步模块的输出结果转换为帧同步的标志位,并输出结果。

2.5 应用领域

基于PN序列的数据帧检测与帧同步Verilog实现在数字通信系统中有广泛的应用。在数据传输中,帧同步是确保数据帧正确解析的关键步骤。基于PN序列的帧同步技术可以应用于无线通信、有线通信、卫星通信、雷达系统等各种通信和信号处理系统。

2.6 实现难点

基于PN序列的数据帧检测与帧同步Verilog实现面临以下几个主要难点:

2.6.1 PN序列生成

实现帧同步模块需要能够准确生成与发送端相同的PN序列。PN序列的生成算法是帧同步实现的关键,需要确保生成的PN序列在时间和频率上与预知的PN序列一致。

2.6.2 互相关运算

在帧同步模块中,互相关运算是一个复杂的计算过程,需要高效的算法和数据结构来实现。互相关运算的正确性和效率对于帧同步的准确性和性能至关重要。

2.6.3 峰值检测

峰值检测是帧同步过程中的关键步骤,需要准确找到相关性序列中的峰值。峰值检测算法需要兼顾灵敏度和鲁棒性,以适应不同信道条件和噪声干扰。

基于PN序列的数据帧检测与帧同步Verilog实现是一种重要的数据通信技术,在数字通信系统中有广泛的应用。通过理解数学原理、实现过程、应用领域以及实现难点,我们可以更好地掌握帧同步算法的本质和实现方法,并在Verilog语言的FPGA平台上高效地实现数据帧检测与帧同步。帧同步技术的发展将进一步推动数字通信系统的性能提升,为未来的通信发展做出贡献。

3.Verilog核心程序

module PN_1_sycn(

i_clk,

i_rst,

o_I_dw,

o_peak,

o_syn,

frame_data_en,

frame_data

);

input i_clk;

input i_rst;

output signed[11:0]o_I_dw;

output signed[14:0]o_peak ;

output o_syn;

output frame_data_en;

output signed[11:0]frame_data;

//测试信号

signal_gen signal_gen_u(

.i_clk (i_clk),

.i_rst (i_rst),

.o_I_dw(o_I_dw)

);

//帧同步

//峰值计算

wire signed[29:0]w_peak2;

peak_cal peak_cal_cal_u1(

.i_clk (i_clk),

.i_rst (i_rst),

.i_base_signal(o_I_dw[11:4]),

.o_peak (),

.o_peak2 (w_peak2)

);

assign o_peak= w_peak2[23:8];

//峰值检测,输出帧同步使能信号

//峰值定位,包括阈值判决粗同步和峰值最大值定位精同步

frame_syn frame_syn_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_lvl (16'd3000),

.i_peak ({o_peak}),

.o_syn (o_syn)

);

...........................................................................

assign frame_data=(frame_data_en==1'b1)?dly_dat[12]:12'd0;

endmodule

00_029m4.完整算法代码文件

V