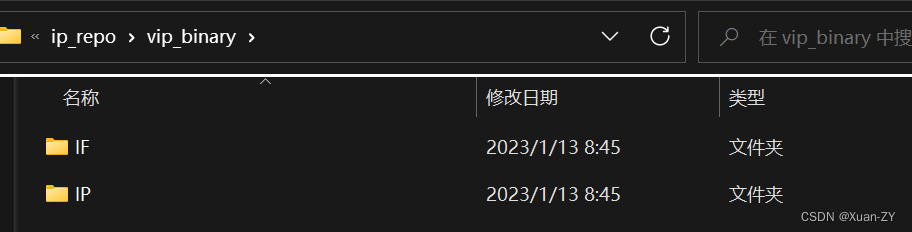

step1:新建文件

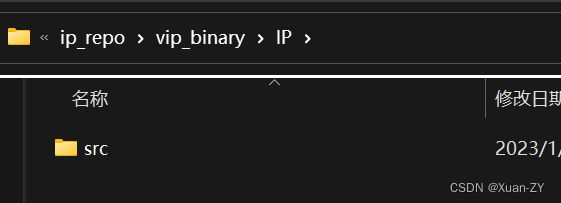

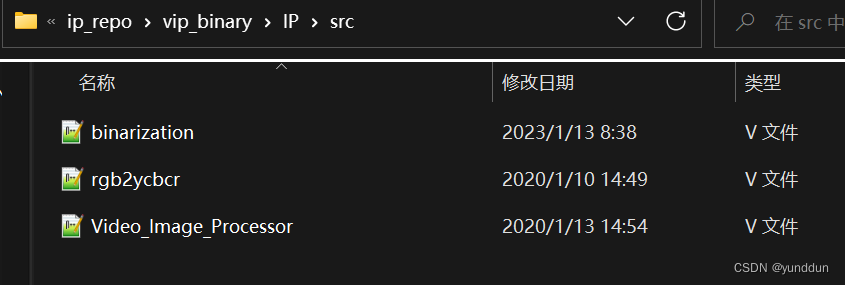

将源码放进src中

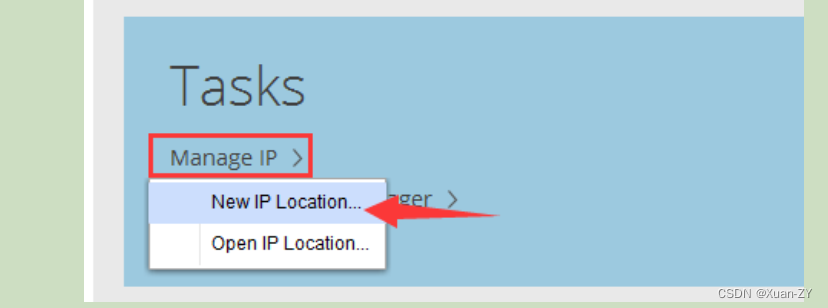

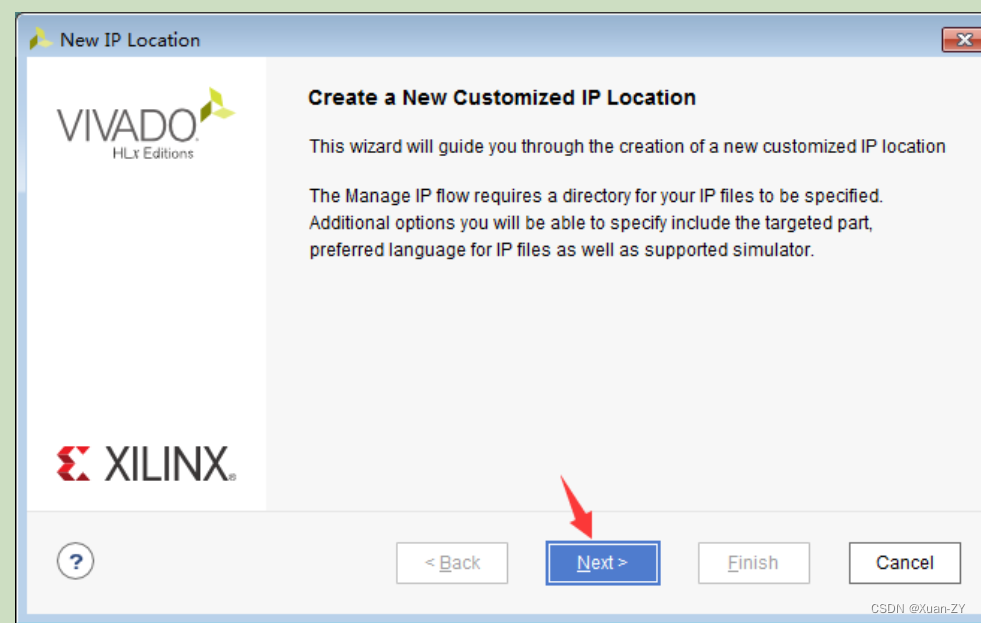

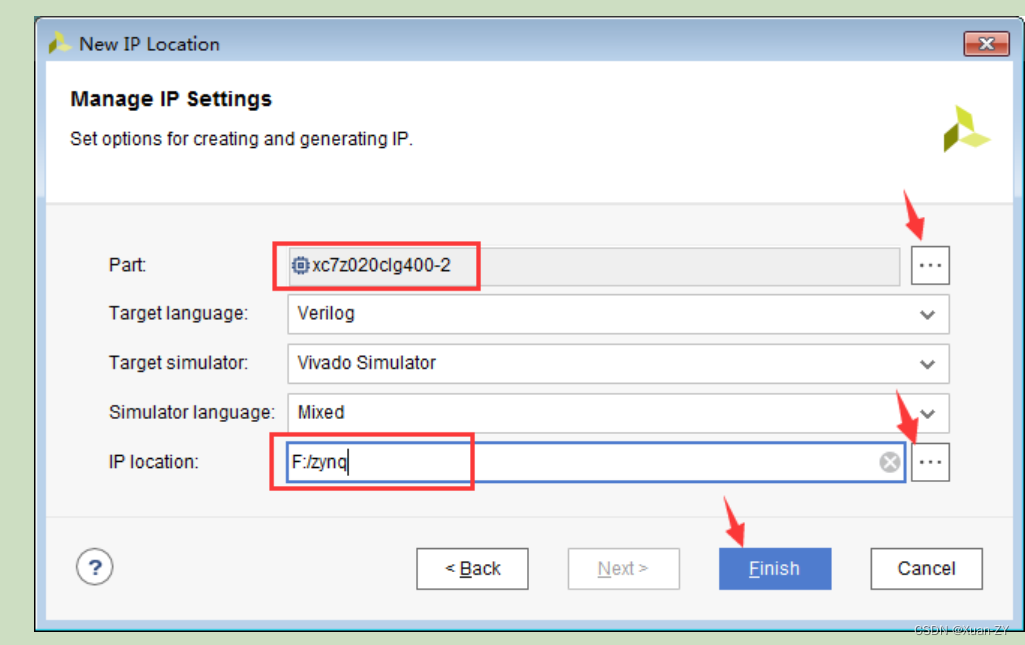

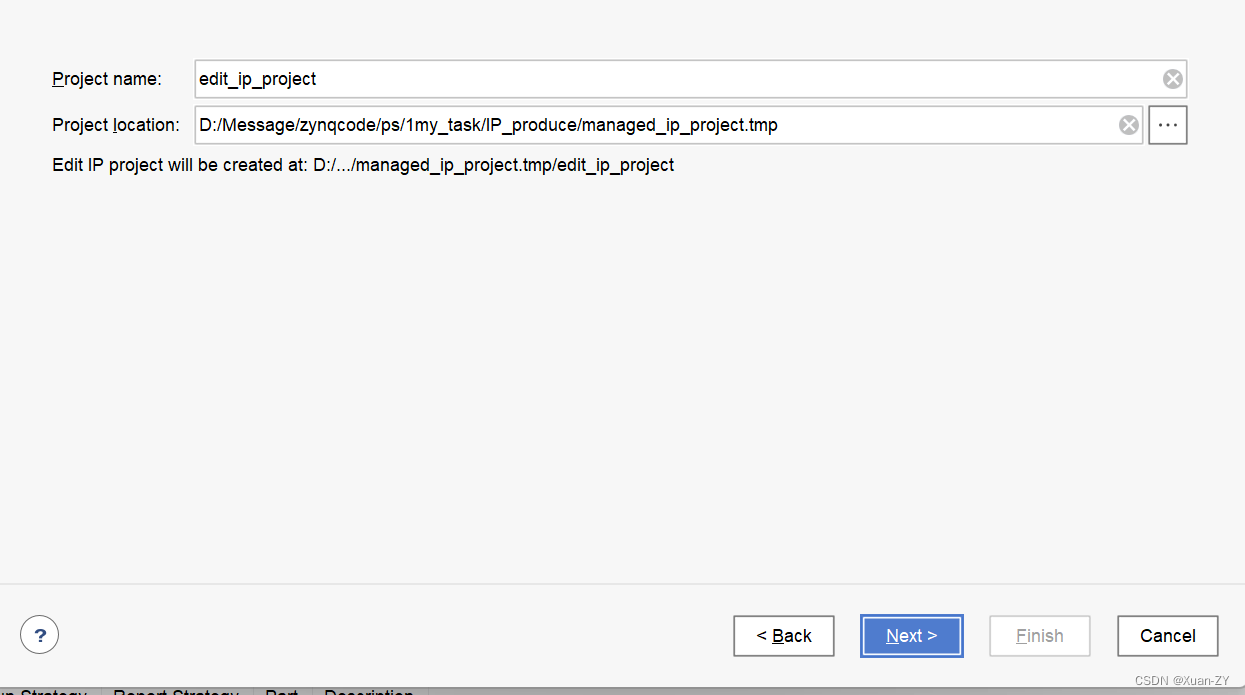

step2:新建IP location(可以多次使用,下次无需创建)

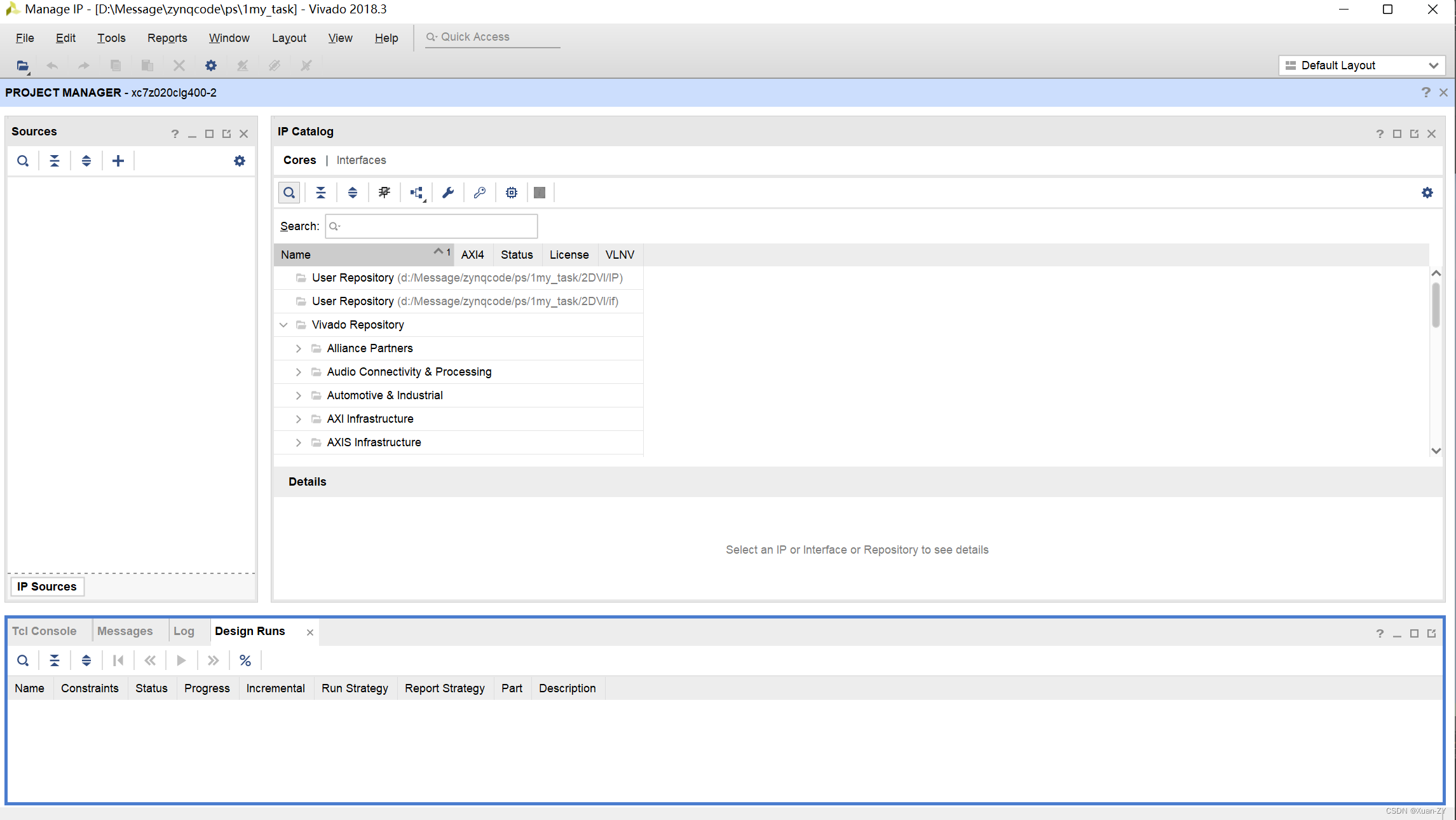

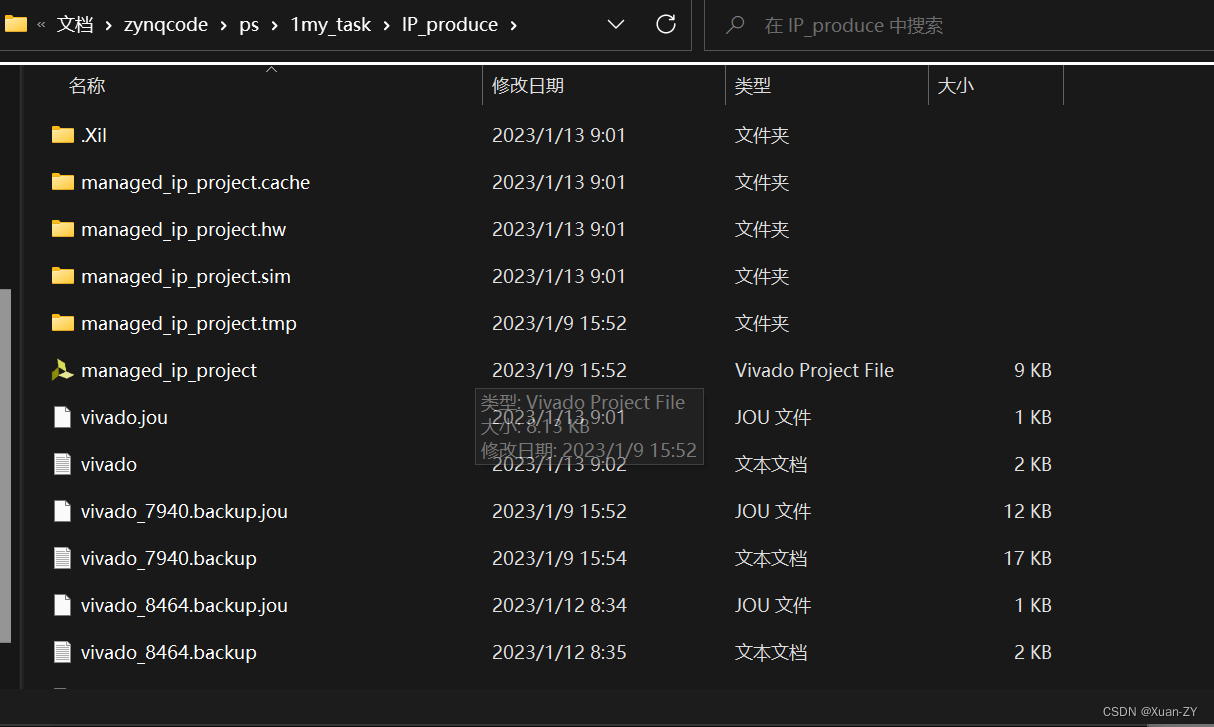

点击“ Finish”之后, Vivado 会新建一个名为“ Manage IP”的工程,

IP_produce就是我管理IP核的一个空间,下次就不用重复step2,直接在这个空间内就可以进行IP核操作

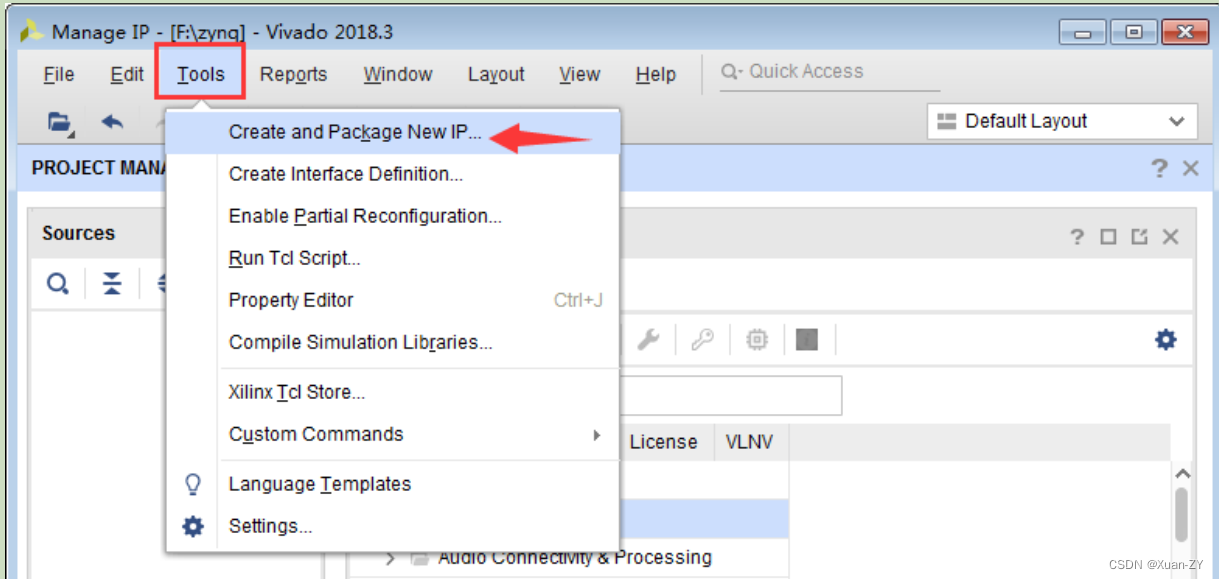

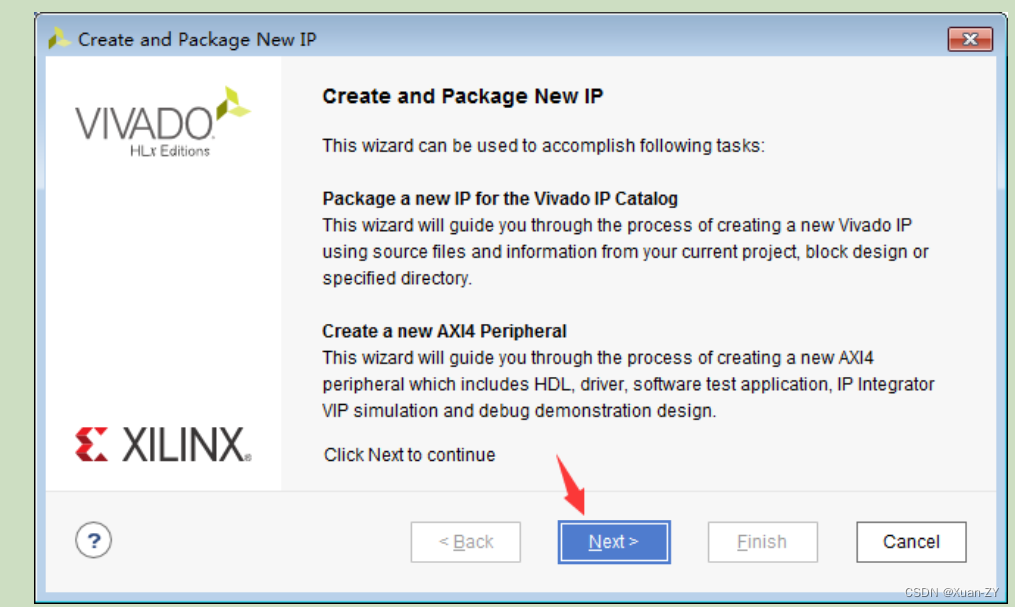

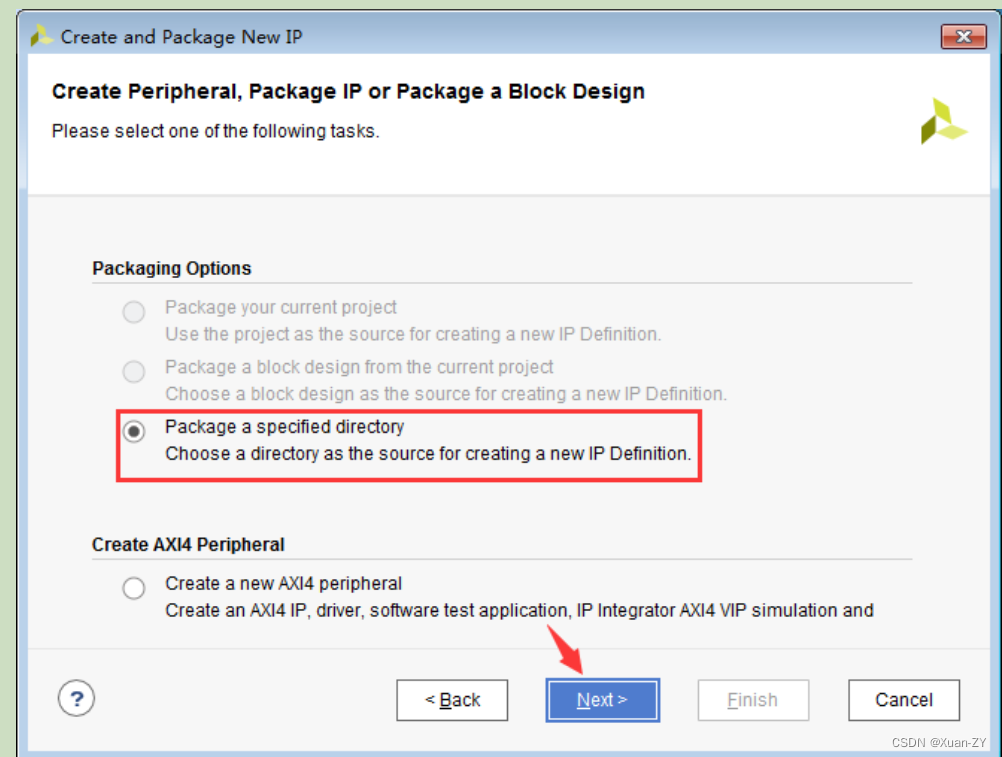

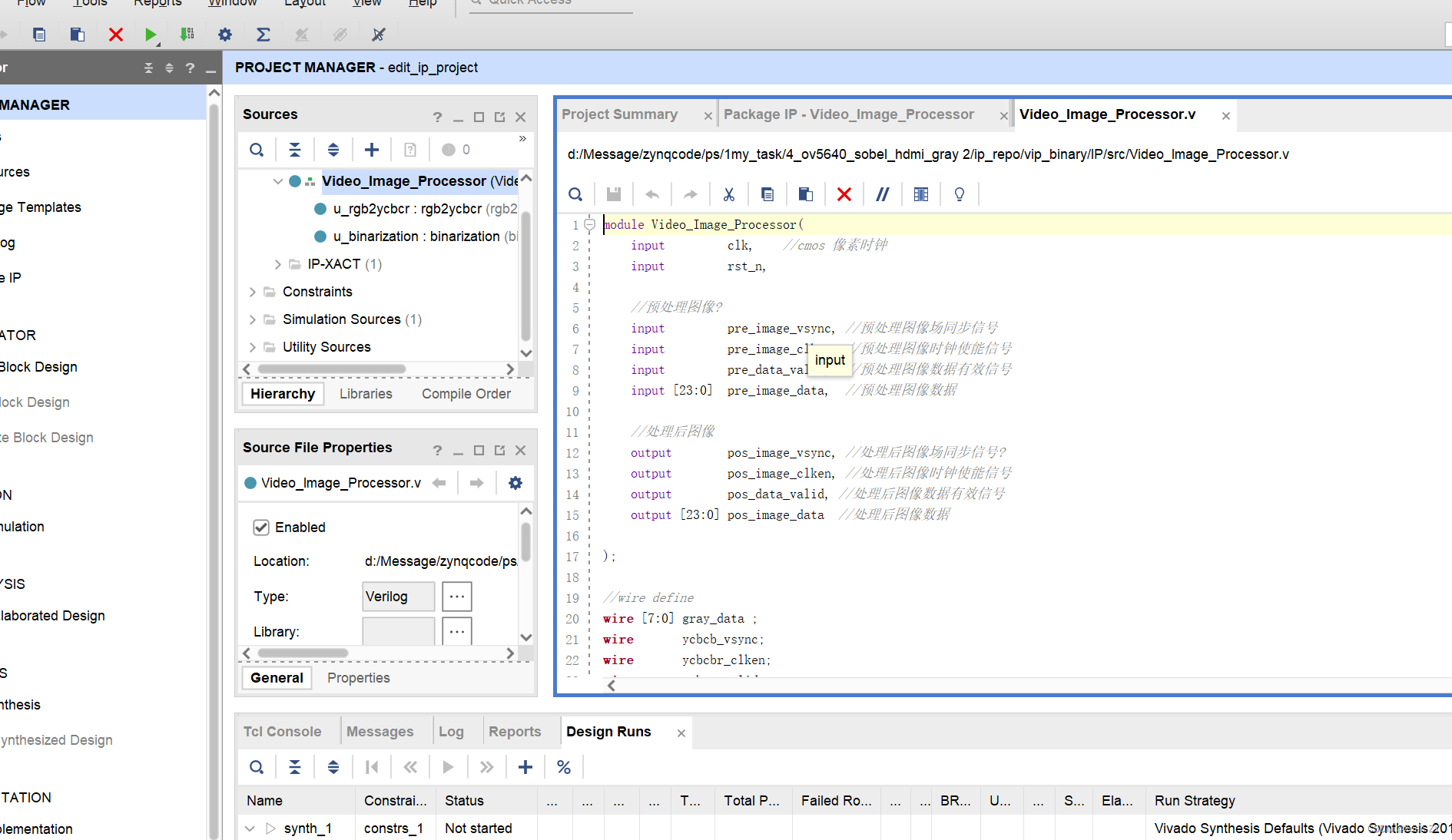

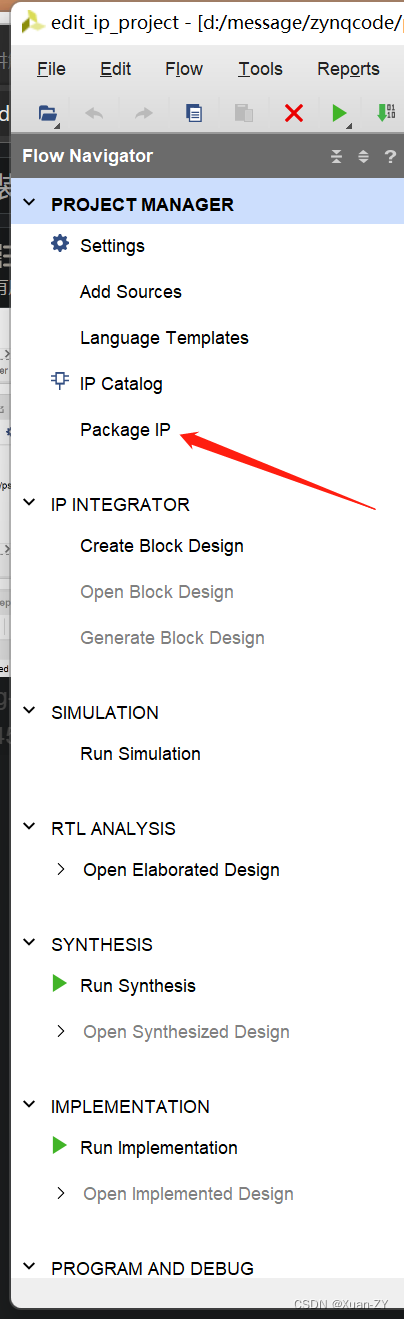

step3:封装IP核

下面那个选项则是新建一个axi接口

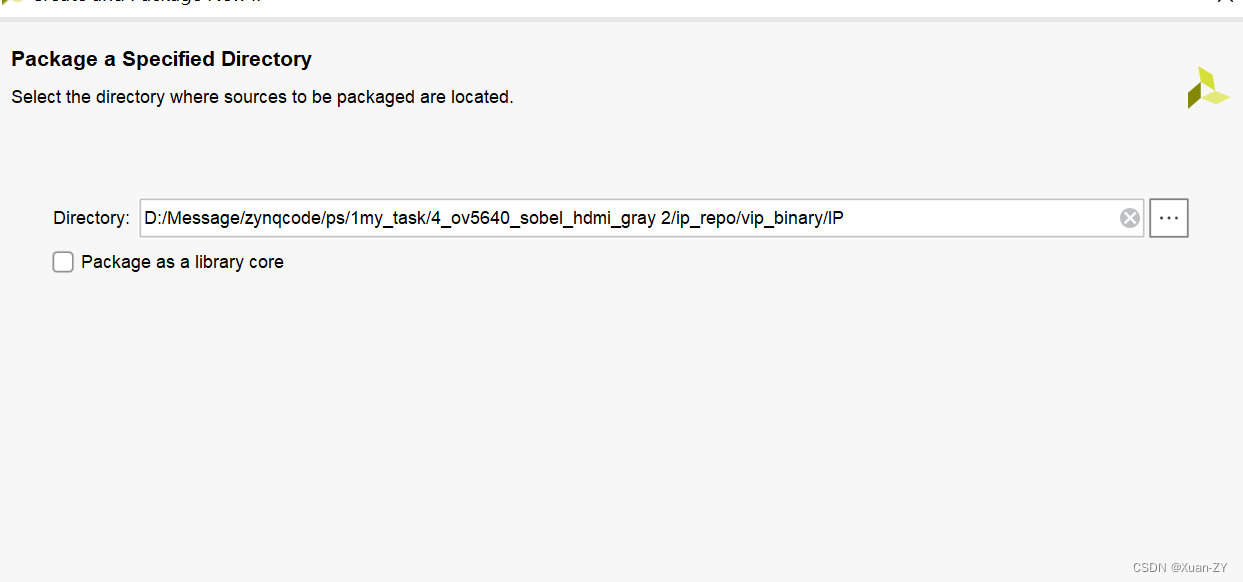

选择step1中的IP目录

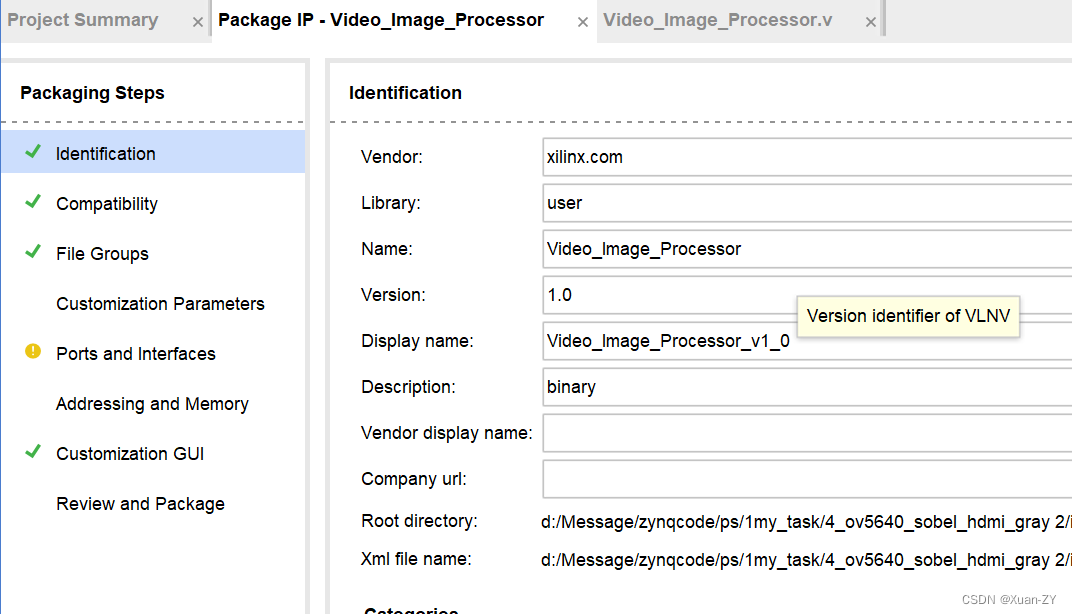

step4:设置IP

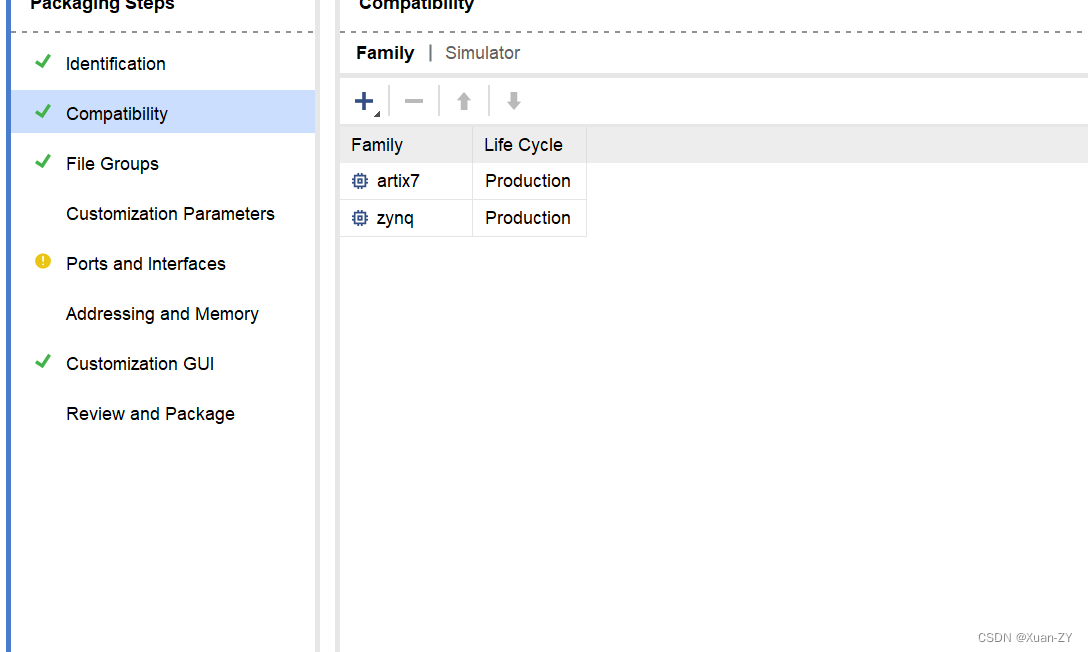

IP 核兼容性是指我们封装的 IP 核可用于哪些型号的器件。由于我们封装的 RGB2DVI 模块在设计时用到了器件的原语, 其功能与器件底层的硬件结构有一定的关联, 因此并不适用于 Xilinx 所有型号的器件。由于 ZYNQ7010/7020 的 PL 部分等同于 Artix7 系列的 FPGA, 因此我们在 IP 核兼容性中只保留 artix7 和 zynq这两个系列。

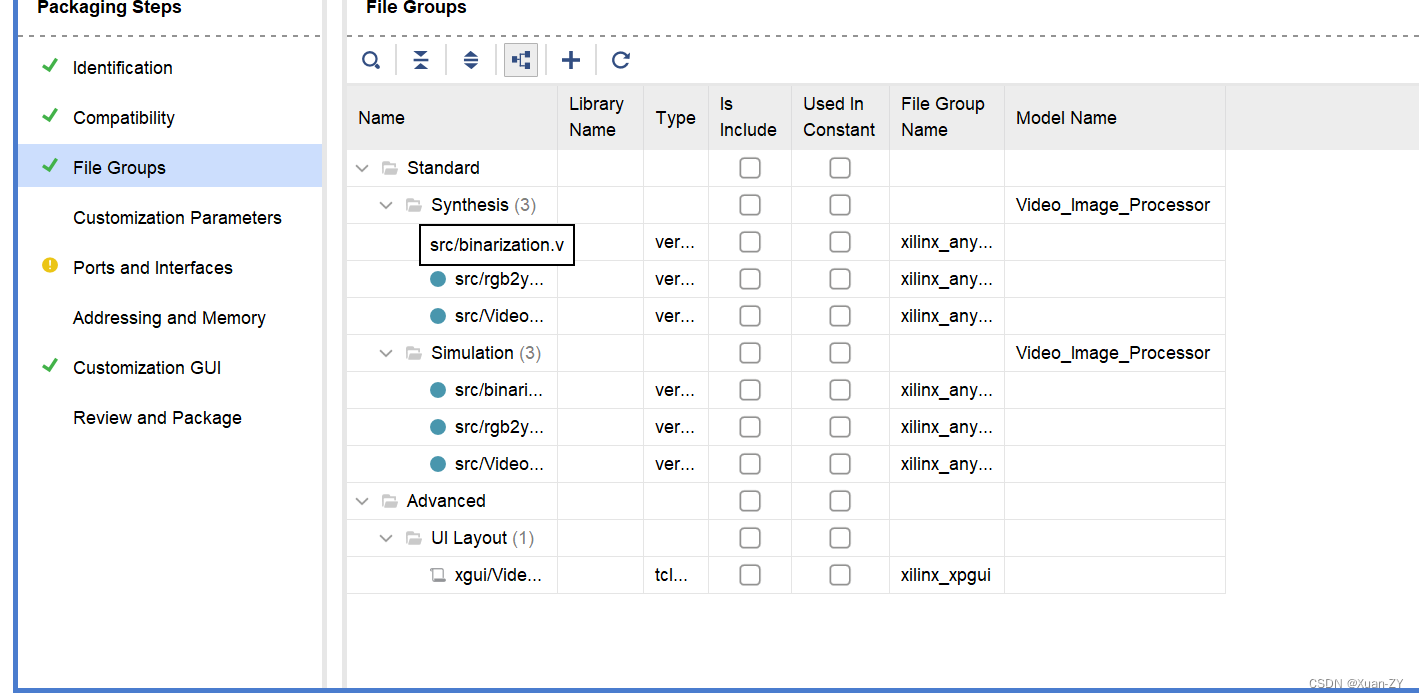

设置文件组

如果修改过顶层模块,这边需要修改

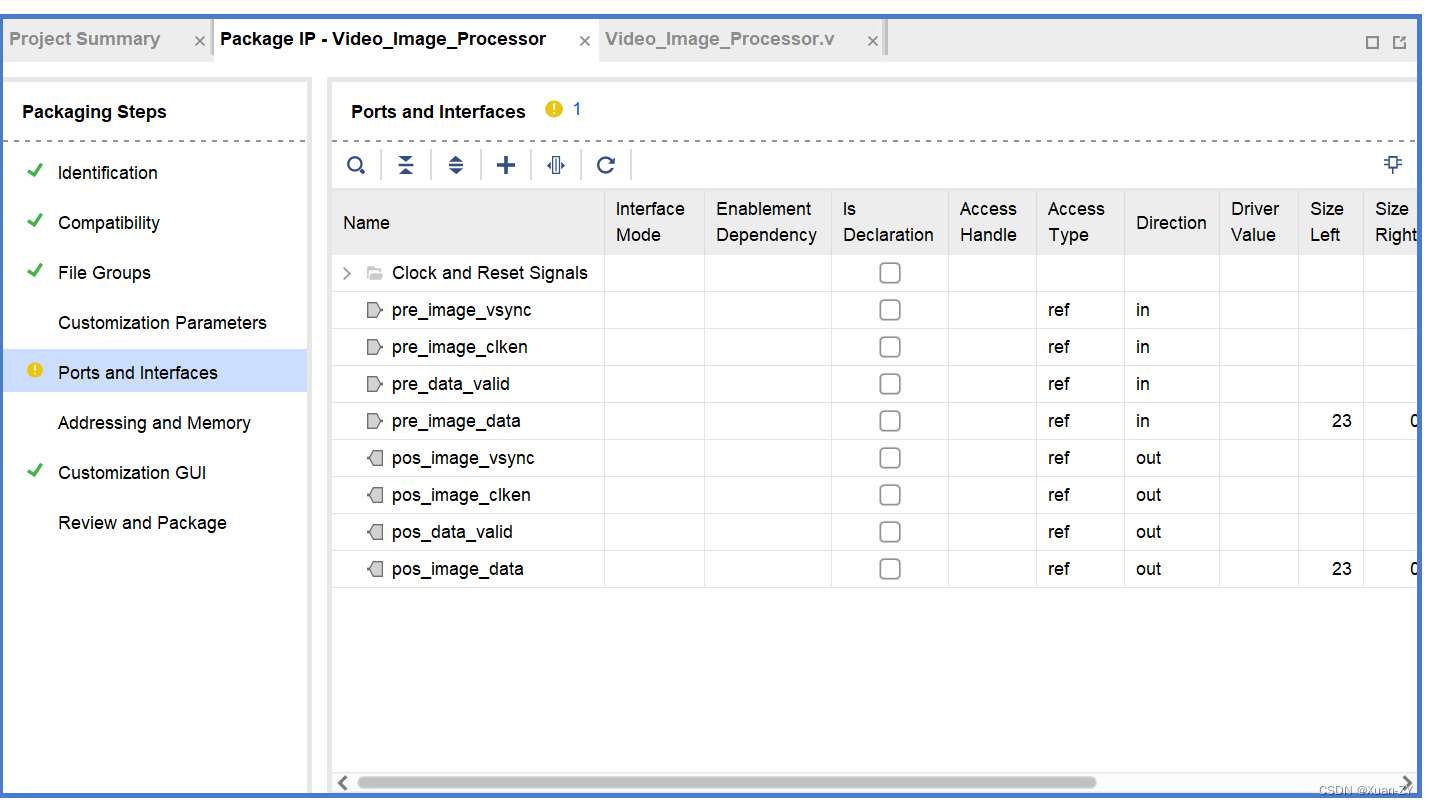

设置端口和接口(interface)

此处需要对比顶层模块代码,观察有没有端口错误

第一行软件自动识别并且封装好接口

剩下的端口都需要手动去映射

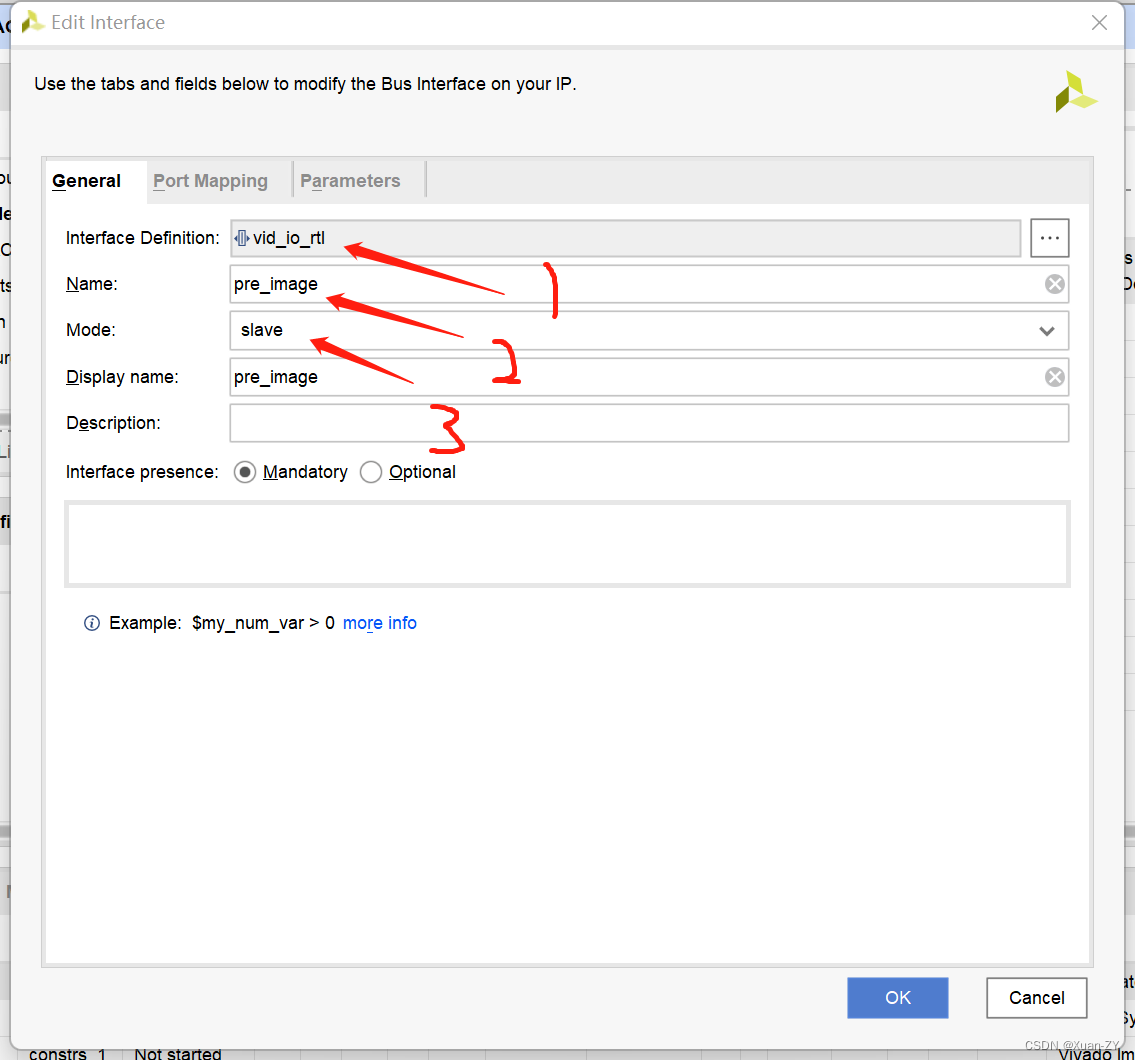

1:接口类型:必须和前级输出接口相同,否则接不上(直接调用前面的接口,自创一个功能相同的无法适用)

2:主从模式:

主(master):此端口发出数据

从(slave):此端口接受数据

3:显示名称

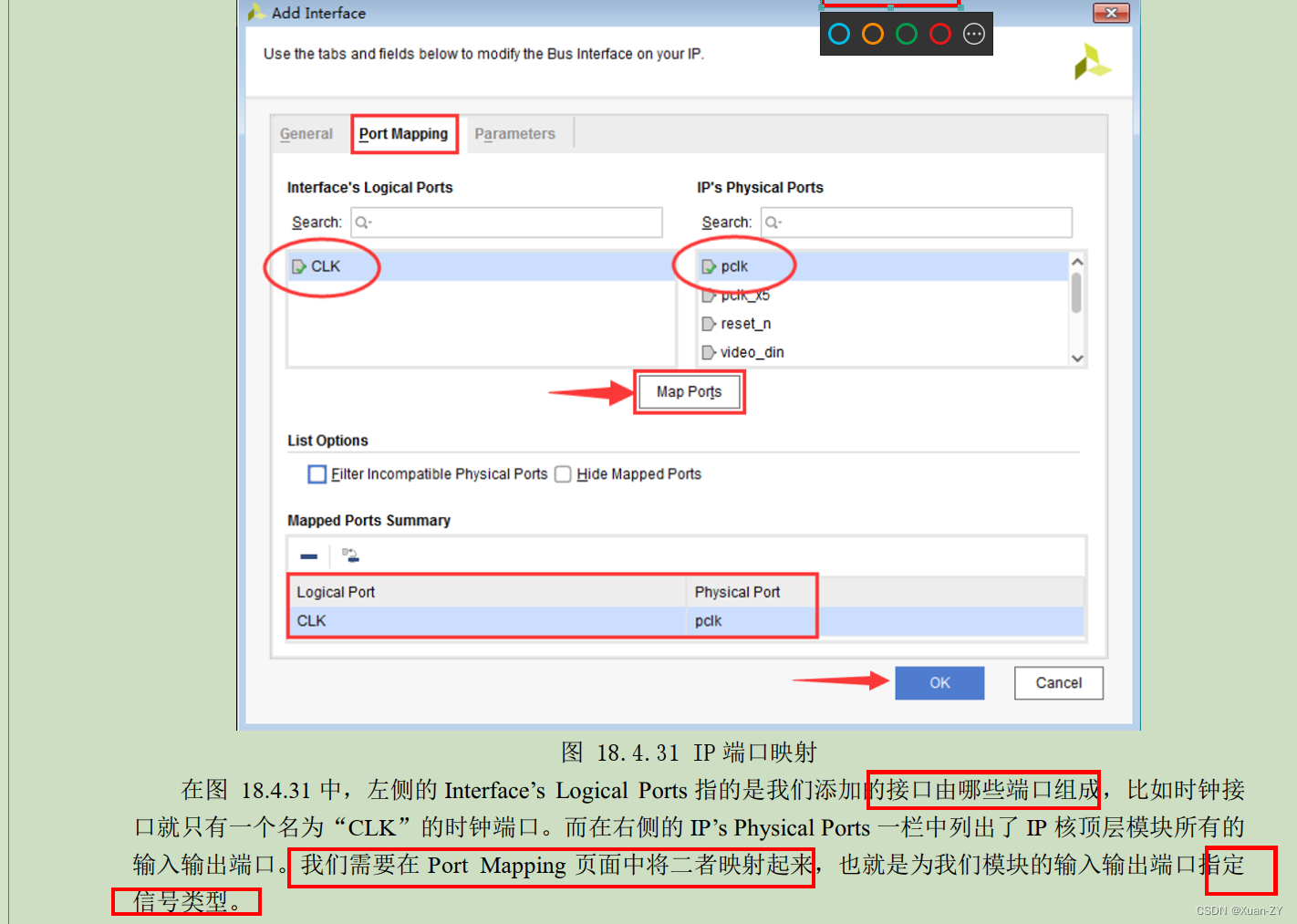

映射接口

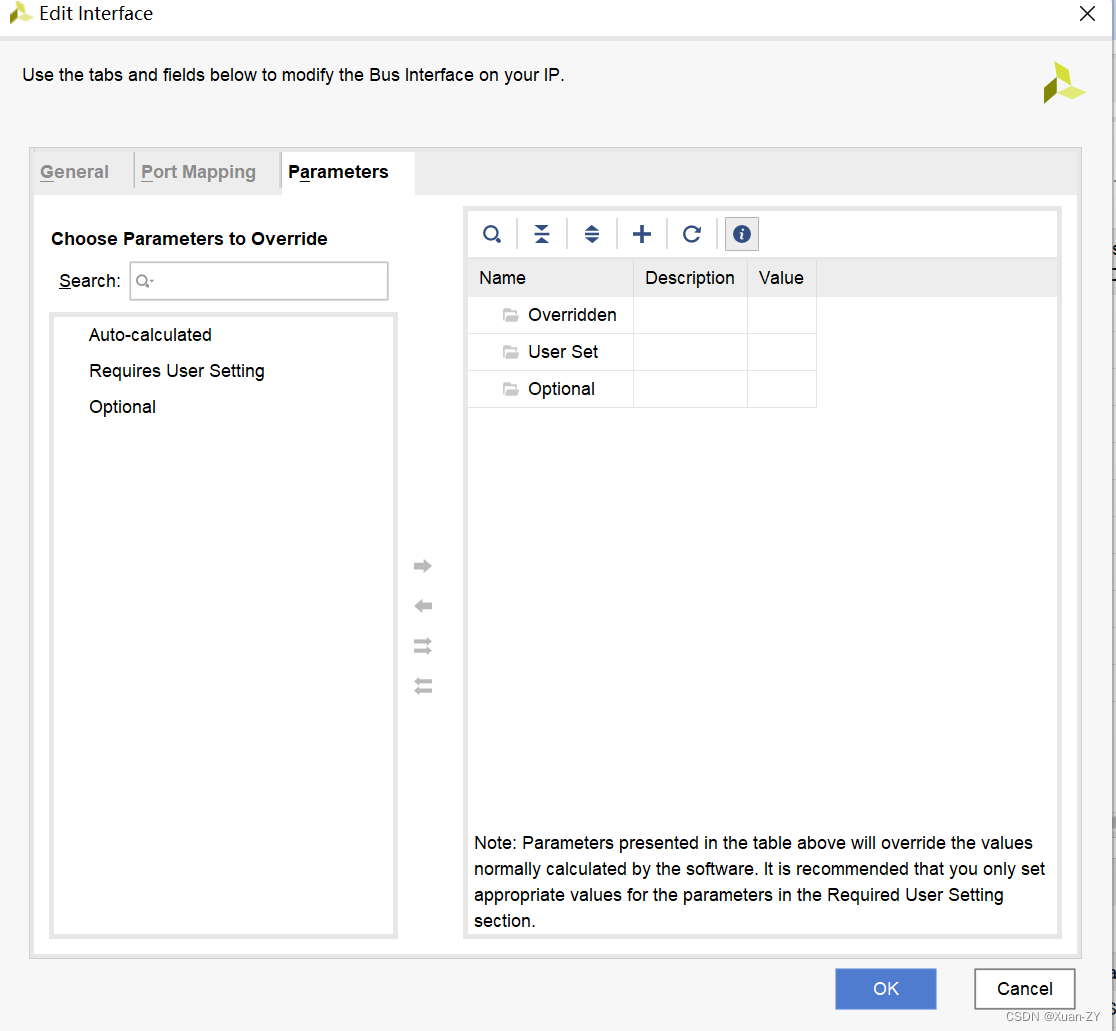

parameters:默认

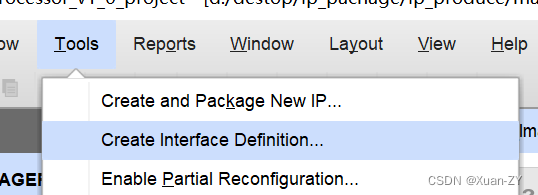

1:新建新的IP核

2:新建创建新的接口(interface)