目录

前言

文章使用的工具及板子类型

- 工具:Quartus II 13.1

- 开发板:Cyclone IV E EP4CE115F29C7

实验目的

- 学习 Quartus Prime 、Platform Designer、Nios II SBT 的基本操作;

- 初步了解 SOPC 的开发流程,基本掌握 Nios II 软核的定制方法;

- 掌握 Nios II 软件的开发流程,软件的基本调式方法。

1 简介

1.1 了解Qsys

Quartus中的一个系统集成工具

- 名称

最先版本中名为SOPC Builder,最新版本名为Platform Designer - SOPC的含义

可编程片上系统(采用编程方法将整个系统集成到一个芯片上) - Qsys作用

- 通过集成IP核快速实现SOPC系统

- 自动创建IP核之间的互联逻辑

- 自定义IP核

1.2 Nios II的介绍

FPGA所设计的一种RSIC架构的嵌入式软核处理器

Nios II的三种产品

- Nios II/f(快速)——最高的系统性能,中等FPGA使用量

- Nios II/s(标准)——高性能,低FPGA使用量

- Nios II/e(经济)——低性能,最低的FPGA使用量

1.3 PIO简介

- 定义

PIO IP核:Avalon-MM从端口和通用I/O端口提供了一个存储器映射(memory-mapped)接口 - 用途

用户逻辑或外围器件提供了简单的I/O控制

例如:- 控制LED灯

- 获取按键的电平变化信息

- 控制显示设备

- 与片外器件通信(SPI、I2C)

- 寄存器

| 偏移量 | 寄存器名称 | 读/写 | 含义 |

|---|---|---|---|

| 0 | data | 读/写 | 读的时候,获取当前PIO输入的端口值,写的时候,输出到PIO端口的值,可配置单向功能 |

| 1 | direction | 读/写 | 控制每个I/O的数据方向,0为输入,1表示输出 |

| 2 | interruptmask | 读/写 | 各输入端口的中断使能信号,1表示使能中断 |

| 3 | edgecapture | 读/写 | 各输入端口的边沿触发中断 |

| 4 | outset | 写 | 设定输出位位1 |

| 5 | outclear | 写 | 设定输出位为0 |

2 Nios II软核实现流水灯

2.1 Qsys系统设计

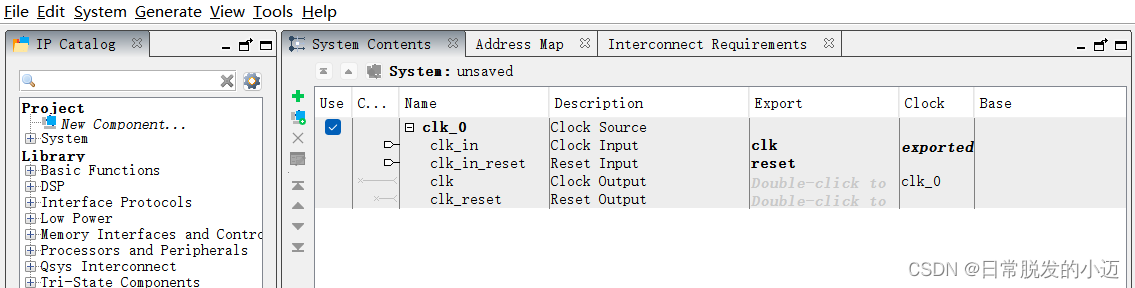

-

点击 Tools 下拉菜单下的 Qsys 工具

-

启动 Qsys 后,点击

File —> save,如图 1.7 所示,在文件名中填写为 kernel,后点击 OK -

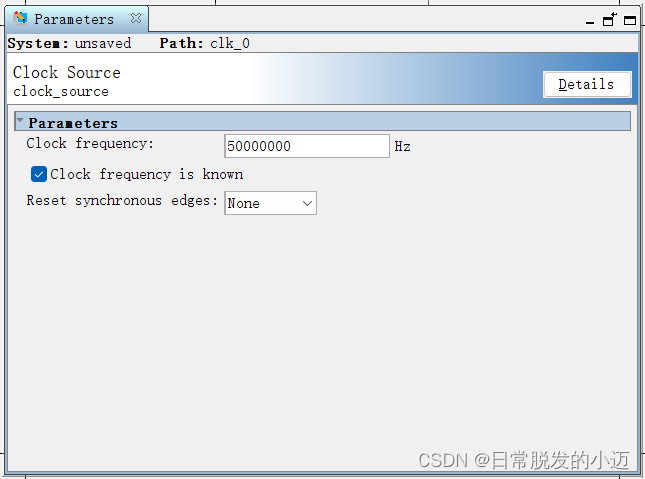

鼠标放在 clk_0 处点击右键 Edit 或是双击 clk_0 元件,对 Clock 进行时钟设置,设为为 50M

-

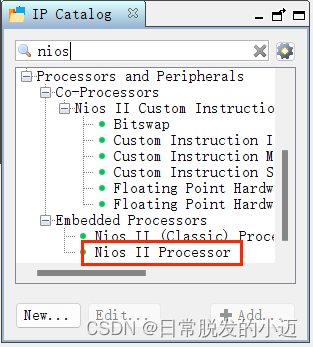

添加 Nios II 32-bit CPU

-

在 “component library” 标签栏中找到 “Nios II Processor” 后点击 Add

扫描二维码关注公众号,回复: 15421805 查看本文章

扫描二维码关注公众号,回复: 15421805 查看本文章

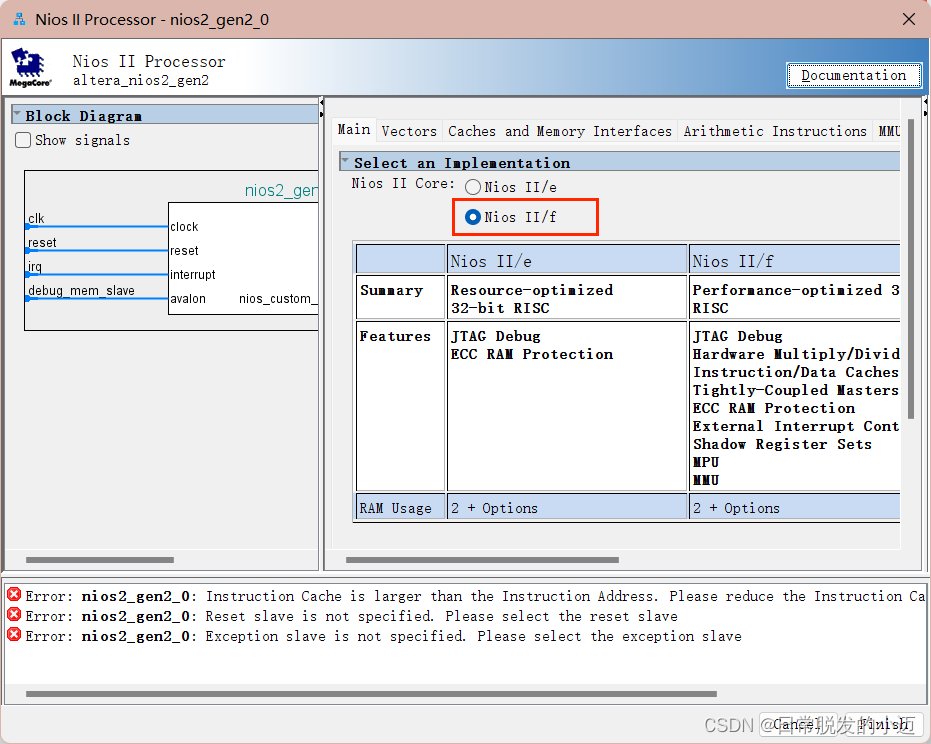

-

在 Nios Core 栏中选择 Nios II/f 选项,其他保持默认选项

-

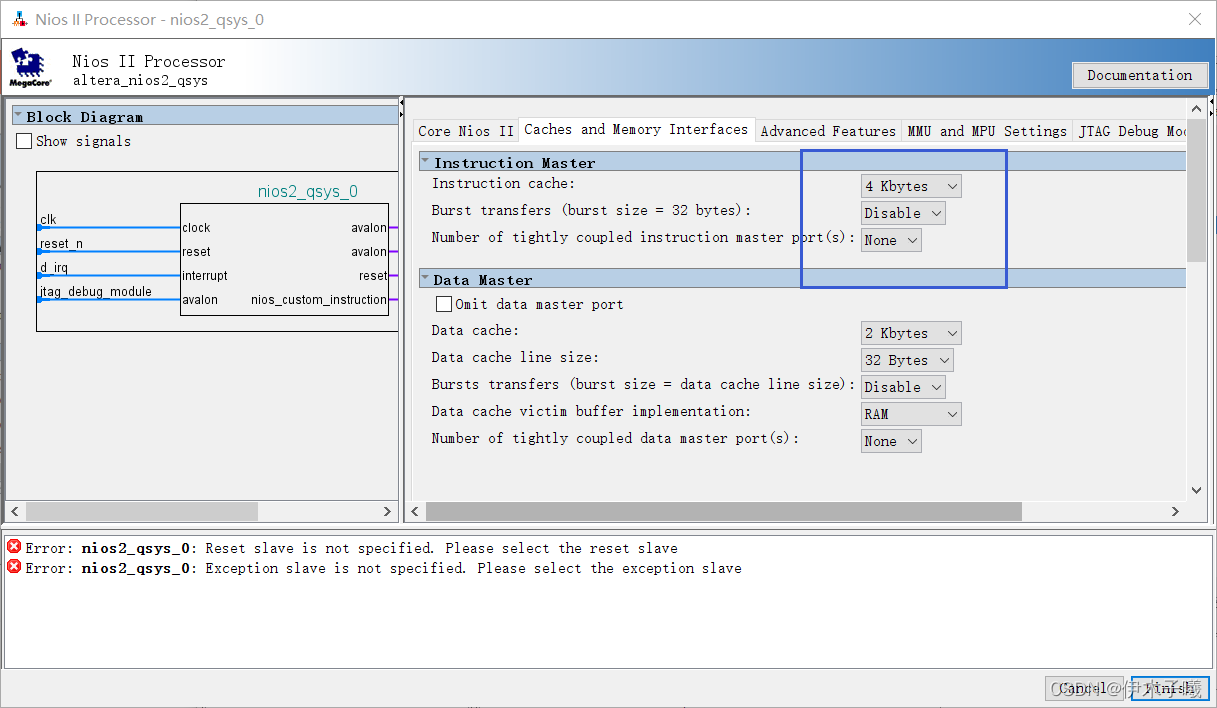

在 ”Caches and Memory Interfaces” 标签栏中保持默认设置 (Instruction Cache 选择

4Kbytes) -

在 ”Advanced Features” 标签栏中保持默认设置

-

在 ”MMU and MPU Settings” 标签栏中保持默认设置

-

在 ”JTAG Debug Module” 标签栏中保持默认设置

-

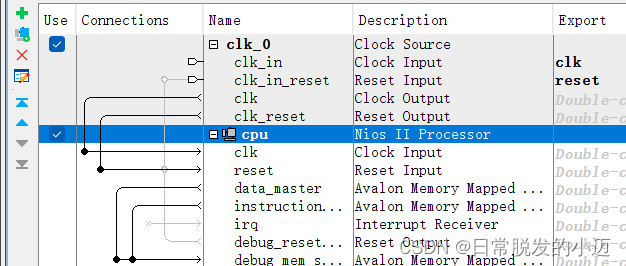

点击 Finish 回到 Qsys 界面 将 nios2_qsys_0 重命名为

cpu -

将 cpu 的 clk 和 reste_n 分别与系统时钟

clk\_0的clk和clk\_reset相连

-

-

添加 jtag uart 接口

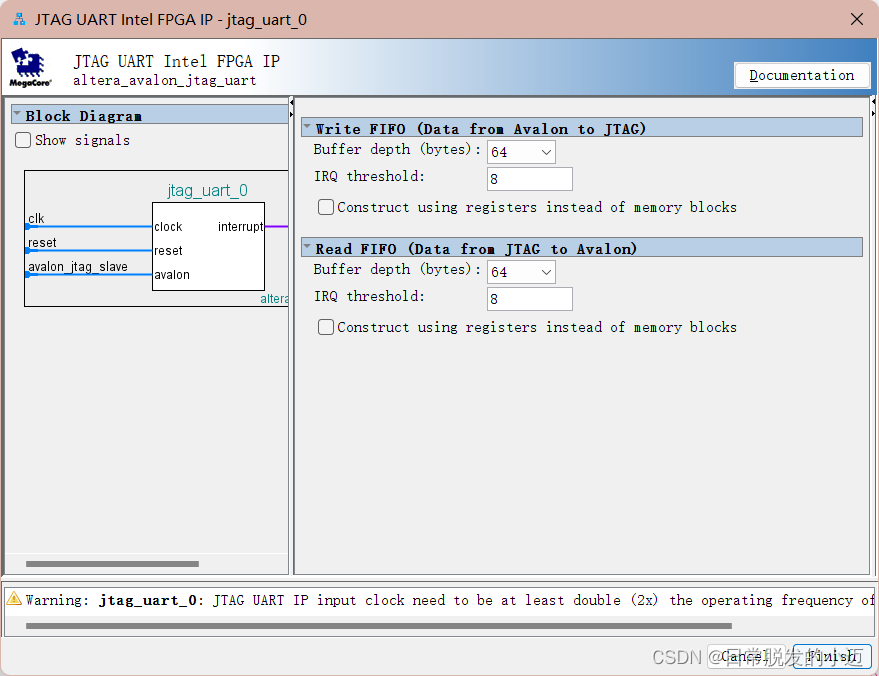

- 同样,在 ”Component Library” 标签栏中的查找窗口输入 jtag 找到 ”JTAG UART ”,然后点击 Add

- 在 JTAG UART-jtag-uart_0 的设置向导中保持默认选项,点击 Finish

- 在 ”Name” 列中将

jtag-uart_0 重命名为 jtag-uart。

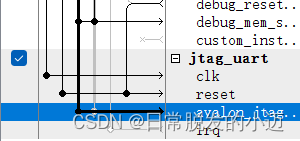

进行 clk、reset 以及 master-slave 的连线

进行中断 irq 连线

- 同样,在 ”Component Library” 标签栏中的查找窗口输入 jtag 找到 ”JTAG UART ”,然后点击 Add

-

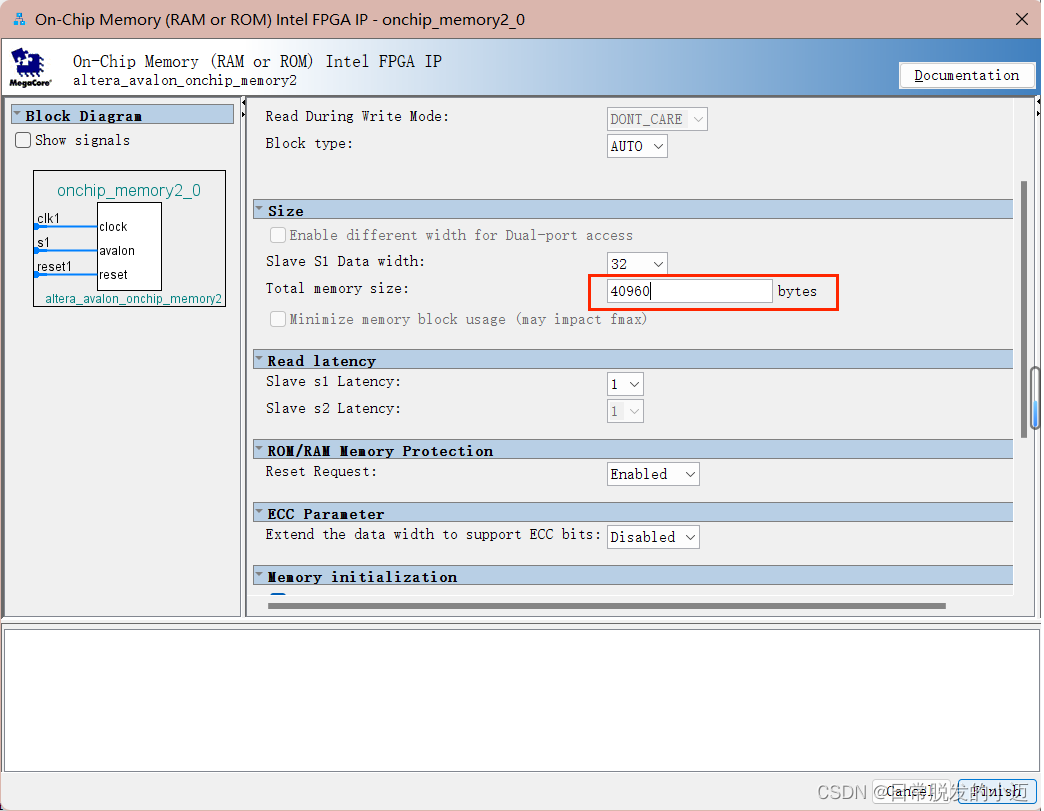

添加片上存储器 On-Chip Memory(RAM)核

- 在左侧 ”Component Library” 标签栏中的查找窗口输入 On Chip 找到 ”On-Chip

Memory(RAM or ROM)” 后点击 Add

- 在 ”Size” 栏中的 ”Total memory size” 窗口中输入 40960(即片上内存的大小为 40KB),其余选项保持默认,点击 Finish。

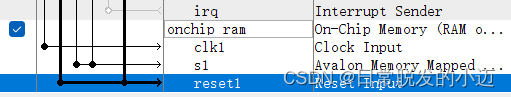

- 在 ”Name”

列中将 onchip_memory2_0 改名为 onchip_ram - 进行时钟、数据端口、指令端口的连接

- 在左侧 ”Component Library” 标签栏中的查找窗口输入 On Chip 找到 ”On-Chip

-

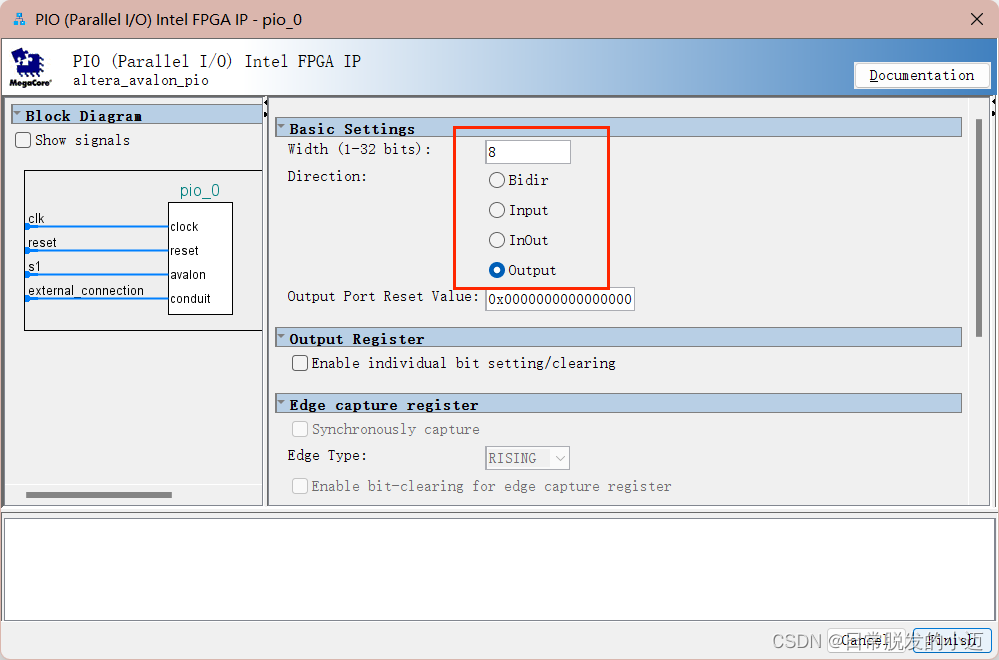

添加 PIO 接口

- 在左侧 ”Component Library” 标签栏中的查找窗口输入 pio 找到 ”PIO” 后点击Add

- 确定以下选项:Width 为 8bits,Direction 选择 output,其余选项保持默认,点击

Finish。

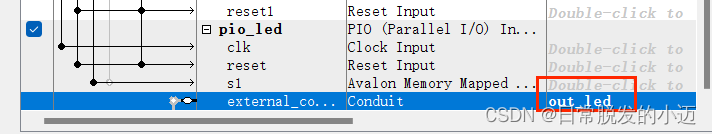

- 返回 ”System Contents” 标签栏可以看到新加入的 ”PIO” 核。在 ”Name” 列中将

pio_0 改名为 pio_led。并在在 Export 栏处双击,把输出口引出来,并命名为 out_led。 - 进行时钟、数据端口、指令端口的连接

- 在左侧 ”Component Library” 标签栏中的查找窗口输入 pio 找到 ”PIO” 后点击Add

-

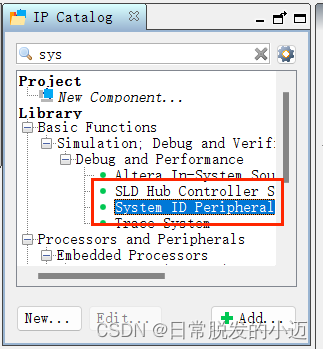

添加片 System ID Peripheral 核

- 在左侧 ”Component Library” 标签栏中的查找窗口输入 sys 找到 ” System ID

Peripheral” 后点击 Add - 保持默认选项,单击 Finish。

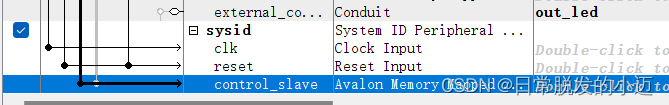

- 返回 ”System Contents” 标签栏可以看到新加入的 ” System ID Peripheral” 核。在 ”Name” 列中将 sysid_qsys_0 改名为 sysid

- 进行时钟、数据端口的连接

- 在左侧 ”Component Library” 标签栏中的查找窗口输入 sys 找到 ” System ID

-

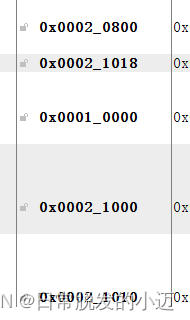

基地址分配

击 Qsys 主界面菜单栏中的 ”System” 下的 ”Assign Base Addresses”。

-

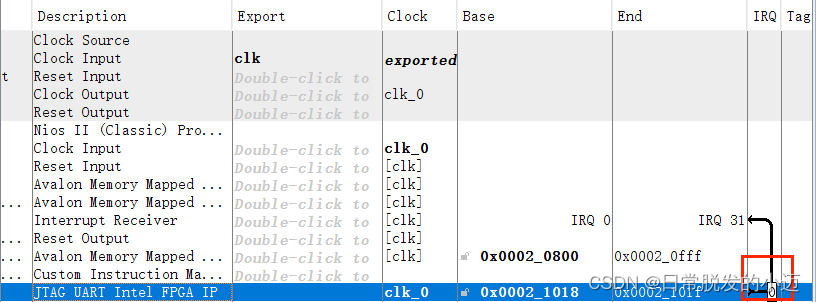

分配中断号

在 ”IRQ” 标签栏下点选 ”Avalon_jtag_slave” 和 IRQ 的连接点就会为 ”jtag_uart” 核添加一个值为 0 的中断号。

-

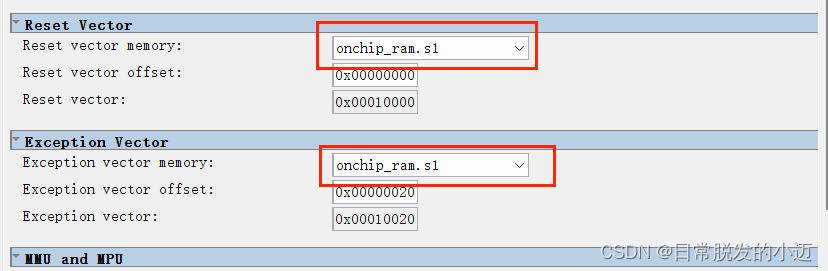

指定 NIos II 的复位和异常地址

从 ”System Contents” 标签栏双击建立好的 cpu 进入 Nios II

Processor 的配置界面,配置 Reset Vector 和 Exception Vector 为

”onchip_ram.s1”,点击 Finish。

-

点击 Qsys 主界面菜单栏中的 ”System” 下的 ”Create Global Reset Network”。完成后会自动连接所有复位端口

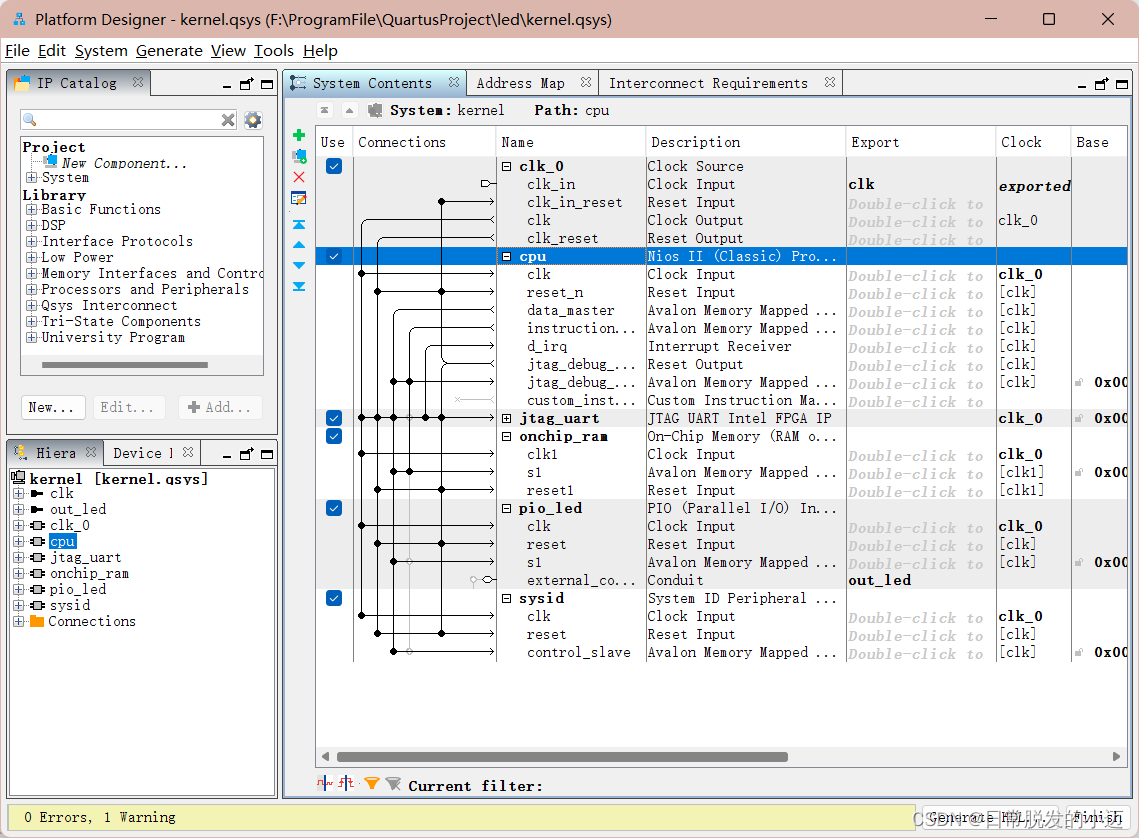

完整配置图如下:

-

生成 Qsys 系统

点选 ”Generation HDL” 标签栏中 Generate 按钮生成 Qsys 系统,保存文件

完成后,点击 Close 后关闭窗口后,再关闭 Qsys 主界面

2.2 逻辑连接

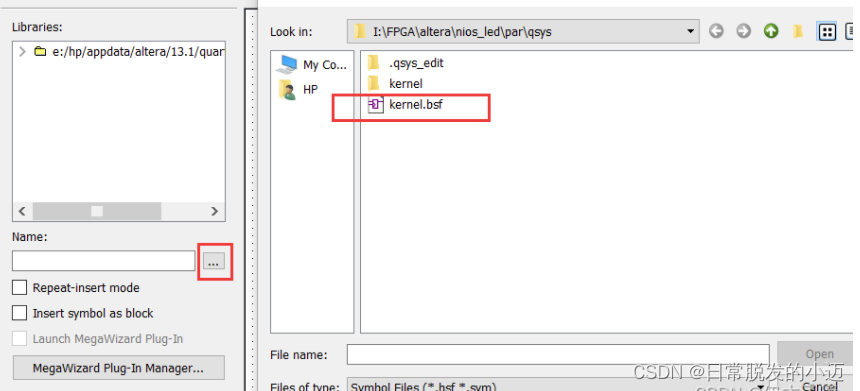

-

在 Quartus-II 中新建一个原理图

- 然后在该原理图(BDF)文件中添加 Qsys 生成的系统符号

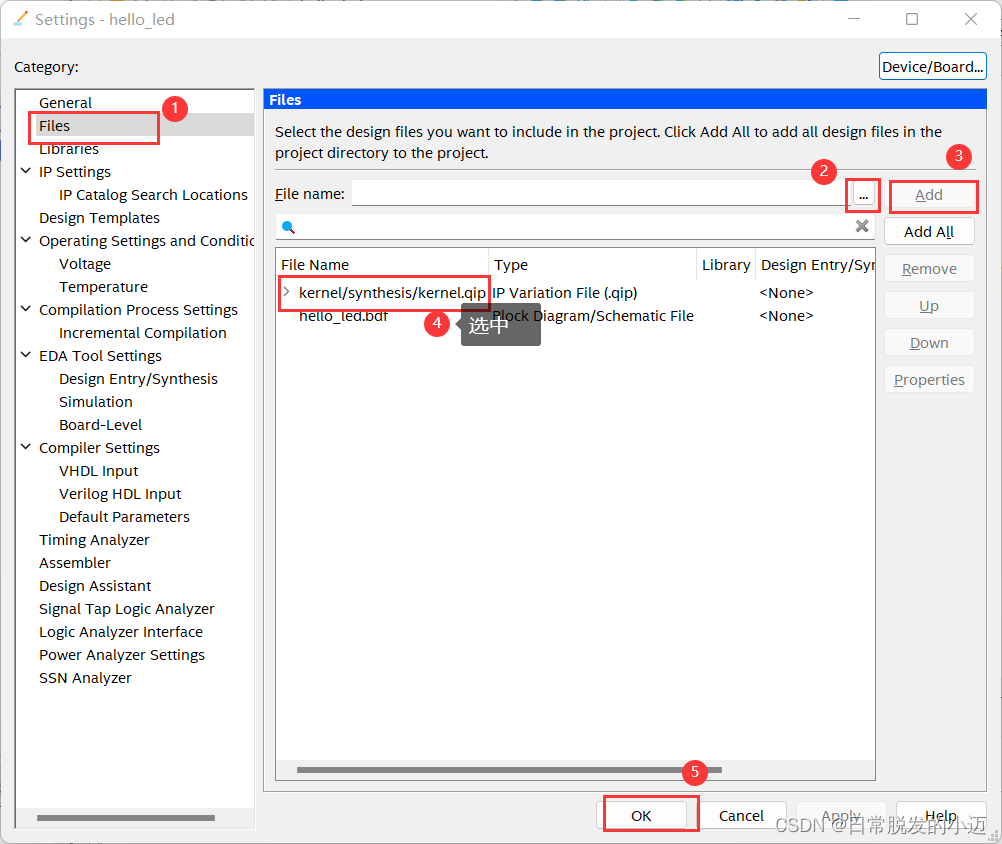

- 点击 Assignments-Settings,添加 kernel.qip 文件

- 然后在该原理图(BDF)文件中添加 Qsys 生成的系统符号

-

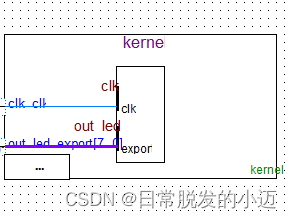

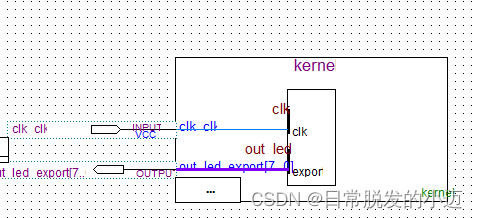

进行逻辑连接和生成管脚

-

在 kernel 模块内点击鼠标右键选取 Generate Pin for Symbol Ports 生成管脚,然后将管脚命名如下

-

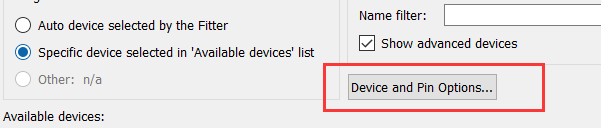

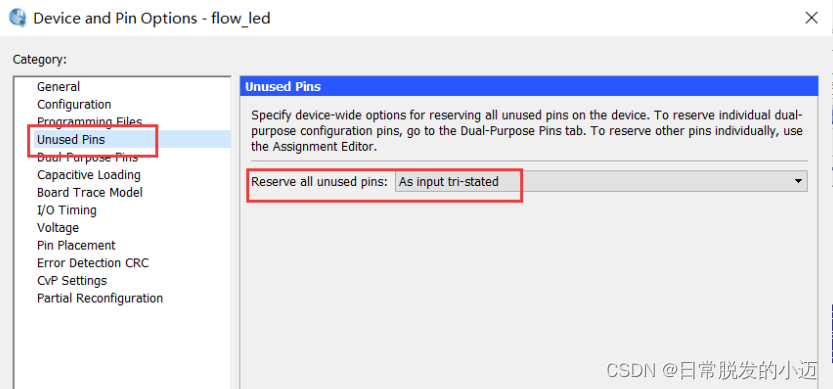

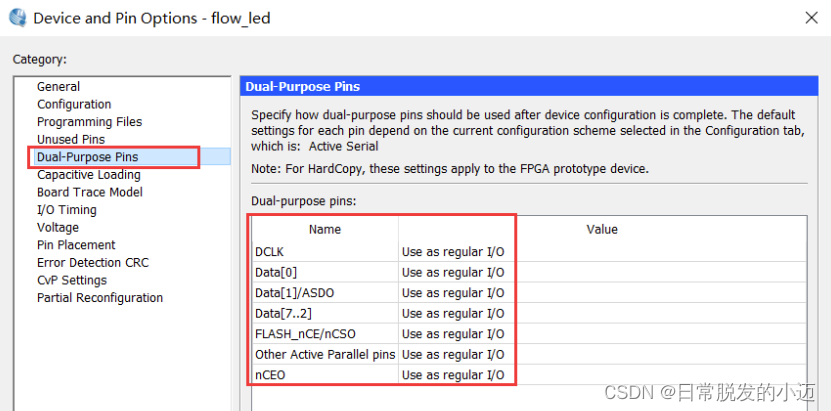

菜单里选择 Assignments-device,然后如下图所示点击 Device pin options

-

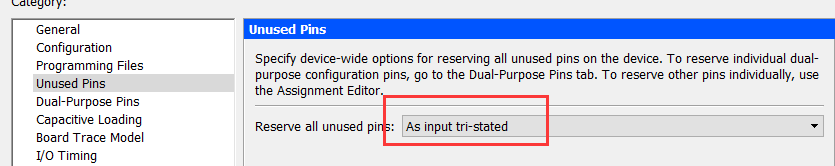

进行 unused pin 设置,可能会收到外部信号的干扰,将未用引脚设置为 As input tri-stated

-

-

编译工程

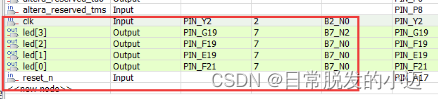

2.3 绑定引脚

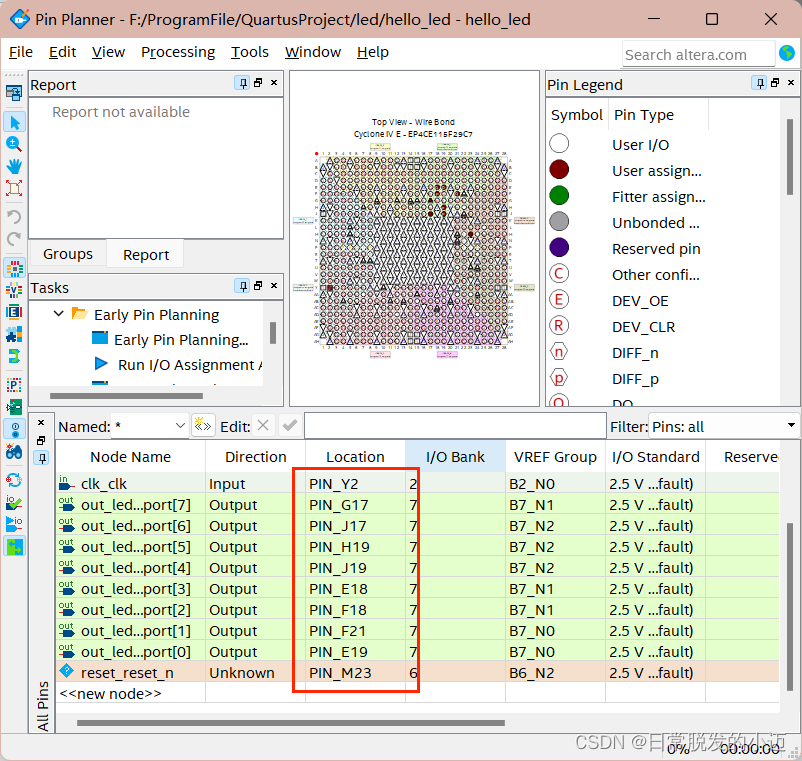

点击Pin Planner,设置引脚

引脚设置如下:

注意,引脚绑定后要再次编译工程

2.4 软件设计

使用 Nios II Software Build Tools for Eclipse

-

在 Quartus-II 界面,点击Tools,然后点击 Nios II Software Build Tools for Eclipse 打开 Nios II SBT for Eclipse

-

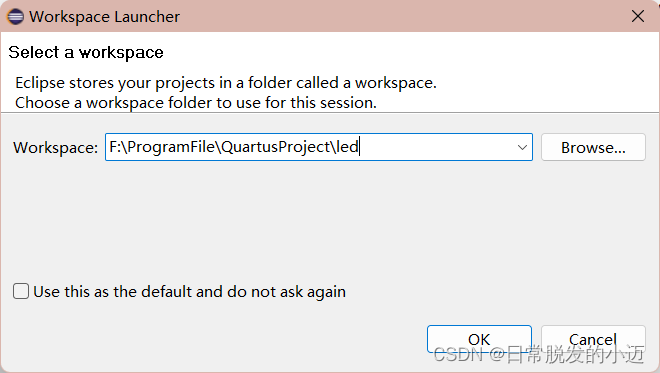

启动 Workspace 选择当前的项目目录,点 OK

-

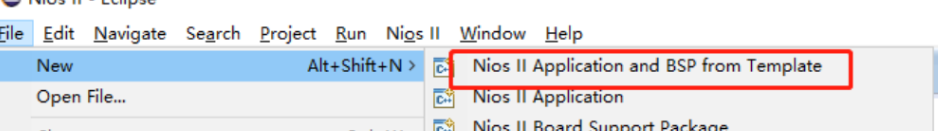

创建工程

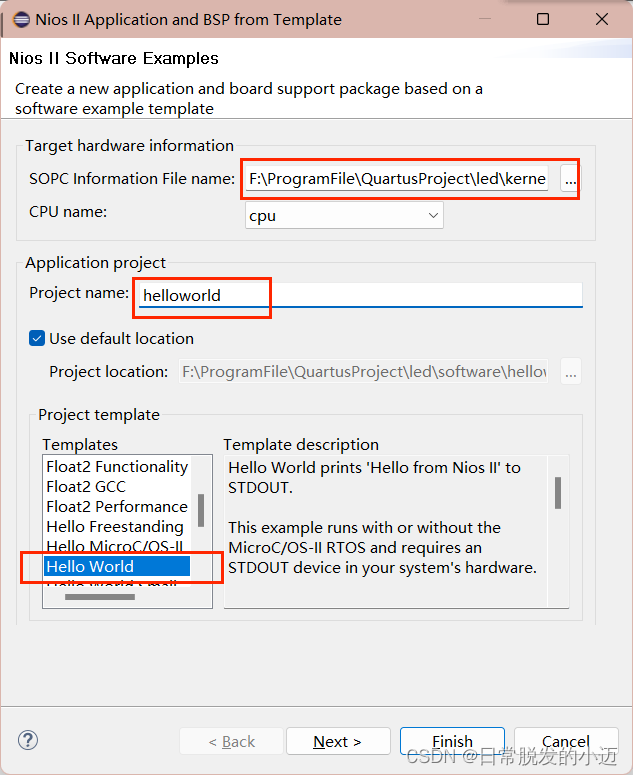

- 在 ”SOPC Information File name” 窗口中选择 kernel.sopcinfo 文件,以便将生成硬件配置信息和软件应用关联,CPU 栏会自动选择”CPU”。在 ”Project name” 输入 ”hello_world” ,Project template选择 Hello World。

- 将 hello_world.c 中的程序修改为流水灯控制程序,保存

#include "system.h"

#include "altera_avalon_pio_regs.h"

#include "alt_types.h"

const alt_u8

led_data[8]={

0x01,0x03,0x07,0x0F,0x1F,0x3F,0x7F,0xFF};

int main (void) {

int count=0;

alt_u8 led;

volatile int i;

while (1)

{

if (count==7)

{

count=0;}

else

{

count++;}

led=led_data[count];

IOWR_ALTERA_AVALON_PIO_DATA(PIO_LED_BASE, led);

i = 0;

while (i<500000)

i++;

printf("Hello world!\n");

}

return 0;

}

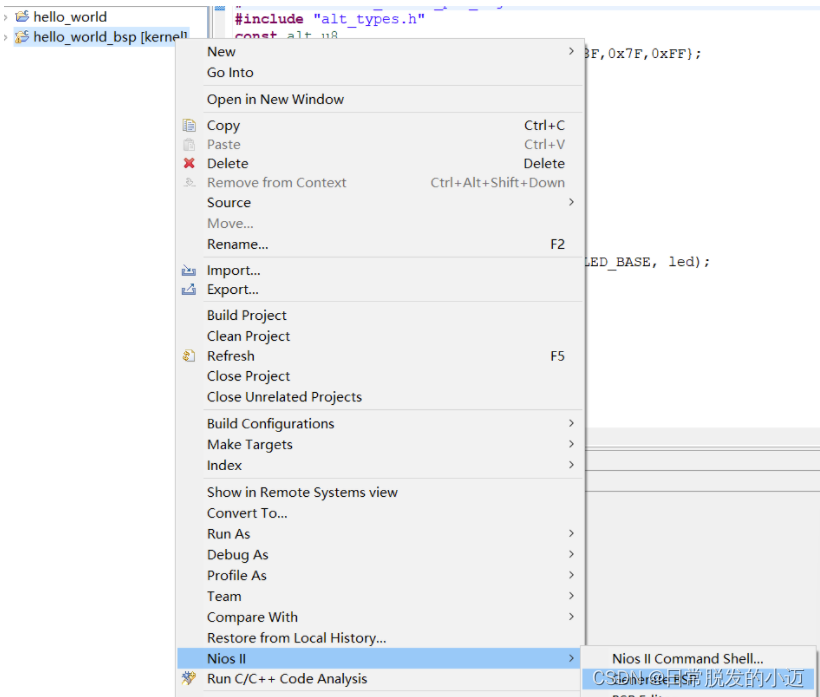

- 选择hello_wold_bsp,右键后,选择Nios II中的Generate BSP

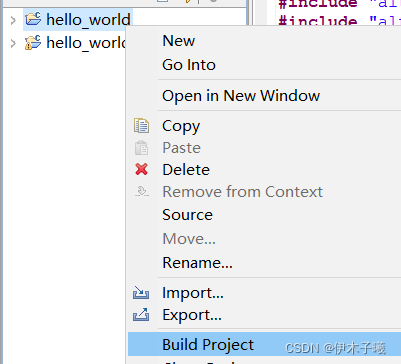

- 右键单击项目名称,在弹出的菜单中选择 Build Project

2.5 下载至开发板

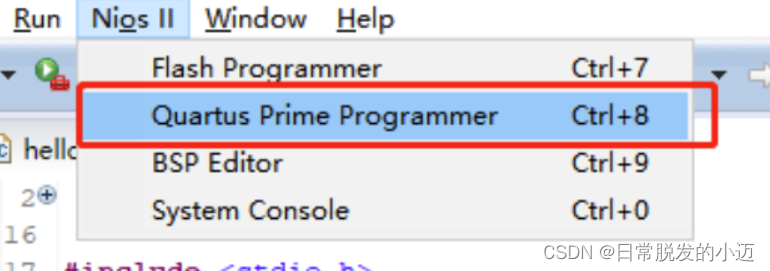

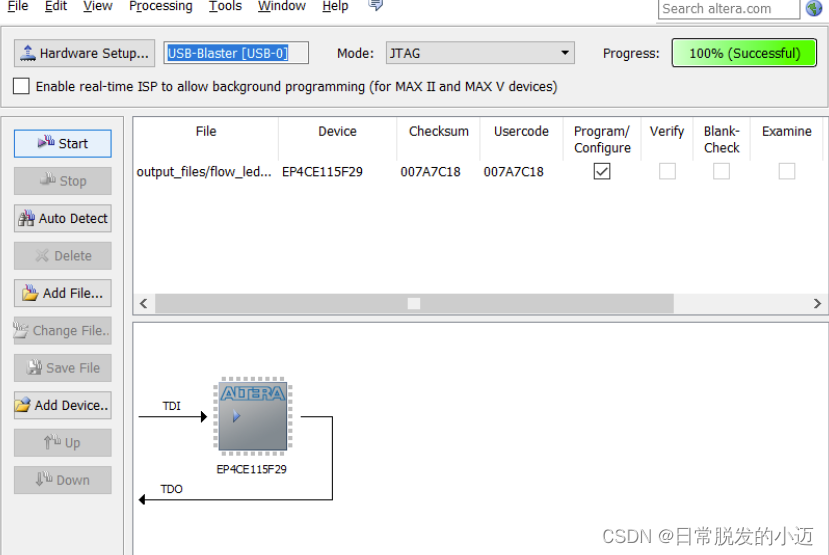

如下图所示,启动 Quartus Prime Prog

硬件下载

2.6 实现结果

流水灯实现结果如下

3 Verilog实现流水灯

3.1 硬件设计

硬件部分设计与上文第二部分内容相同,此处不做赘述

3.2 创建顶层文件

回到Quarters,选择New->Verilog HDL File

顶层文件内容

module hello_world(

input clk,

input reset_n,

output [3:0] led

);

//此处的代码可以通过Qsys中的Generate->Generate Example,复制里面的内容,粘贴到此处,进行相应的修改

system_qsys u0 (

.clk_clk (clk), // clk.clk

.reset_reset_n (reset_n), // reset.reset_n

.led_export (led) // led.export

);

endmodule

保存文件,并编译

3.3 引脚设置

菜单里选择 Assignments-device,点击 Device pin options

进行 unused pin 设置,可能会收到外部信号的干扰,将未用引脚设置为 As input tri-stated

特殊引脚设置如下图

编译完成后,分配管脚如下

3.4 软件设计

文件和工程的创建与上一部分相同,不做赘述

修改文件内容如下:

#include <stdio.h>

#include "system.h"

#include "altera_avalon_pio_regs.h"

#include "alt_types.h"

const alt_u8

led_data[4]={

0x01,0x03,0x07,0x0F};

int main (void) {

int count=0;

alt_u8 led;

volatile int i;

while (1)

{

if (count==4)

{

count=0;

}

else

{

count++;

}

led=led_data[count];

IOWR_ALTERA_AVALON_PIO_DATA(LED_BASE, led);

//延时的设置

i = 0;

while (i<5000000)

i++;

}

return 0;

}

总结

初次尝试NIOSII软核开发,实验本身并不困难,只是过程繁琐,需要仔细一点,花费较多时间。在进行kernel的连线时一定要仔细,不要连错,否则会导致后面的过程出错。

参考:

https://blog.csdn.net/qq_43279579/article/details/115917160

https://blog.csdn.net/weixin_41155462/article/details/121906230