一、硬件部分设计

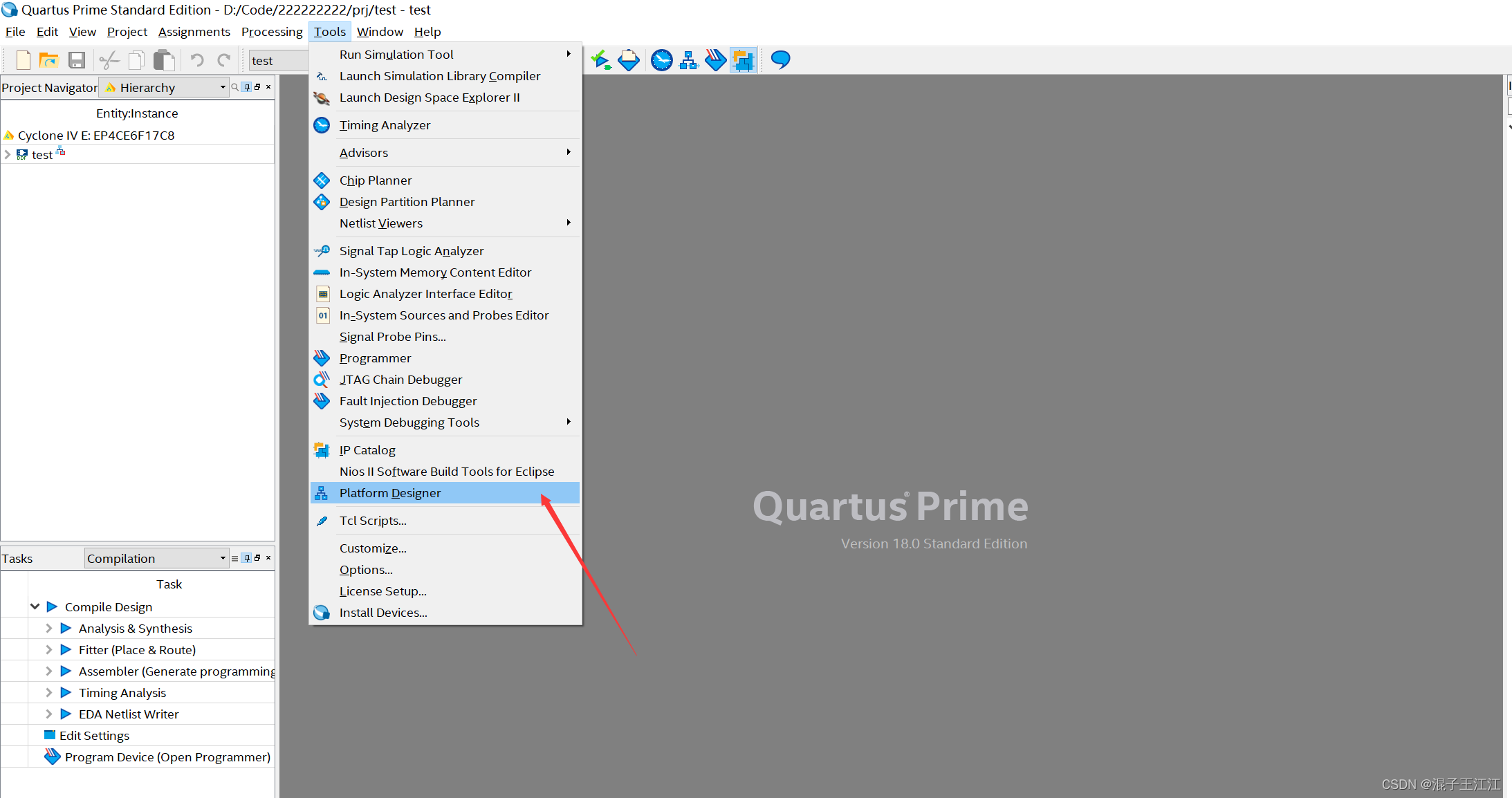

1、进行 Qsys 系统设计

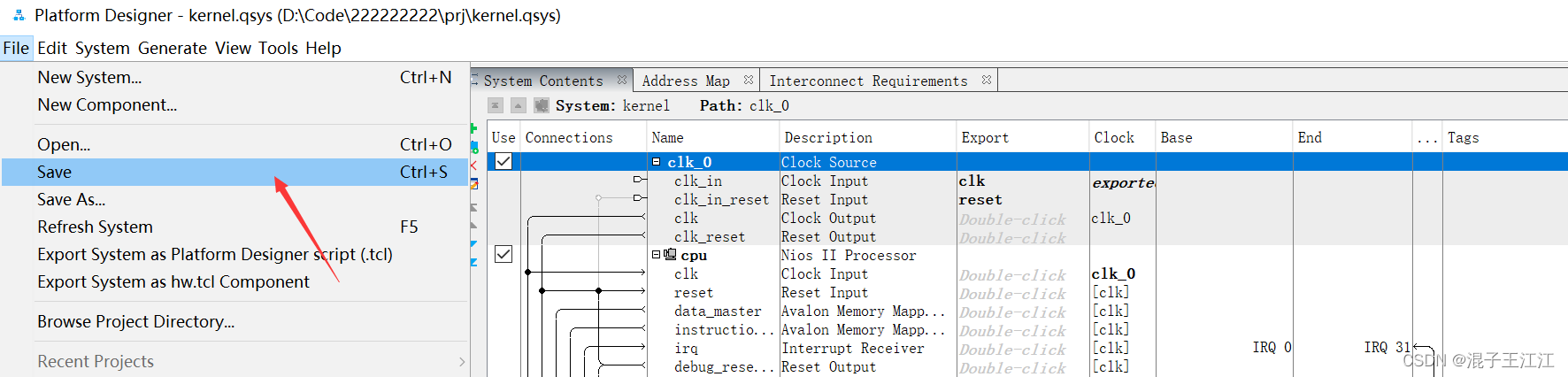

- 新建kernel.qsys文件:

- 设置clk时钟:

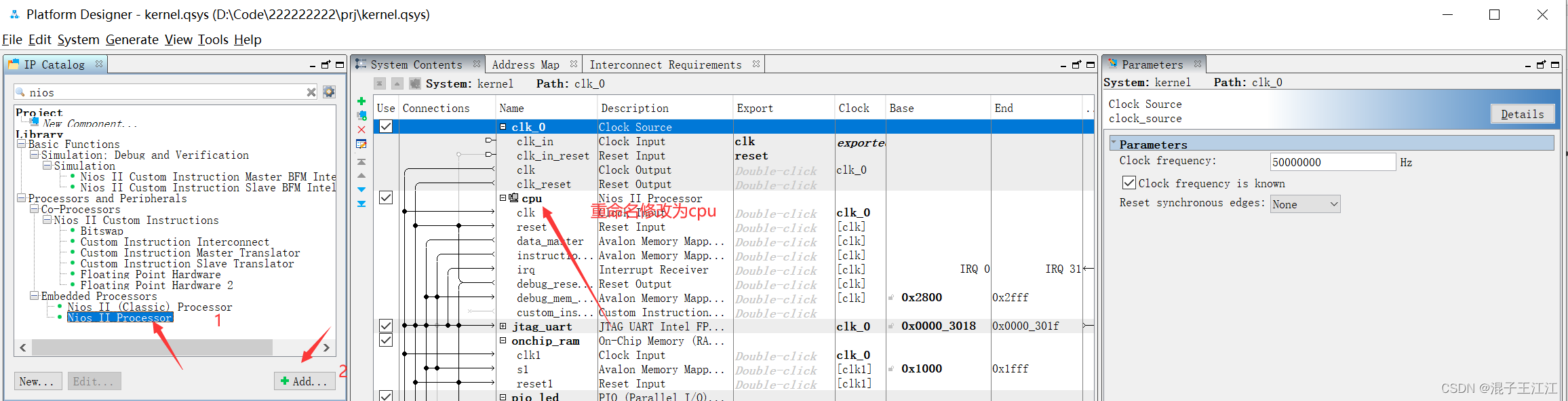

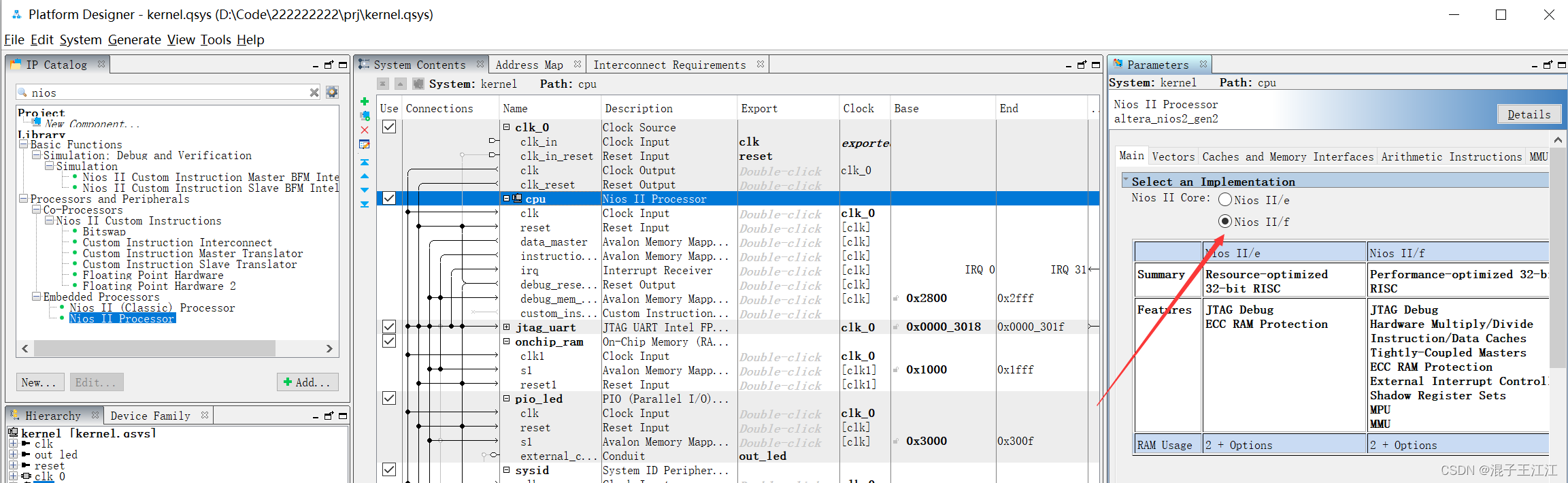

- 添加 Nios II

其余选项保持默认

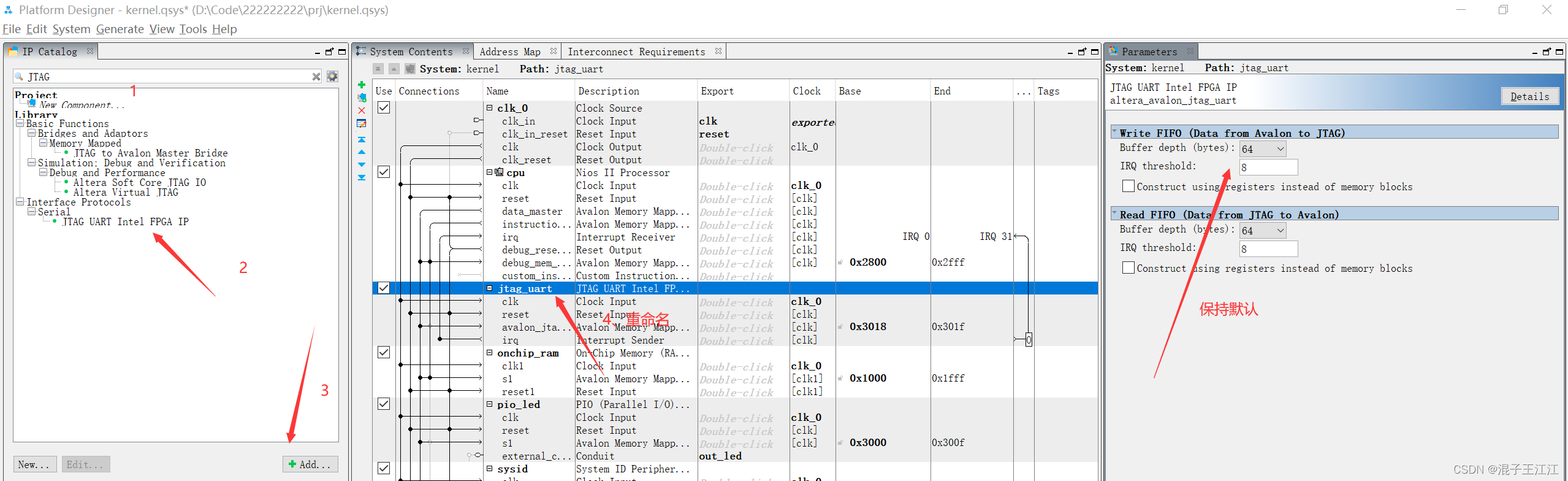

- 添加 jtag uart 接口

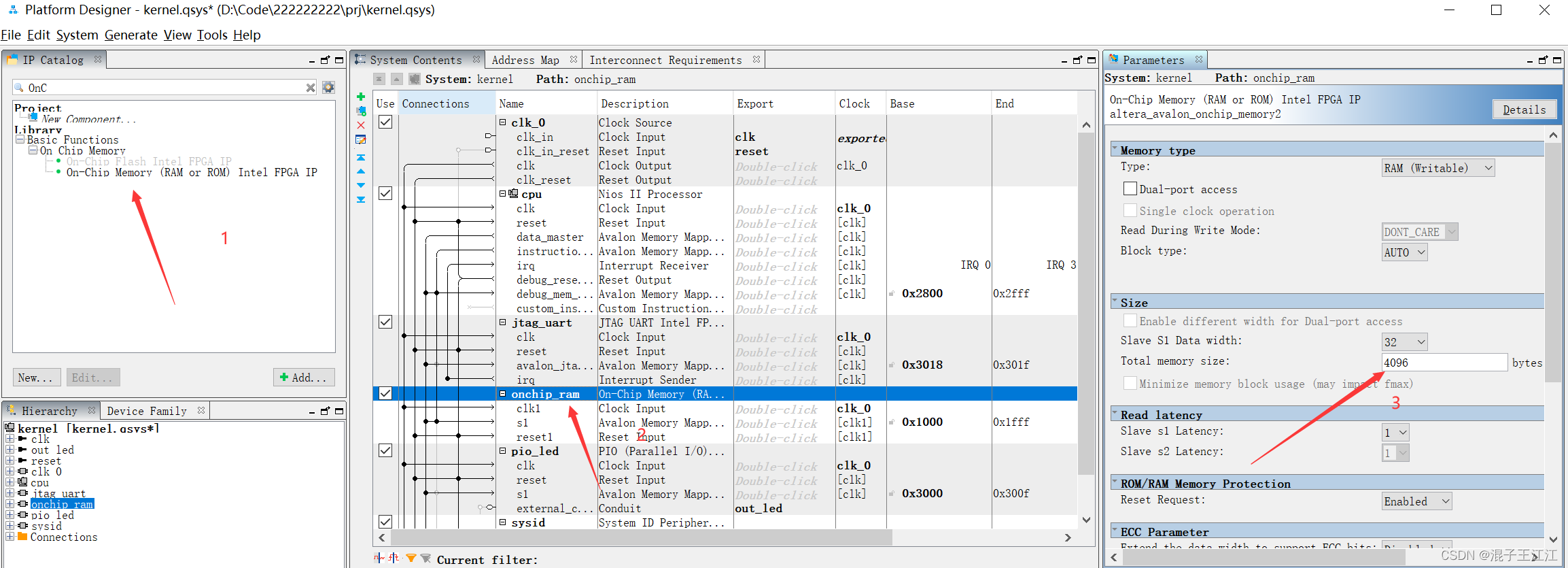

- 添加片上存储器 On-Chip Memory(RAM)核

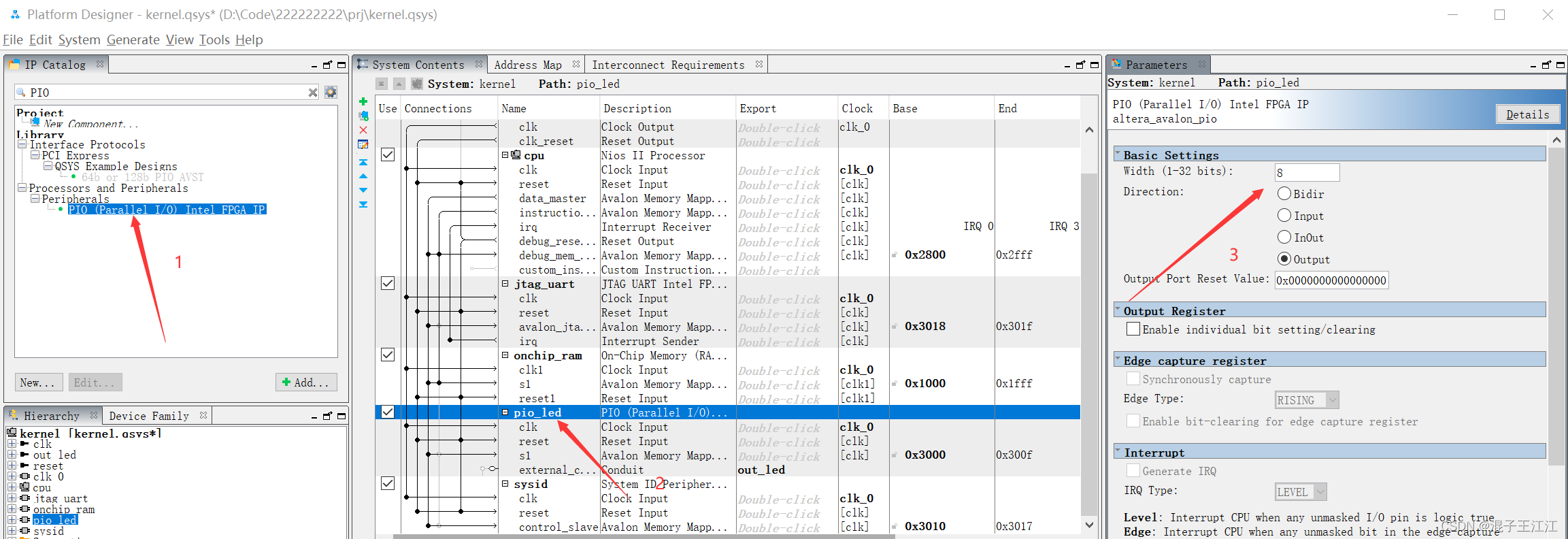

- 添加 PIO 接口

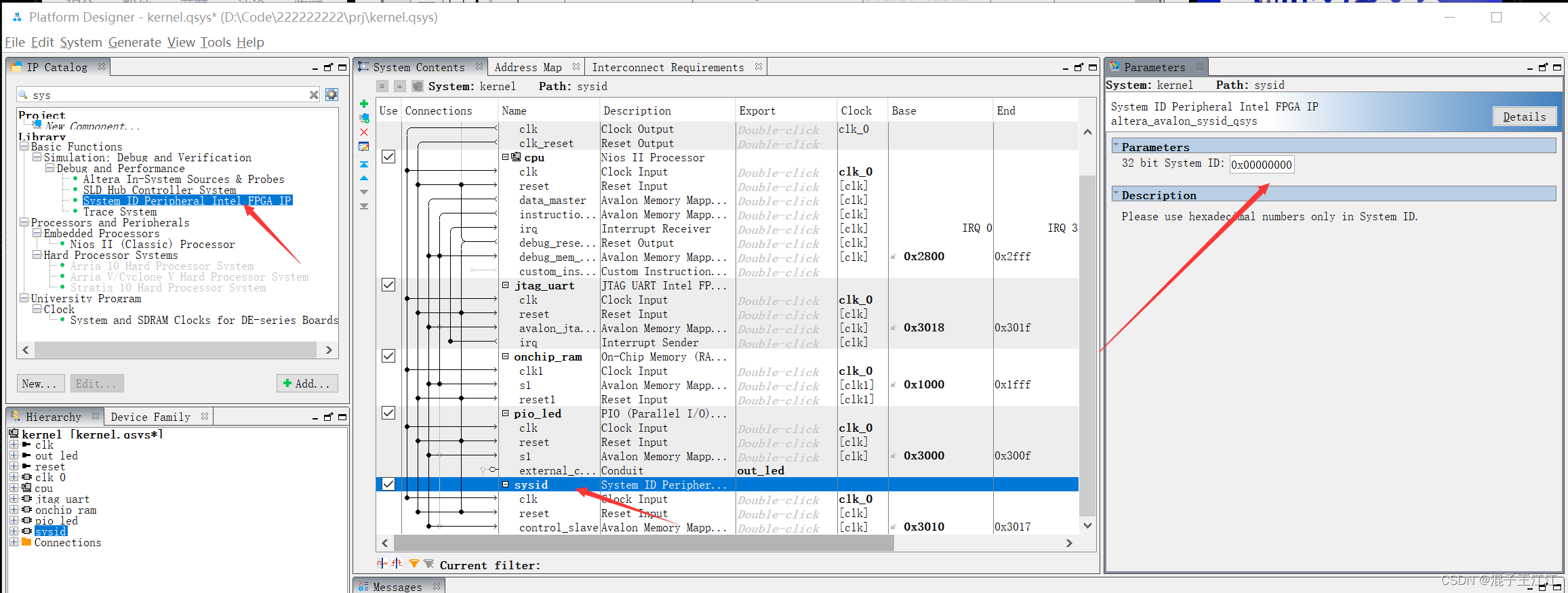

- 添加片 System ID Peripheral 核

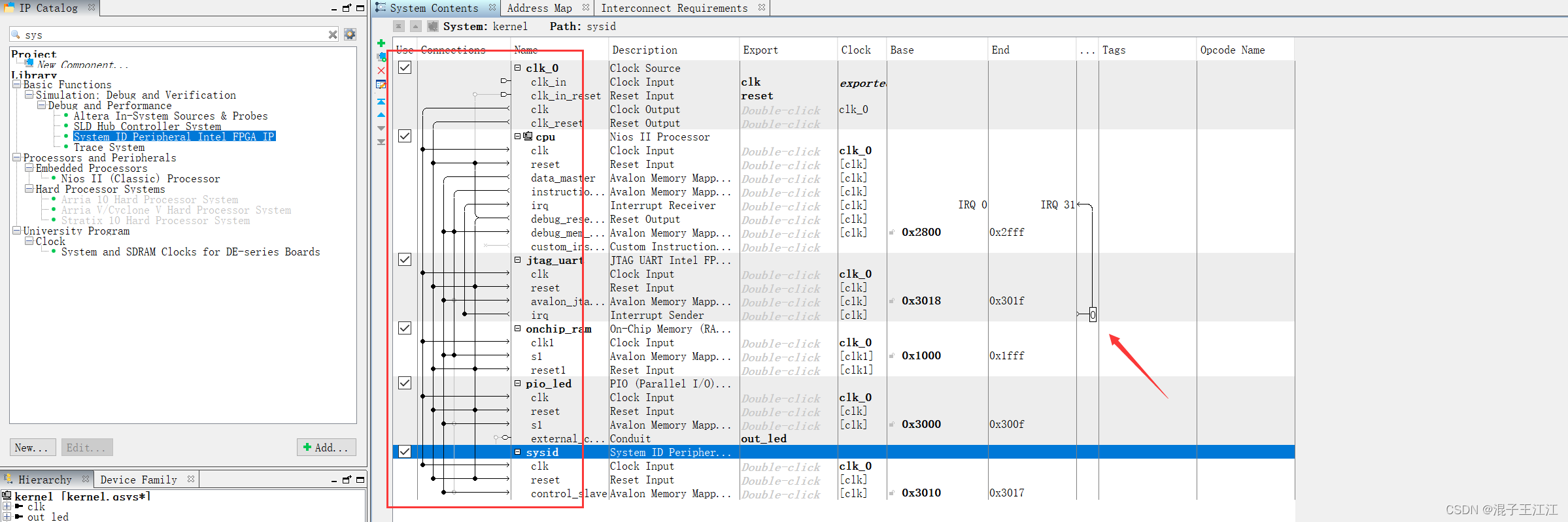

- 连线及中断:

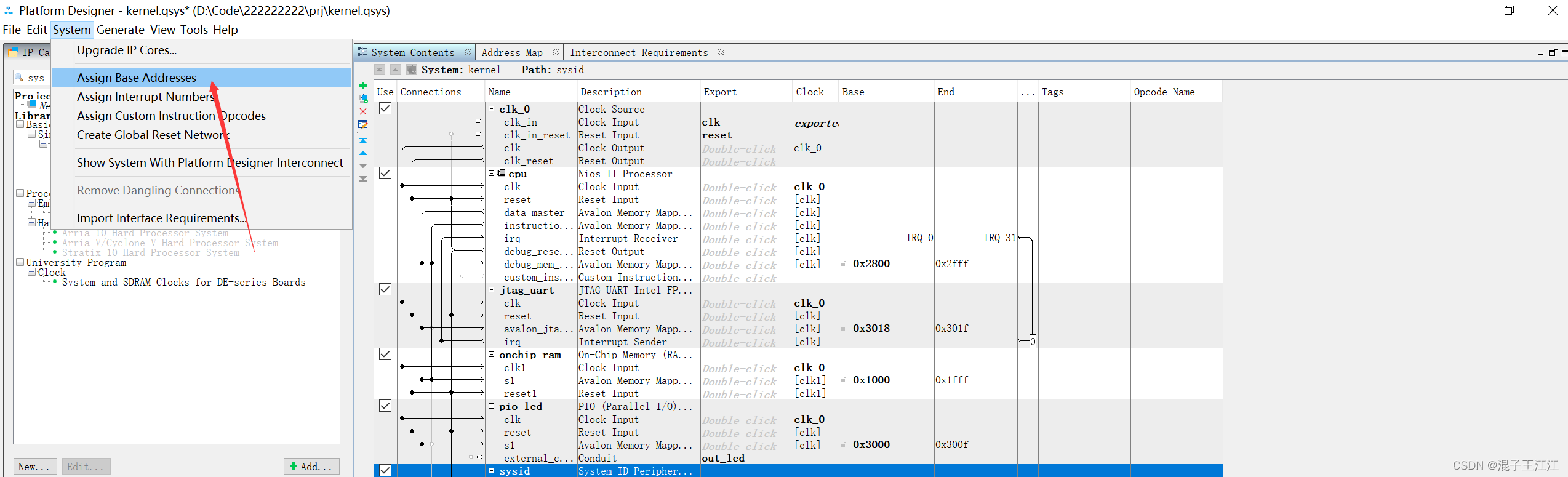

- 分配基地址:

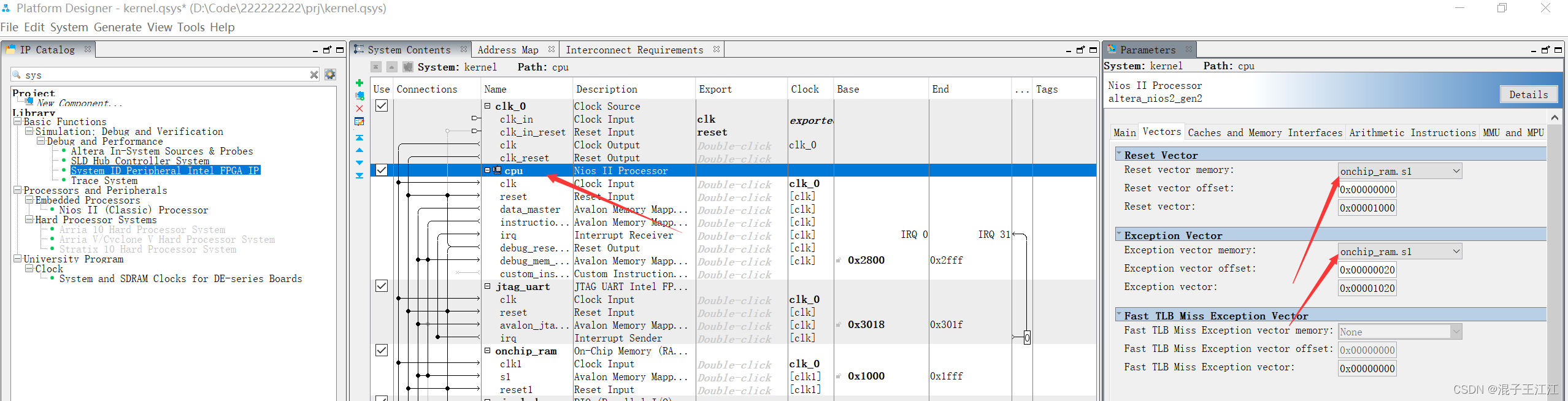

- 配置 Reset Vector 和 Exception Vector 为”onchip_ram.s1”

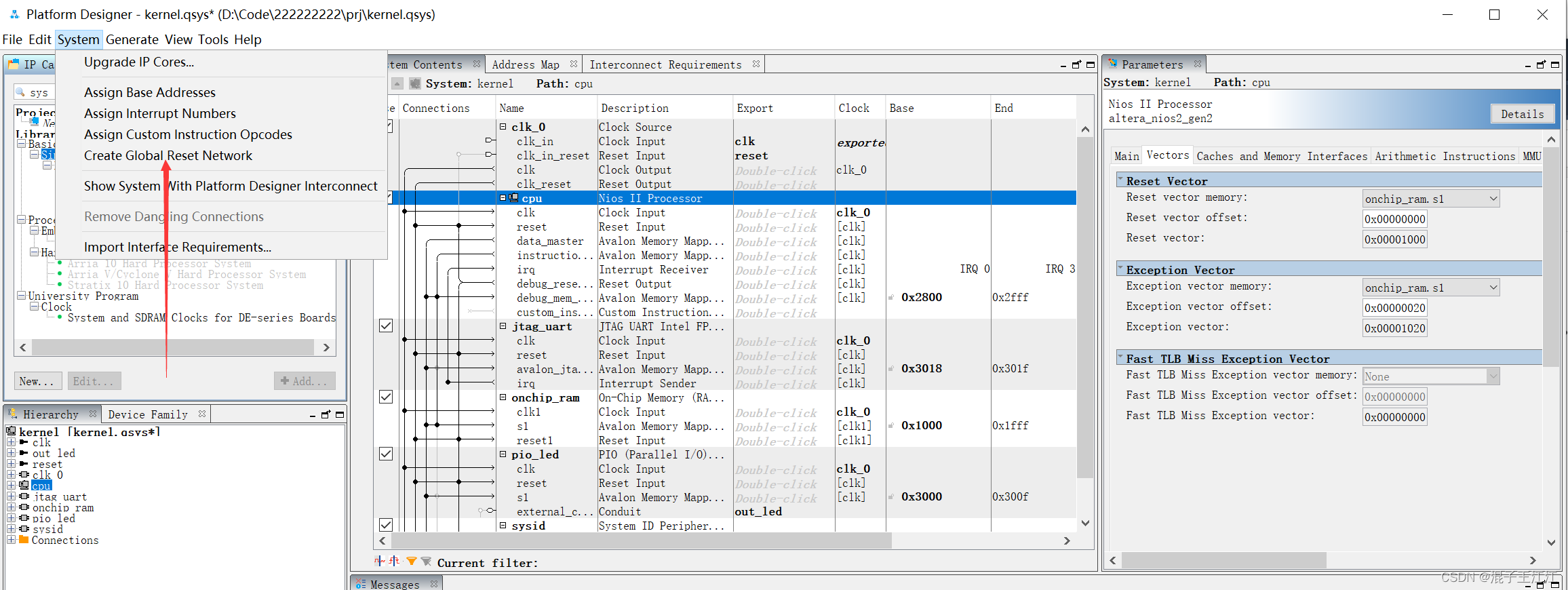

- 点击 Qsys 主界面菜单栏中的 ”System” 下的 ”Create Global Reset Network”。完成后会自动连接所有复位端口

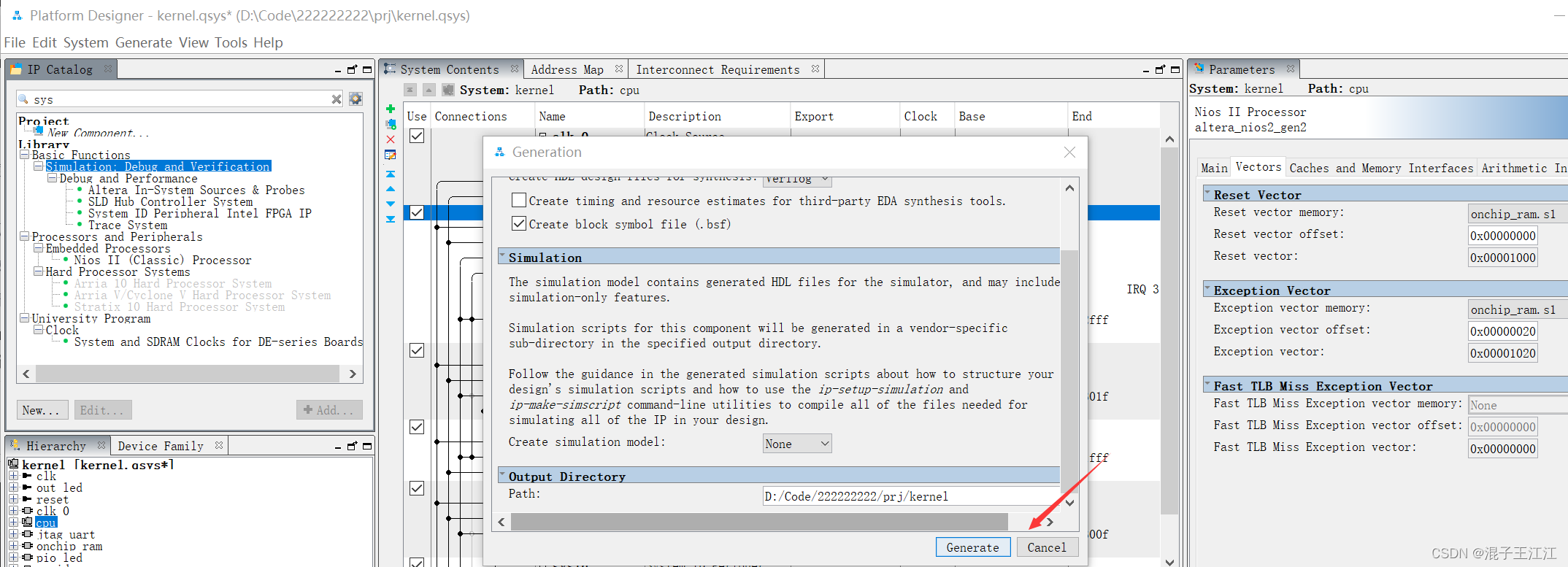

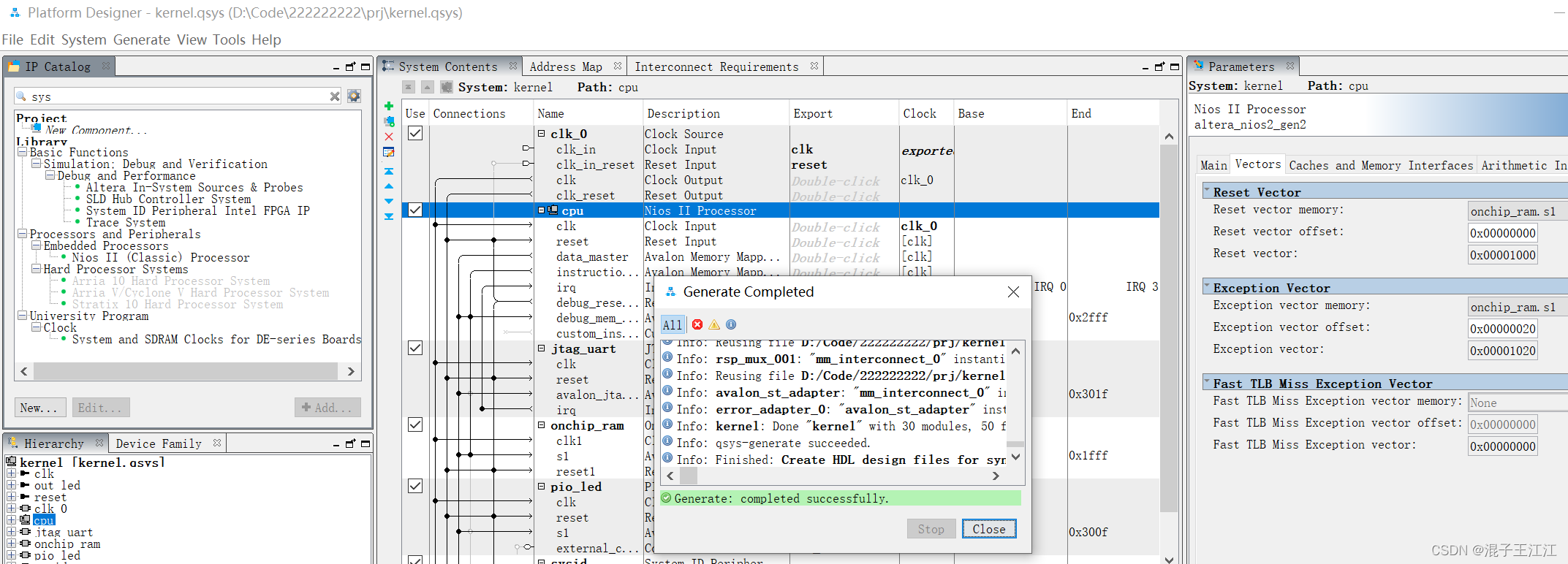

- 生成 Qsys 系统:点选 ”Generation HDL” 标签栏中 Generate 按钮生成 Qsys 系统,保存文件

依次关闭即可。

二、逻辑连接

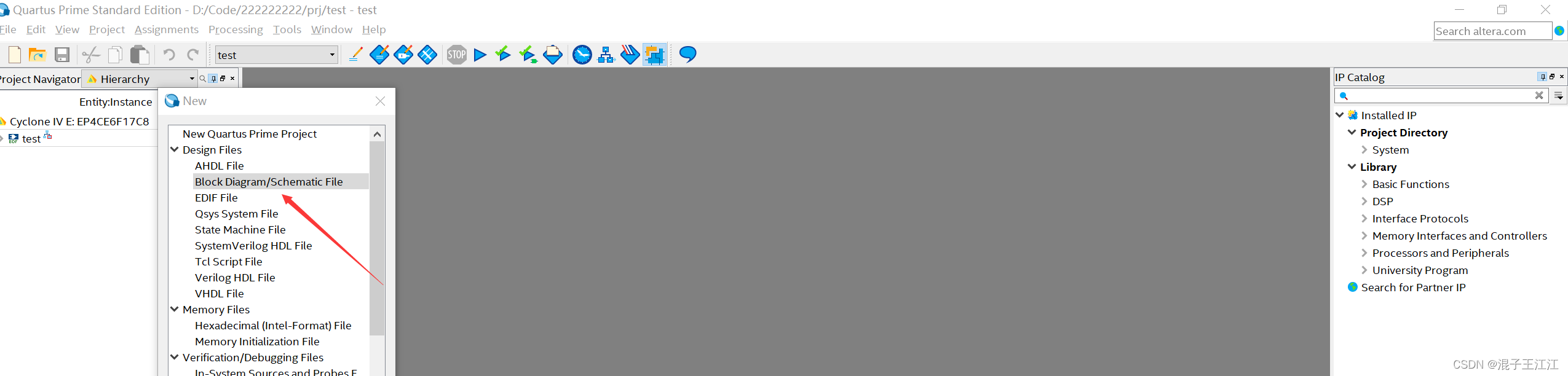

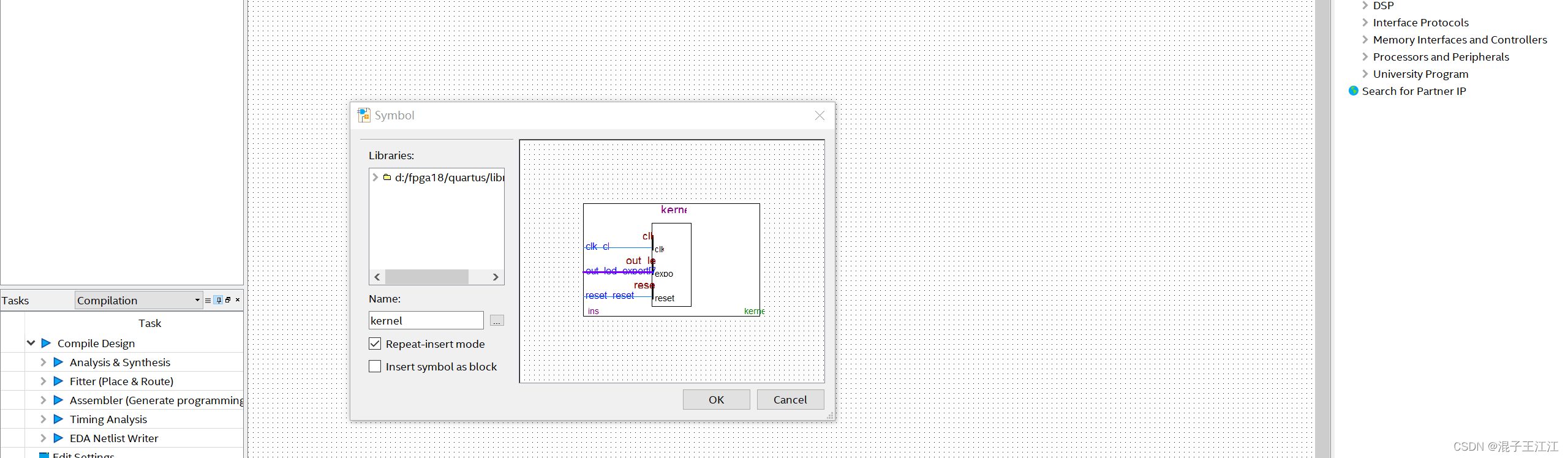

- 新建BDF文件,将设计好的系统符号引入

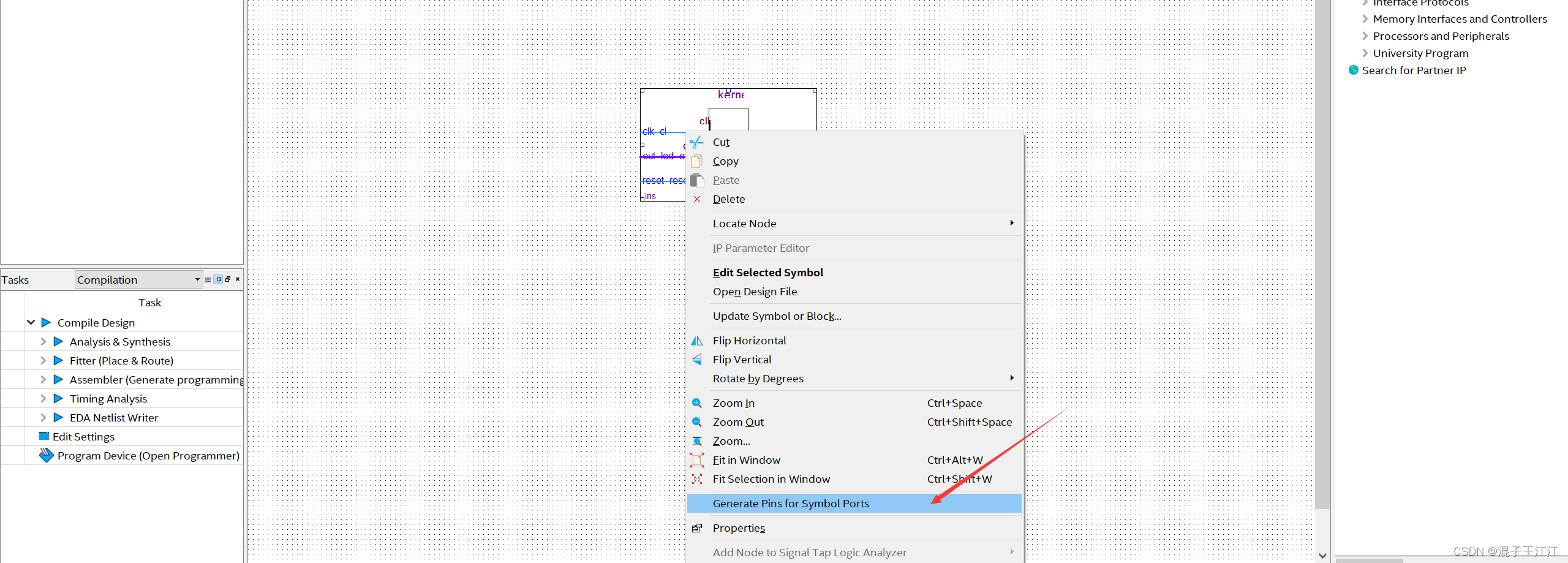

- 生成管脚:

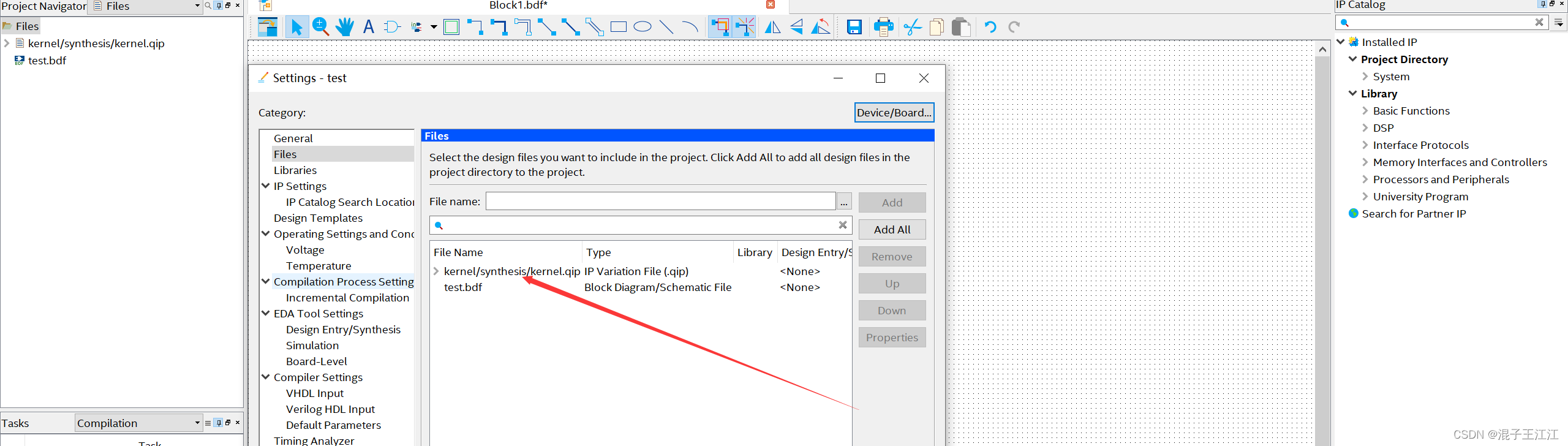

- 添加 kernel.qip 文件:

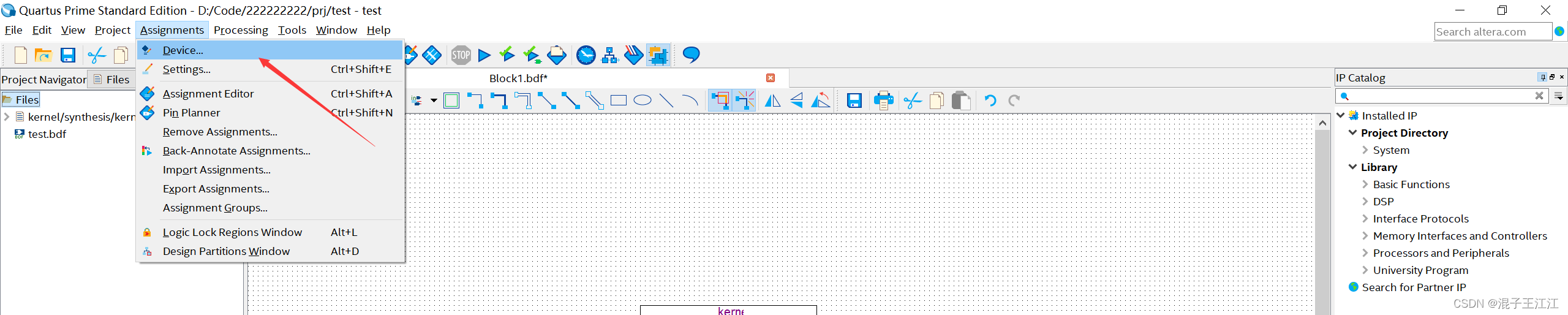

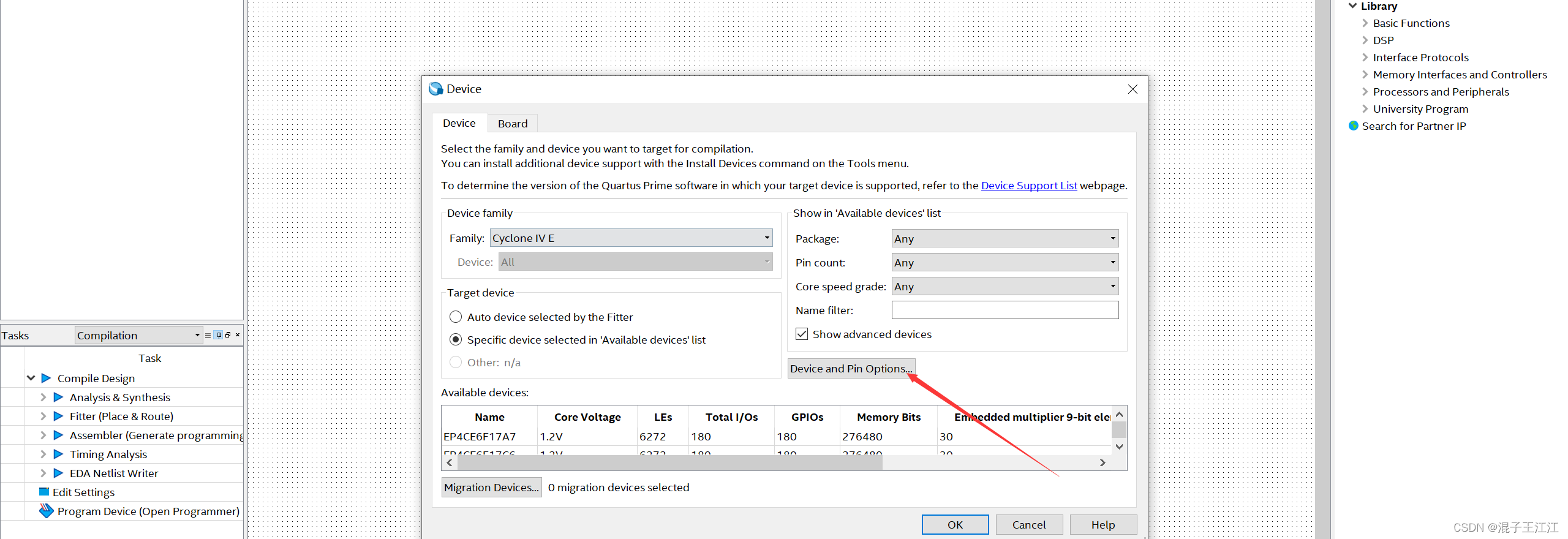

- 芯片引脚设置:

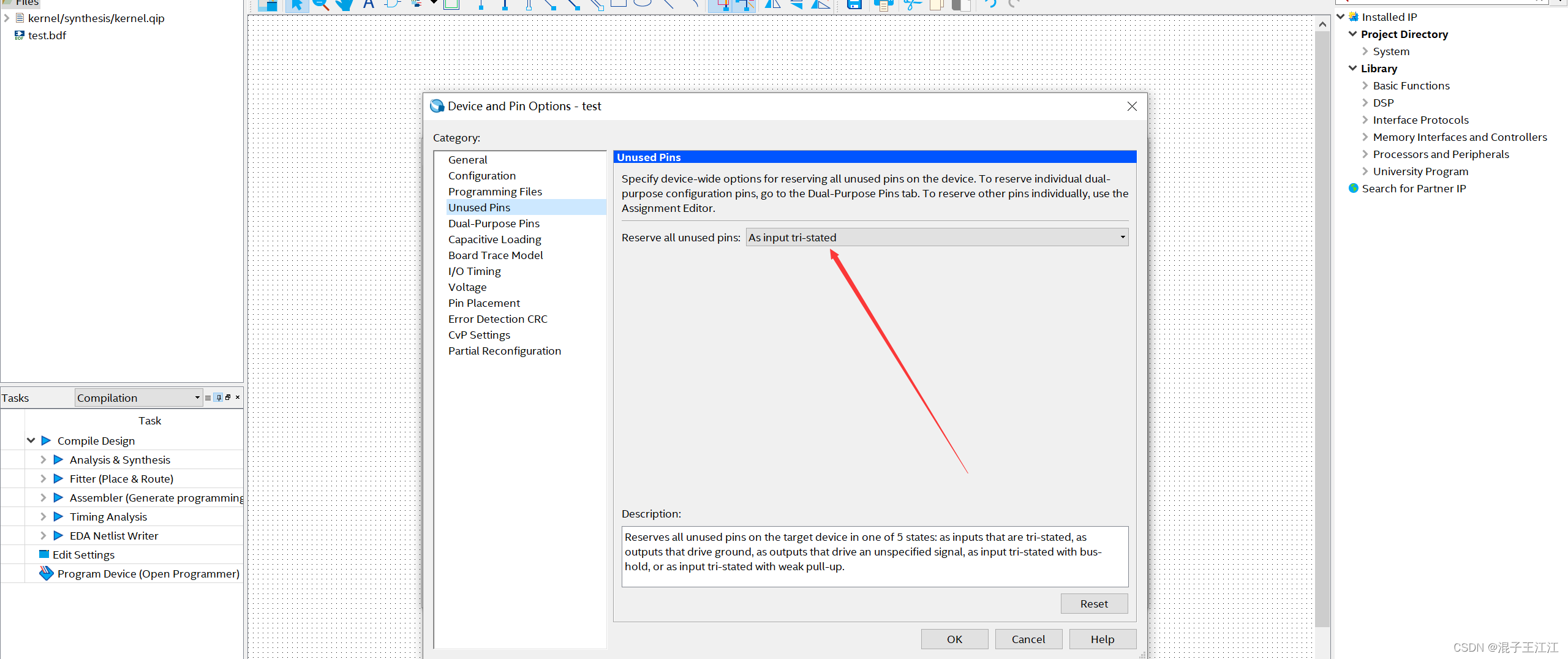

- 进行 unused pin 设置,可能会收到外部信号的干扰,将未用引脚设置为 As input tri-stated

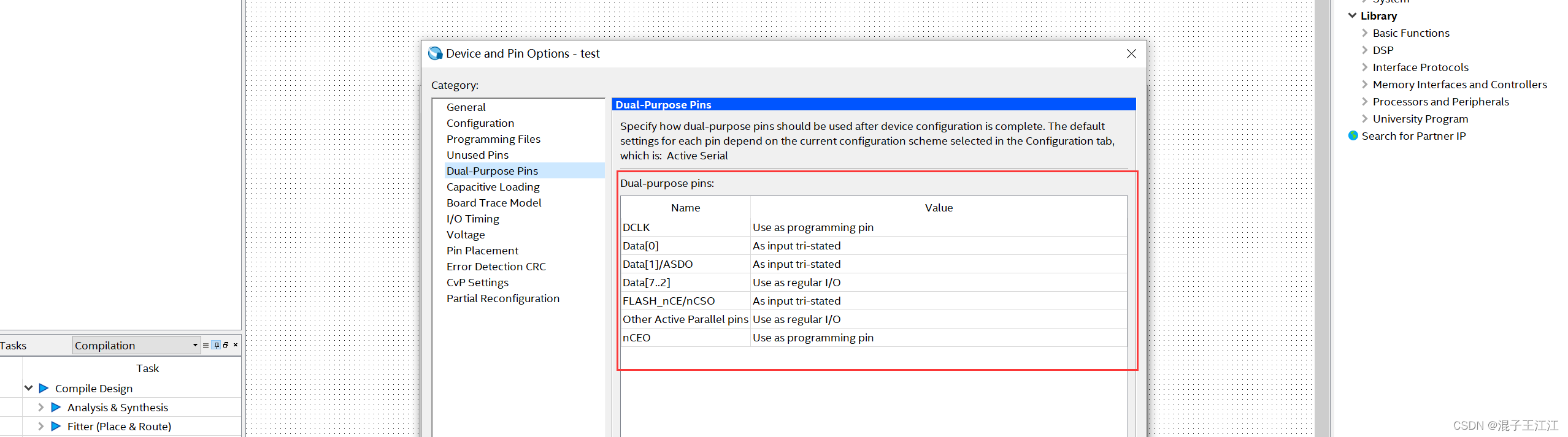

- 设为常规引脚

- 编译成功:

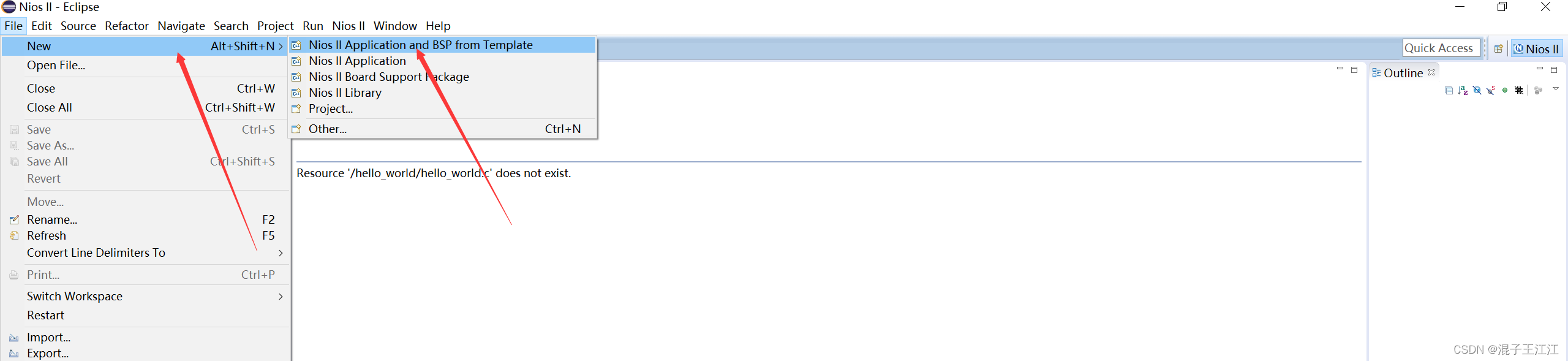

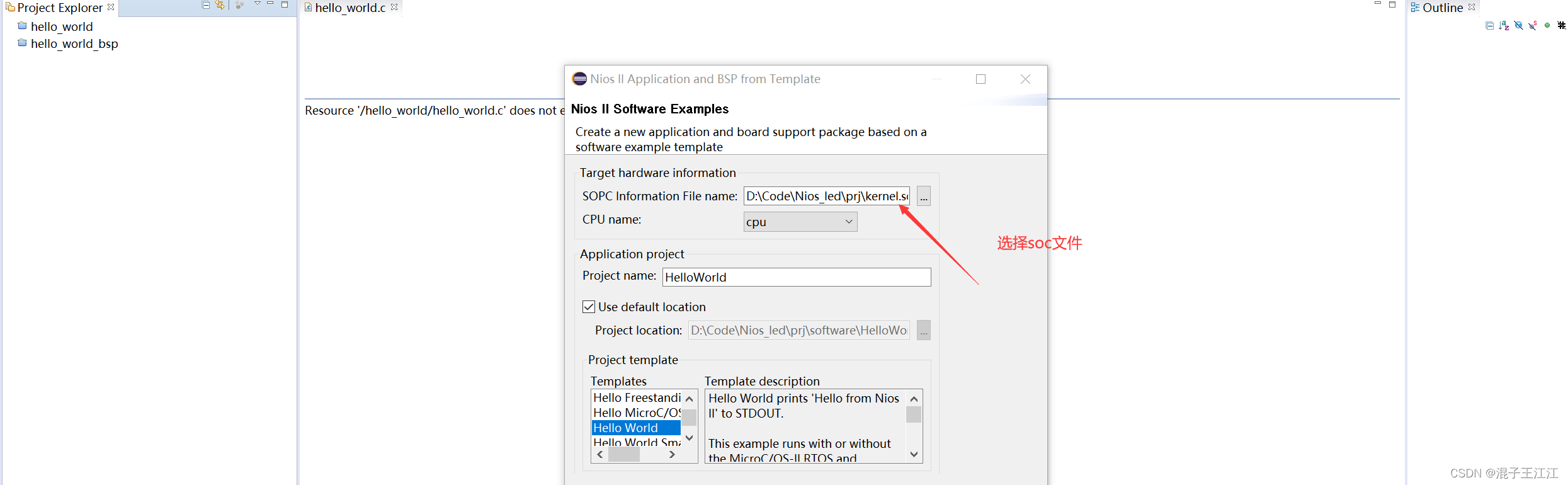

三、软件设计

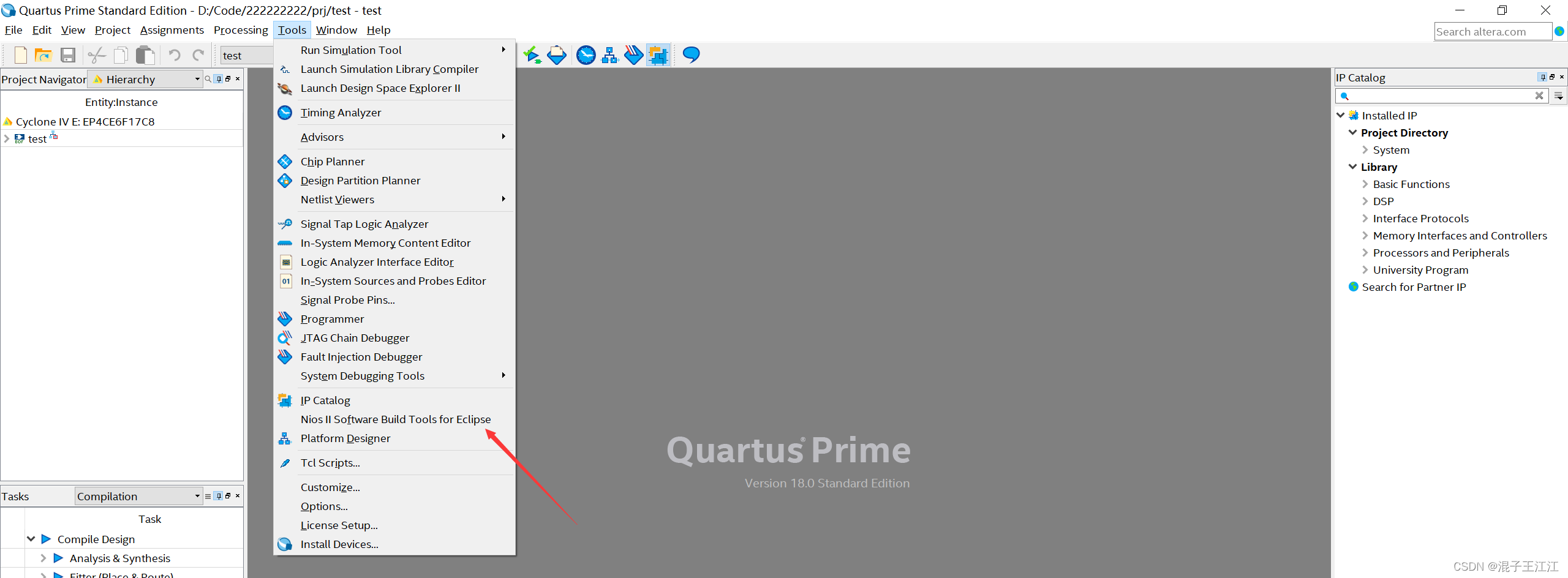

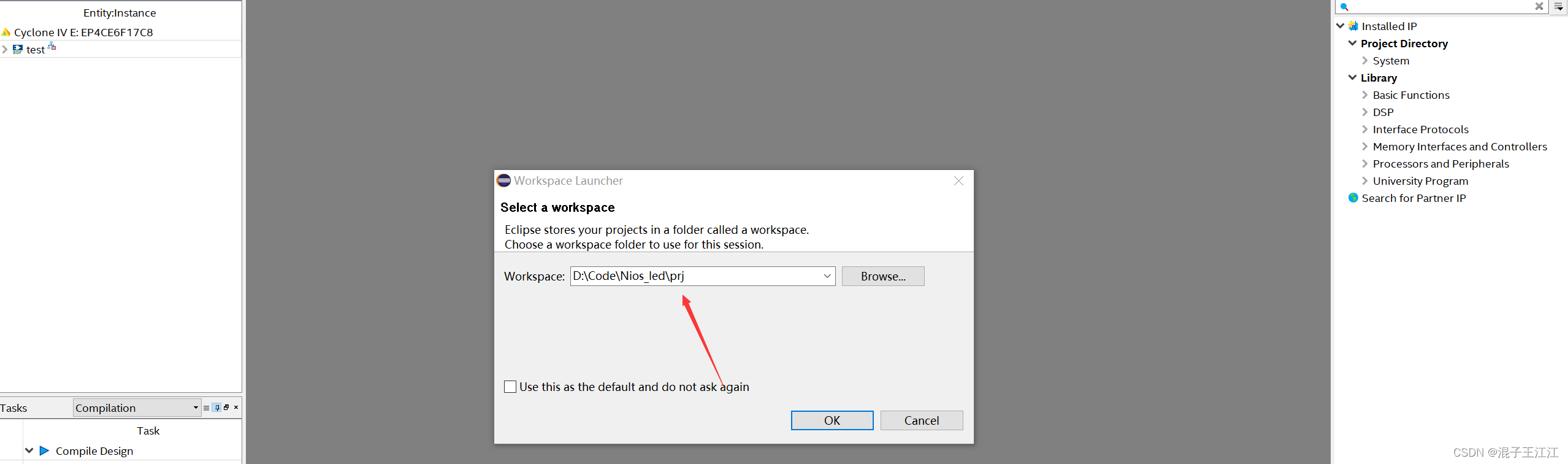

- 选择工程目录:

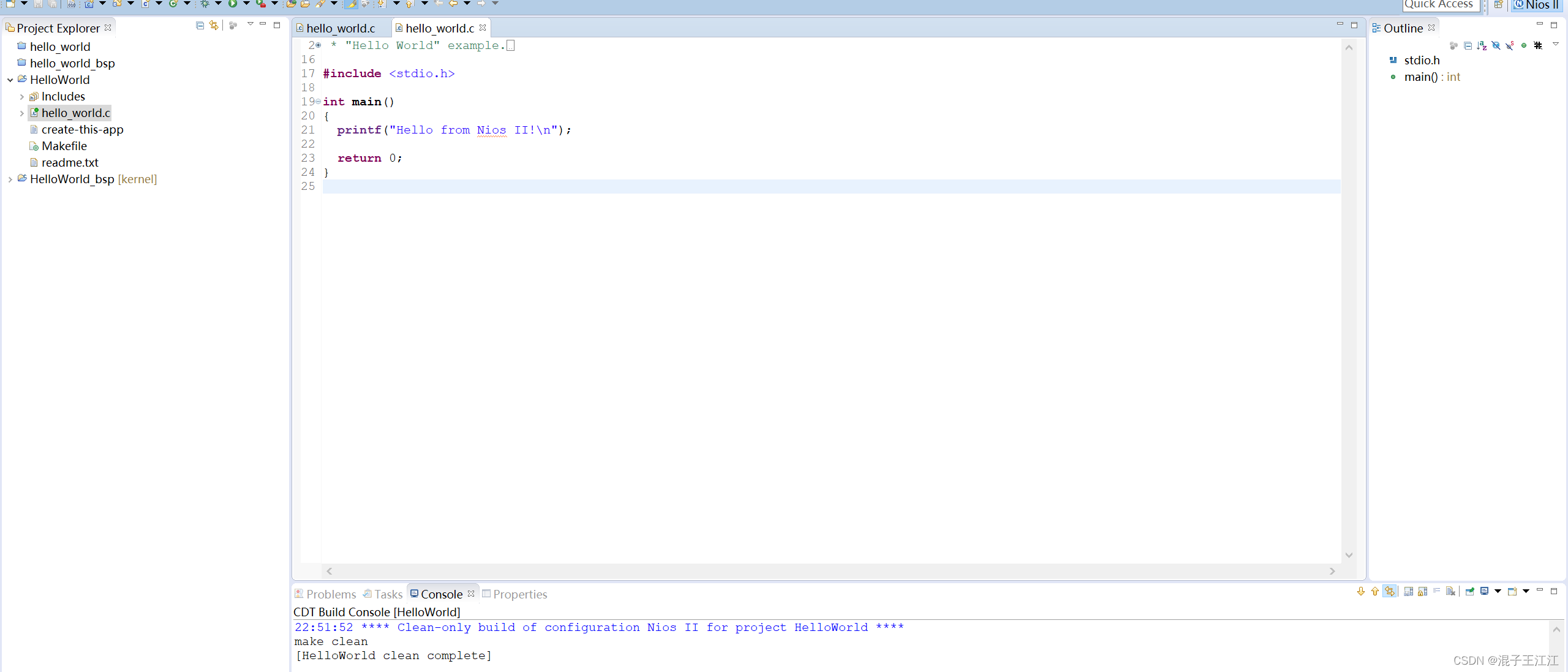

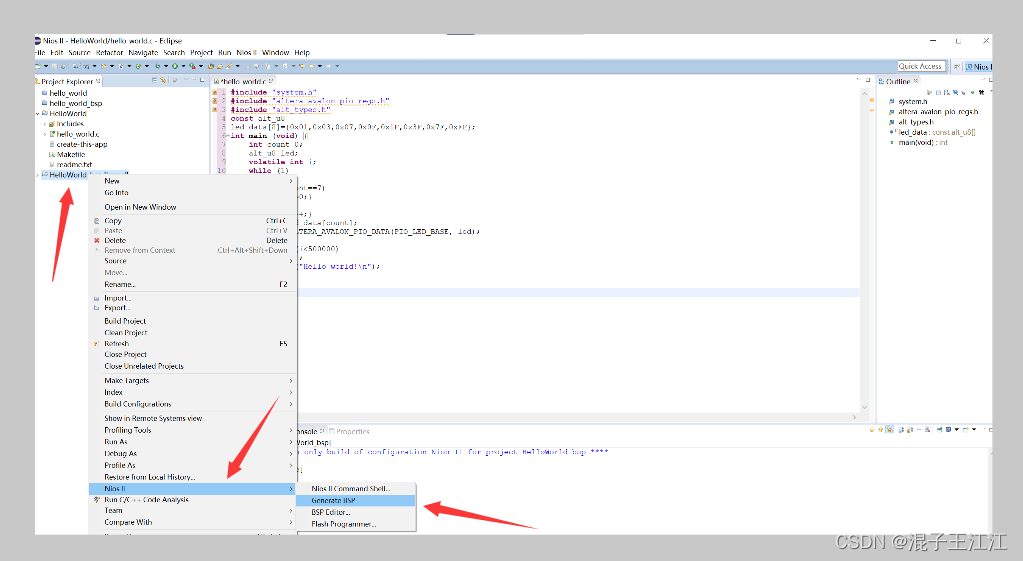

- 创建工程:

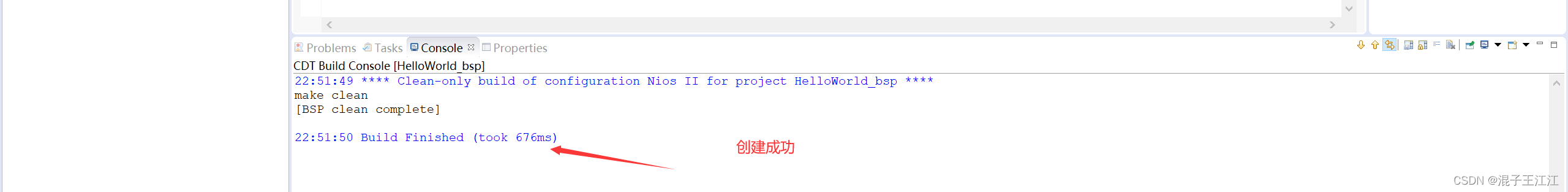

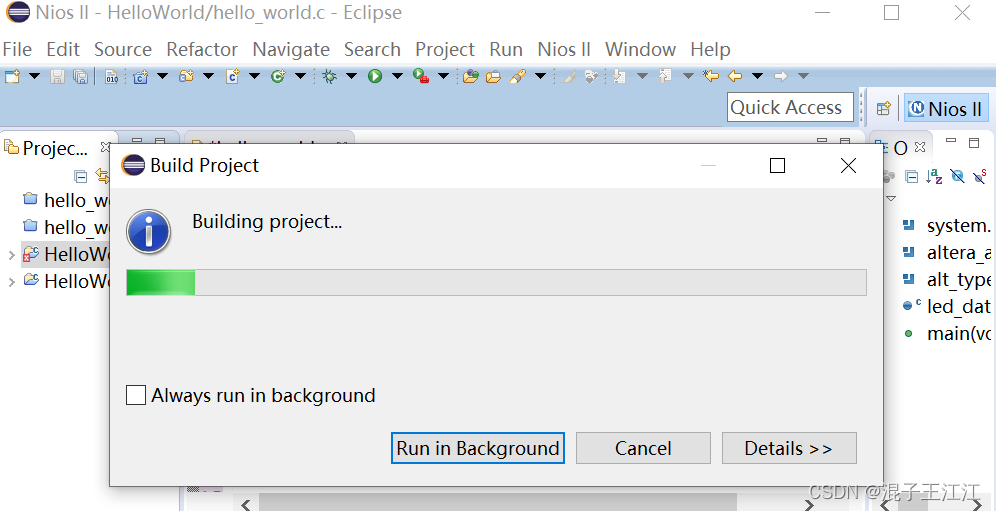

- 编译工程:

接下来就是下载到开发板进行测试即可。

四、总结

实验课上由于出现了特殊错误没有及时完成实验效果,没能上板进行验证,这次只能算是熟悉一下设计一个 NIOSII 软核的步骤。