基于Nios-II 软核的流水灯显示

目录

一、实验内容简述

1、实验目的

- 学习 Quartus-II 、Platform Designer、Nios-II SBT 的基本操作;

- 初步了解 SOPC 的开发流程,基本掌握 Nios-II 软核的定制方法;

- 掌握 Nios-II 软件的开发流程,软件的基本调试方法。

2、实验设备

硬件:PC 机、DE2-115 FPGA 实验开发平台;

软件:Quartus Prime 18.1、Platform Designer、Nios II SBT

3、实验内容

使用 FPGA 资源搭建一个简单 Nios II 处理器系统,具体包括:

(1) 在 Quartus Prime 中建立一个工程;

(2) 使用 PD 建立并生成一个简单的基于 Nios II 的硬件系统;

(3) 在 Quartus Prime 工程中编译基于 Nios II 的硬件系统并生成配置文件.sof;

(4) 在 Nios II SBT 中建立对应硬件系统的用户 C/C++工程,编写一简单用户程序,在Nios II SBT 中编译程序生成可执行文件.elf;

(5) 将配置文件.sof 和可执行文件.elf 都下载到 FPGA 进行调试运行。

4、实验原理

控制 LED 灯闪烁的用户程序代码很小,可将其固化在片内 ROM 来执行。变量、堆栈等空间使用片内 RAM,不使用任何片外存储器。

二、硬件部分设计

建立新项目

步骤可参考

基于Quartus-II的全加器设计.

这里为节约篇幅就省略了。

界面如图

1、进行Qsys设计

点击Tools下方的Qsys;

出现如示界面

点击file—>save,在文件名中填写kernel后保存

鼠标放置clk_0处右键Edit或双击,对clock进行时钟设置

添加 CPU 和外围器件。从 PD 的元件池中选择以下元件加入到当前设计的系统中:Nios II 32-bit CPU、jtag uart、片上存储器、PIO、system ID。

添加 Nios II 32-bit CPU

a. 在“library”标签栏中找到“Nios II Processor”或在查找窗口输出 nios 即可

点击 Add后界面如示

在Nios Core栏中选择NiosII/f选项其他保持默认

在“Caches and Memory Interfaces”标签栏中保持默认设置(Instruction Cache选择4Kbytes)

在“Advanced Features”标签栏中保持默认设置

在“MMU and MPU Setting”标签栏中保持默认设置

在“JTAG Debug Module”标签栏中保持默认设置(注意勾选“Include JTAG Debug”)

点击finish回到FD界面

将 nios2_qsys_0 重命名为 cpu,点击”Rename”即可重新命名

将 cpu 的 clk 和 reste_n 分别与系统时钟 clk_0 的 clk 和 clk_reset 相连

注意:对模块命名要遵循以下规则:

- 名字最前面应该使用英文;

- 能使用的字符只有英文字母、数字和下划线“_”;

- 不能连续使用“”符号,在名字的最后也不能使用“”。

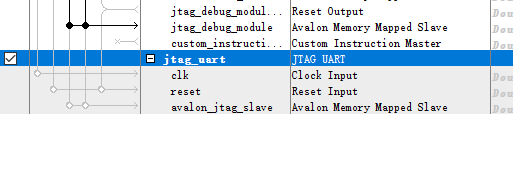

添加 jtag uart 接口。(可实现在 PC 主机与 Qsys 系统之间进行串行字符 流通信。)

保持默认选项,点击finish

在”Name”列中将 jtag-uart_0 重命名为 jtag-uart

进行 clk、reset 以及 master-slave 的连线,

进行中断 irq 连线

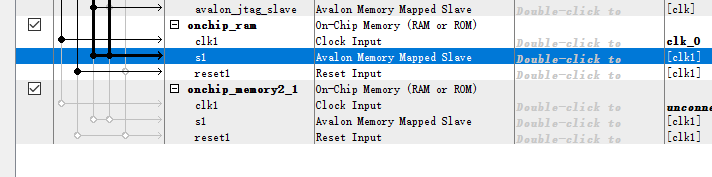

添加片上存储器 On-Chip Memory(RAM)核

在”Size”栏中的”Total memory size”窗口中输入 40960(即片上内存的大小为 40KB),其余选项保持默认,点击 Finish

在”Name”列中将 onchip_memory2_0 改名为 onchip_ram

进行时钟、数据端口、指令端口的连接

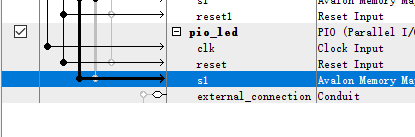

添加 PIO 接口

确定以下选项:Width 为 8bits,Direction 选择 output,其余选项保持默认,点击Finish

在”Name”列中将pio_0 改名为 pio_led。并在在 Export 栏处双击,把输出口引出来,并命名为 out_led

进行时钟、数据端口、指令端口的连接

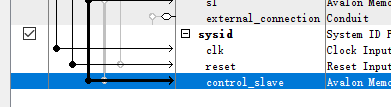

添加片 System ID Peripheral 核

保持默认选项,单击 Finish

注:之前在 SOPC Builder 中 System ID 是自动生成的,但是PD(Qsys )里已经不再自动生成。在 System ID 中可以输入一个 32 位的十进制整数值,保持 0 当然也可以。

在”Name”列中将 sysid_qsys_0 改名为 sysid

进行时钟、数据端口的连接

2、Qsys设计的后续

基地址分配:点击 PD 主界面菜单栏中的”System”下的”Assign Base Addresses”

完成后”Base”栏将出现不会重复的具体的地址

分配中断号:在”IRQ”标签栏下点选”Avalon_jtag_slave”和 IRQ 的连接点就会为”jtag_uart”核添加一个值为 0 的中断号

指定 NIos II 的复位和异常地址:从”System Contents”标签栏双击建立好的 cpu 进入 Nios II Processor 的配置界面,配置 Reset Vector 和 Exception Vector 为””onchip_ram.s1”,点击 Finish

点击 Qsys 主界面菜单栏中的”System”下的”Create Global Reset Network”。完成后会自动连接所有复位端口

最终完成的连接图(注意仔细对照节点,避免出错,以保证后续的正常进行)

生成 Qsys 系统:点选”Generation HDL”标签栏中 Generate 按钮生成 Qsys 系统

出现如示窗口

点击 Close 后关闭窗口后,再关闭 Platform Designer 主界面。

3、原理图设计

新建原理图文件

点击添加元件,放置创建的PD文件

加入 Quartus II IP File 文件,为了以后编译成功,请务必将对应的 Quartus II IP File (.qip) 加入项目中;

①点击 Assignments-Settings,添加 kernel.qip 文件

加入 kernel.qip 文件

至此 Qsys 组件构建完成。

4、进行逻辑连接和生成管脚

逻辑连接。开发板晶振为 50M,与系统默认一致,因此,这里我们不需要修改;

在 kernel 模块内点击鼠标右键选取 Generate Pin for Symbol Ports 生成管脚;

将管脚”inclk0”改名为 clock,管脚”reset_reset_n”改名为 reset_n,

管脚 out_led_export[7…0]改为 out_led[7…0]

5、芯片引脚设置

选择 Assignments-device,然后如下图所示点击 Device pin options。

进行 unused pin 设置,可能会收到外部信号的干扰,将未用引脚设置为 As input tri-stated

特殊引脚设置,设置为常规引脚

6、编译工程

回到 Quartus II 主界面后编译项目。如下图所示,编译成功后,点击 OK 完成

编译结果

分配物理针脚

按照开发板提供的管脚名称分配针脚

完成后关闭 Pin Planner,回到 Quartus Prime 主界面后再次编译项目。至此完成项目的硬件设计。

三、软件部分设计

1、启动 Nios II SBT

点击 Nios II Software Build Tools for Eclipse 打开 Nios II SBT for

Eclipse

选择当前目录,点击OK

出现 Nios II SBT for Eclipse 主界面

2、创建工程

建立新的软件应用

点击后出现下图,在”SOPC Information File name”窗口中选kernel.sopcinfo 文件,以便将生成硬件配置信息和软件应用关联,CPU 栏会自动选择”CPU”。在”Project name”输入”hello_world,”Project template”选择 Hello_World。点击 Finish。

系统会自动生成一个打印“hello_world”的软件工程,在 hello_world.c 中我们可以看到相应代码

#include <stdio.h>

int main()

{

printf("Hello from Nios II!\n");

return 0;

}

3、修改程序

在 hell_word.c 里修改流水灯控制程序

#include <stdio.h>

#include "system.h"

#include "altera_avalon_pio_regs.h"

#include "alt_types.h"

const alt_u8

led_data[8]={

0x01,0x03,0x07,0x0F,0x1F,0x3F,0x7F,0xFF};

int main (void) {

int count=0;

alt_u8 led;

volatile int i;

//串口打印

printf("Hello world!\n");

//流水灯循环

while (1)

{

if (count==7)

{

count=0;

}

else

{

count++;

}

led=led_data[count];

IOWR_ALTERA_AVALON_PIO_DATA(PIO_LED_BASE, led);

//延时的设置

i = 0;

while (i<5000000)

i++;

}

return 0;

}

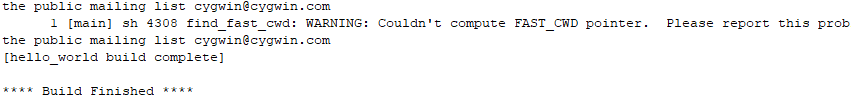

编译项目

编译结果

4、运行项目

连接 JTAG 到开发板,确定 A.已正确安装驱动。B. 防火墙不会影响到 JTAG 的正常工作。最后给开发板上电。

启动 Quartus Prime Programmer

添加下载文件。然后点击 Start 开始下载,下载成过后关闭,回到 Eclipse 主机面

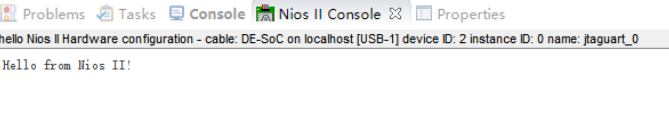

运行程序

注意,在目标板上运行程序前,要确保 USB Blaster 下载电缆已经连接好,要保证已经使用硬件系统对 FPGA 完成配置。

配置 Run Configurations,转到”Target Connection”标签栏,点击右侧的 Refresh Connections 将 USB-Blaster 加入

Apply 后,Run

5、实际结果

四、总结与参考资料

1、总结

对流水灯的开发原理有了一个简单了解。