软件版本:vivado 18.3

使用芯片:zynq 7020

7020中包含FPGA及ARM,在实际工程中,FPGA和ARM之间可进行数据传输,这种情况下,就需要PL和PS端进行联合调试,下面介绍其过程。

一、添加MARK DEBUG

选用MARK BDBUG语句进行ila观测。

首先,在想观察的信号前面添加(* MARK_DEBUG="true" *),这部分语句可添加在input或output的端口定义前,如下图:

![]()

也可以添加在后面的信号声明中,如下图:

![]()

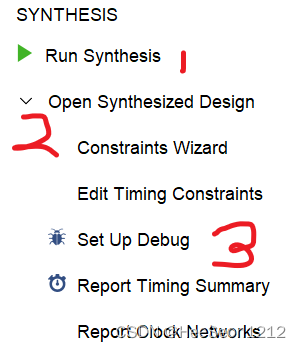

二、综合并set up debug

在.v文件添加完MARK DEBUG后,1、点击软件左侧界面的Run Synthesis;2、Synthesis完成后,展开open synthesis Design;3、双击Set up debug。

出现如下界面

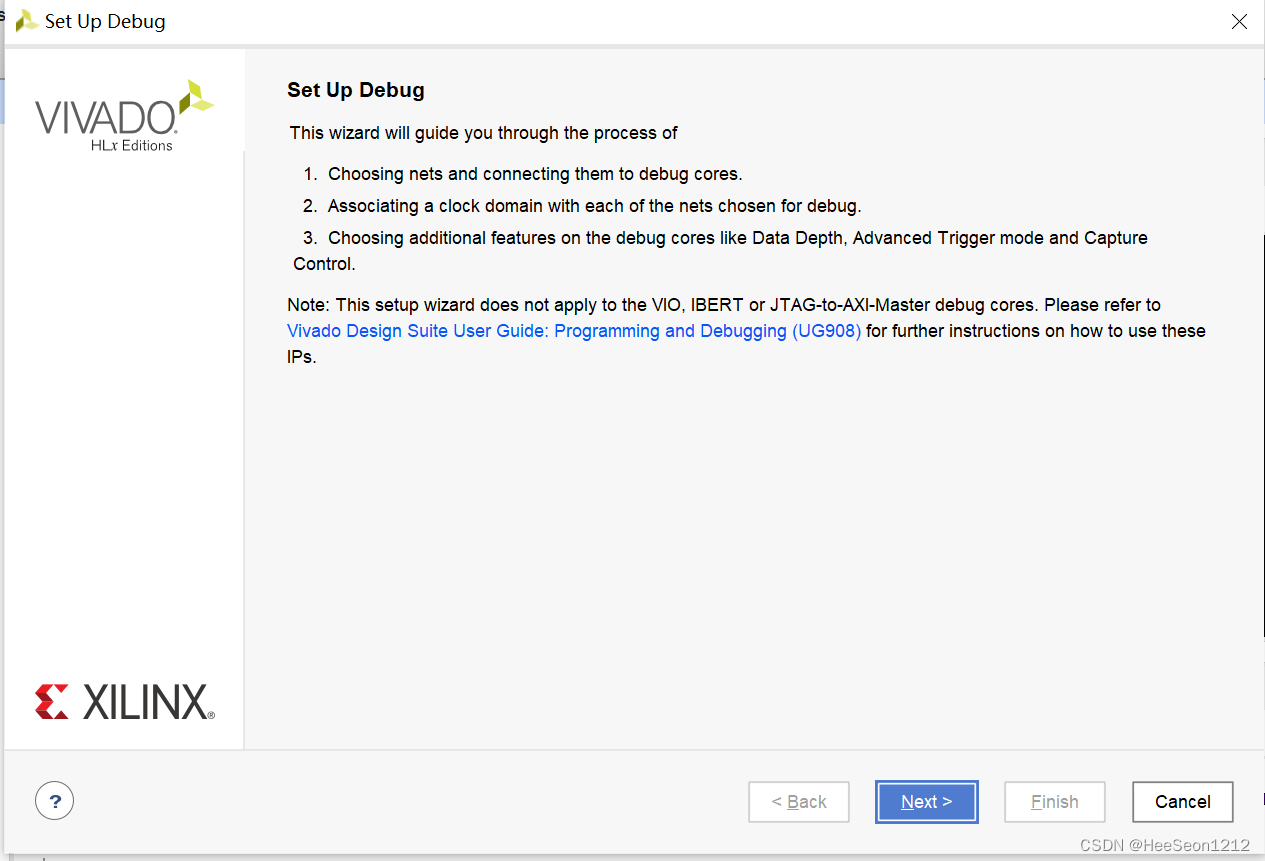

点击next,进入网表配置,NAME为你要观察的信号,Clock Domain为在哪个时钟域进行信号观测,选中要更改的某一行的clock domain右键,可以select clock domain,一般一个工程中的Clock Domain都设置成一样的,否则容易出错,往右拉进度条还有Driver cell,一般为默认,Probe type选Data and Trigger。

如果这个窗口中没有你要观察的信号,可以通过“+”从netlist添加。一般情况下,如果你已经用MARK DEBUG标注齐全,这个表中会包含全部你想要观察的信号,不需要额外添加了。

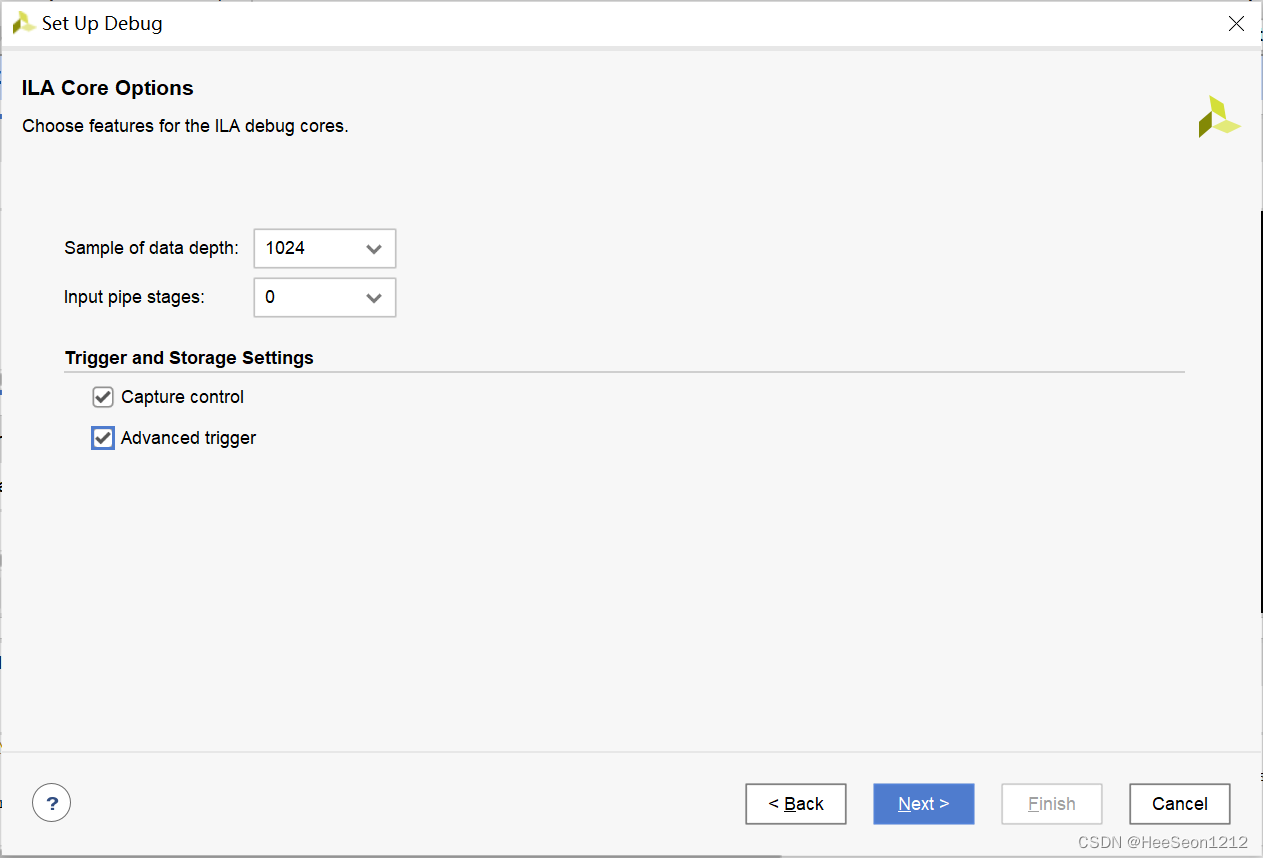

点击next,进入探针深度配置,即Sample of data depth,这个值选择越大,在后续的ila窗口中能看到的数据时间跨度就越大,越有利于分析,但选择过大,有可能会在后面implementation中出现资源不够的问题,所以自己试试吧,切记要勾选上Capture control和Advanced trigger。

点击next-finish,进入creating debug core,等待生成结束。生成结束后会弹出Schematic。

三、进行implementation及bit流生成

双击vivado左侧界面的run implementation,会提示你保存刚刚由set up debug 产生的文件更改,一定要点击save,不然对应的xdc文件是不对的

save以后一路点击ok,等待implementation完成,这一步骤时间视程序复杂程度而定。

完成后,点击vivado界面左侧generate bitstream,等待完成。

完成后先不要烧写FPGA程序,后续在SDK中烧写,防止多次烧写锁相环出错。

四、导出硬件平台,打开SDK

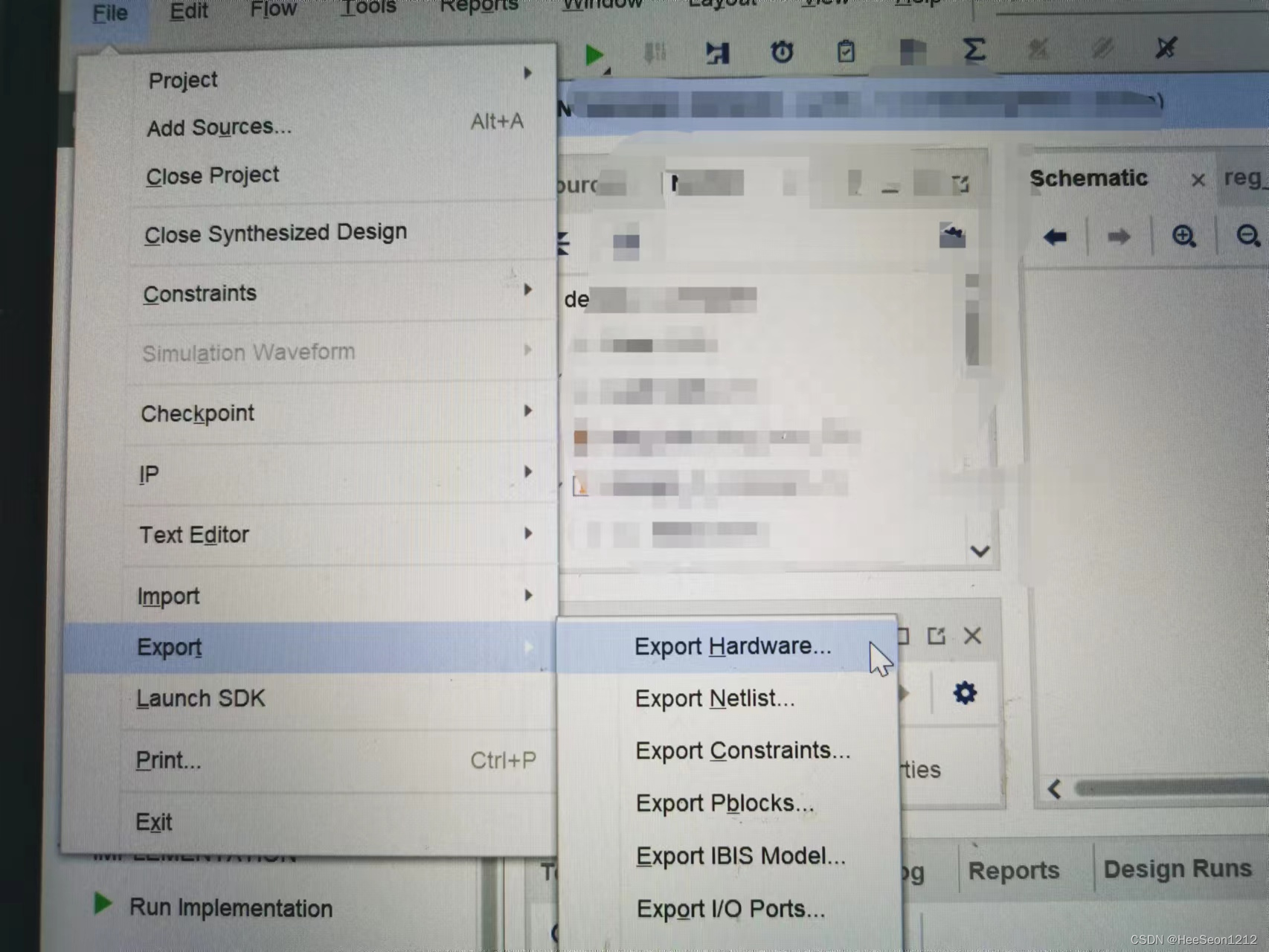

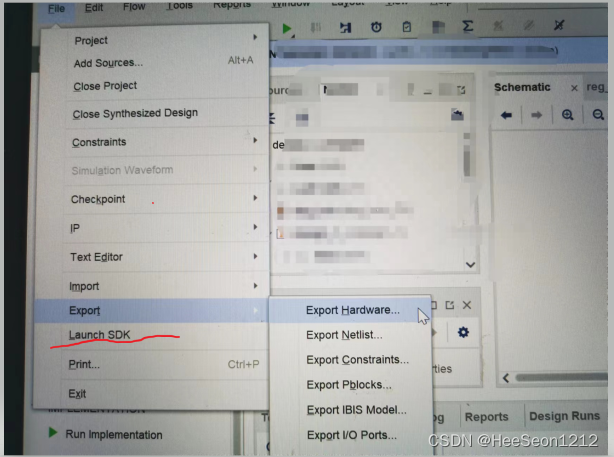

生成bit流后点击左上角file-export-export hardware,导出硬件平台,切记勾选include bitsream,ok

随后点击左上角file-launch SDK,打开SDK;

建立你的工程,然后在左侧文件目录中选中工程,右键,选择debug as-Debug configuration,

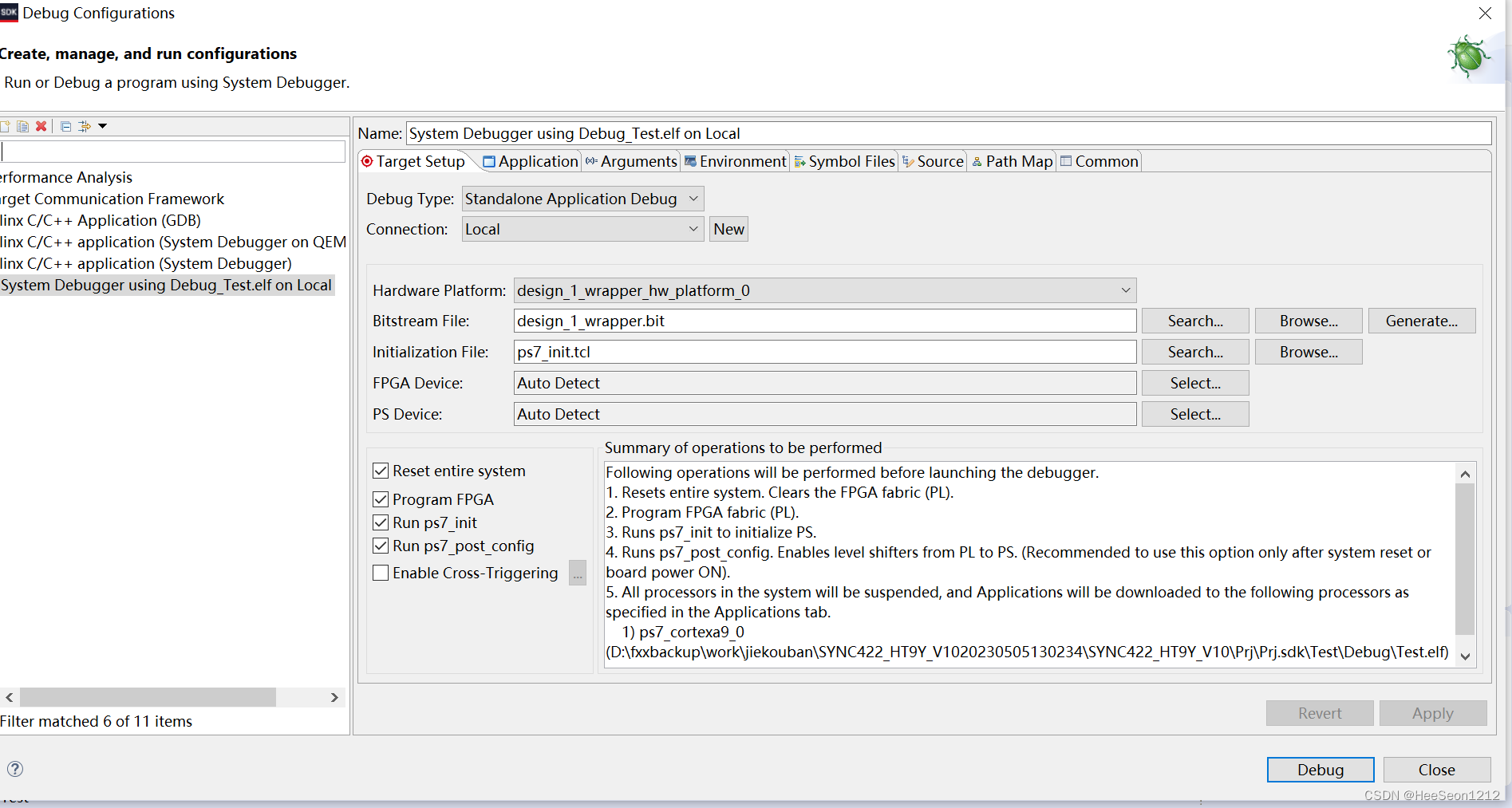

进入以下界面

platform,bitstream file选择对应的文件,注意勾选上Reset entire system和program FPGA,硬件平台连接好,上电,然后点击Debug,就进入正常的C语言debug模式了,这个时候你可以设置断点,单步调试等等。

五、从SDK触发FPGA端的ila

在第四步中,已经从SDK中烧写了FPGA程序,此时,芯片中已经在运行程序了。

返回vivado界面,点击 open hardware maneger-点击红圈中图标,自动connect硬件平台,连接上硬件以后不要再program devices了,等过几秒钟就会出现自动ila观察界面了,可以选择观察的信号,设置触发信号Trigger等,现在手里没板子,就不截图了。

至此,PS+PL联合调试步骤就结束了,剩下的与单独的PS调试、PL调试无异了。

下次可以记录以下PS和PL之间的AXI-LITE通信?