目录

数制与编码

字符和字符串的表示方法

ASCII码

ASCII码字符系统有128个元素,因此二进制编码需要7位,加上一个偶校验码,共八位,刚好一个字节。规定8位最高位为0,余下7位可以给出128个编码。

128个编码中,有95个可显示字符,编号范围是32-126。33个控制字符,编号范围是0-31和127。

汉字编码

输入编码:数字编码、拼音码、字型编码等

汉字内码:汉字信息的存储,交换和检索的机内代码,两个字节组成,每个字节高位都为1

输出编码:字模码

定点数和浮点数的表示

定点数即所有数据的小数点位置固定不变,分为定点小数和定点整数。

为了方便对数据进行运算时处理符号位与数值位的问题,计算机将符号位与数值位一起编码来表示数据,这些编码称为机器码。

定点数表示方法

机器码表示部分比较简单不再赘述,可参考https://blog.csdn.net/btufdycxyffd/article/details/127775989?spm=1001.2014.3001.5502

原码表示法

反码表示法

补码表示法

原码变成补码的方法:

- 原码符号位为1不变,整数的每一位二进制数位求反得到反码

- 反码符号位为1保持不变,反码数值位最低位加1,得到补码

移码表示法

移码通常用于表示浮点数的阶码。

移码和补码尾数相同,符号位相反

浮点数表示方法

浮点数即数据的小数点位置可在一定范围内浮动。

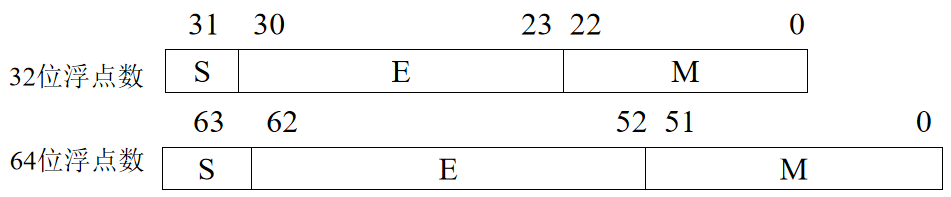

当前计算机采用IEEE754标准中的格式表示浮点数。规定32位短浮点数和64位长浮点数的标准格式为

S表示符号位,E是阶码,M是尾数,尾数用原码,指数用移码(便于对阶和比较)。

当尾数的值不为0时,尾数域的最高有效位为1。形式为:1.M,最高位1视为隐藏在小数点左侧,提高数据表示精度。

阶码采用移码方式(加上一个固定的偏移值),将指数真值e变为阶码E时,加上固定偏移值127,即E= e+127。

机器零:当一个浮点的尾数为0,不论阶码为何值;或当阶码的值比阶码的最小值还小,不论尾数为何值,视为机器零。

基数R=2,基数固定,采用隐含方式来表示它。

规格化:

原码:尾数的最高数位必须是一个有效值。

补码:尾数的最高数位必须与尾数符号位相反。

为什么要规格化?

答:若不对浮点数的表示作出明确规定,同一个浮点数的表示就不是唯一的。

规格化的32位浮点数x的真值为:

规格化的64位浮点数x的真值为:

浮点数的表示范围

例题:若浮点数x的二进制存储格式为(43AC0000)16,求其32位浮点数的十进制值。

解:将16进制数展开后,可得二进制数格式为:

指数e=阶码-127=10000111-01111111=00001000=(8)10

隐藏位1的尾数1.M=1.010 1100 0000 0000 0000=1.01011

所以真值:

定点数和浮点数的运算

定点数的运算

补码加法

[x+y]补=[x]补+[y]补 (mod 2n+1)

补码减法

口诀:求反且最末位加1

[x-y]补=[x]补- [y]补= [x]补+ [-y]补

[-y]补 = -[y]补 (mod 2n+1)

[-y]补 = [y]补取反 + 2-n

溢出概念与检测方法

溢出的概念 :在运算中出现大于字长绝对值的现象

溢出检测方法:双符号位法(变形补码)、单符号位法

双符号位法

[x]补 = 2n+2 + x ( mod 2n+2 )

Sf1 表示正确的符号,逻辑表达式为V=Sf1 ⊕ Sf2

例题:x=+01100 , y=+01000 , 求 x+y 。

定点乘法

阵列乘法器: 采用流水式阵列乘法器,取代串行方案

[x]原=xf.xn-1…x1x0 [y]原=yf.yn-1…y1y0[x.y]原=(xf ⊕ yf)+(xn-1…x1x0).(yn-1…y1y0)

两个原码表示的数相乘的运算规则是:乘积的符号位由两个数的符号位按异或运算得到,数值位按两个整数相乘之积得到。

不带符号位的阵列乘法器

带符号位的阵列乘法器

求补电路:

E=0时,输入和输出相等,E=1时,则从数最右端往左边扫描,直到第一个1的时候,该位和右边各位保持不变,左边各数值位按位取反

直接的原码乘法:输入原码并做乘法时,不需要算前求补、算后求补。立即可得乘积。

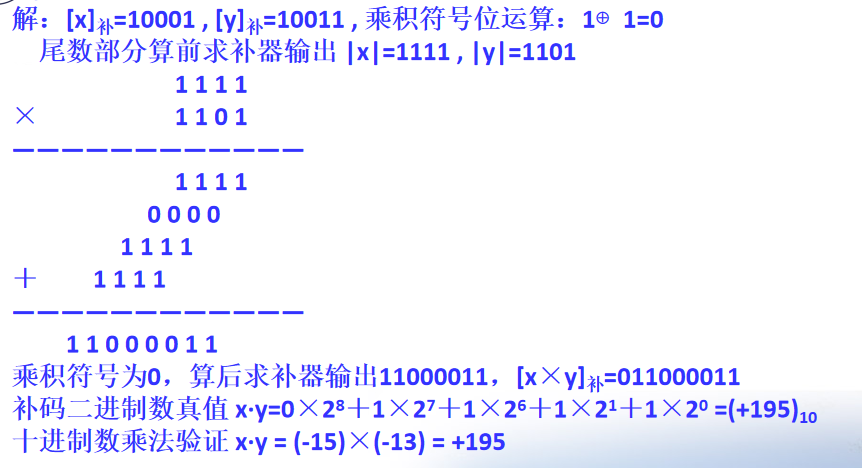

例题:设x=+15,y=-13,用带求补器的原码阵列乘法器求出乘积 x·y=?

间接的补码乘法:输入补码并作乘法时,需要算前求补,得各数的绝对值。经算后求补器,得乘积的补码。

例题:设x=-15,y=-13,用带求补器的补码阵列乘法器求出乘积 x·y=? 并用十进制数乘法进行验证。

定点除法

设有n位定点小数(定点整数也适用)被除数x,[x]原=xf.xn-1…x1x0除数y,[y]原=yf.yn-1…y1y0

则有商q=x/y,[q]原=(xf⊕yf)+(0.xn-1…x1x0/0.yn-1…y1y0)

商的符号运算qf=xf⊕yf与原码乘法一样,用模2求和得到。

原码恢复余数法

人工除法时,人可以比较被除数(余数)和除数的大小来确定商1(够减)或商0(不够减) 机器除法时,余数为正表示够减,余数为负表示不够减。不够减时必须恢复原来余数,才能继续向下运算。

这种方法叫恢复余数法,控制比较复杂。

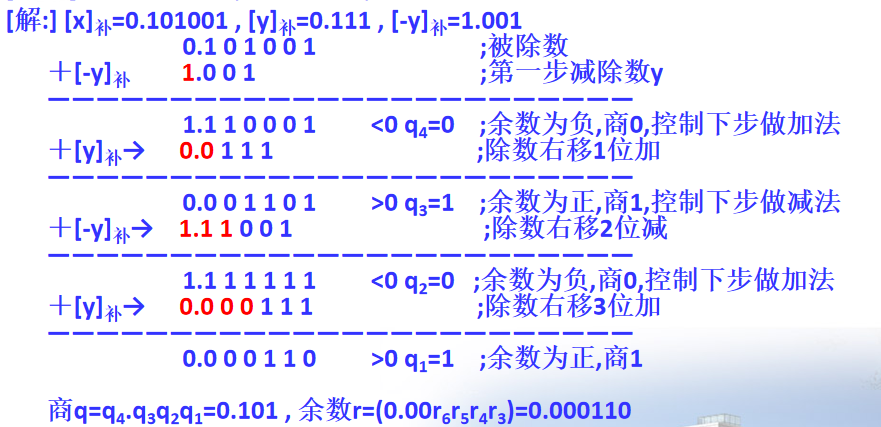

原码不恢复余数法(加减交替法)

余数为正,商1,下次除数右移做减法;

余数为负,商0,下次除数右移做加法。

运算步数固定,控制简单,有规律。

例题:x=0.101001, y=0.111, 求x÷y。

不恢复余数的阵列除法器

浮点数的运算

浮点数的加、减法运算

设有两个浮点数x和y,它们分别为

x=2E^x·Mx y=2E^y·My

其中Ex和Ey分别为数x和y的阶码,Mx和My为数x和y的尾数。

两浮点数进行加法和减法的运算规则是:x±y=(Mx2(Ex-Ey)±My)2Ey

运算步骤

- 0操作数检查;遇0时,可做旁路处理

- 比较阶码并完成对阶(小阶向大阶对齐);

规则是阶码小的向阶码大的数对齐;小阶对大阶;

△E =[Ex]补-[Ey]补

- 若阶差△E=0,表示两数阶码相等,即Ex=Ey;

- 若阶差△E>0,表示Ex>Ey;

- 若阶差△E<0,表示Ex<Ey。

- 当Ex≠Ey时,要通过尾数的移动以改变Ex或Ey,使之相等。

- 尾数加、减运算;

- 结果规格化;

这部分我也不太懂,详细参考https://blog.csdn.net/weixin_43715360/article/details/120256108

若尾数求和结果符号位用双符号位表示,结果得到10.&&&&&或01.&&&&&,即双符号位不相等,在定点加减法运算中称为溢出。浮点运算中表明运算结果绝对值大于1,破坏了规格化,此时要右移规格化处理。而数值位最高位无效时(注意原码和补码不同),通过左移尾数,使数值最高位有效。

- 右规处理:当尾数运算有溢出时,右移1位,阶码加1。

- 左规处理:当尾数运算无溢出时,且尾数不是1.M(这部分不太懂,还有例题也是,不知道对不对,先写下来)时,则尾数左移1位,阶码减1。

- 舍入处理;

- 就近舍入(0舍1入):类似”四舍五入”,丢弃的最高位为1

- 进1朝0舍入:截尾

- 朝+∞舍入:正数多余位不全为”0”,进1;负数,截尾

- 朝-∞ 舍入:负数多余位不全为”0”,进1;正数,截尾

- 溢出处理。

阶码上溢,一般将其认为是+∞和-∞ 。阶码下溢,则数值为0。

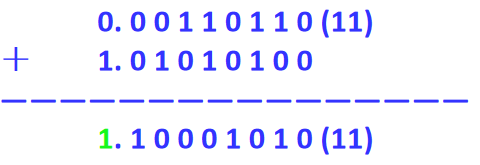

例题:设x=2^010 ×0.11011011,y=-2^100×0.10101100,求x+y 。

解:设阶码及尾数都用补码表示

[x]浮补=00010, 0.11011011; [y]浮补=00100, 1.01010100

① 0操作数检查(非0):提高运算速度

② 对阶:阶码对齐后才能加减

此题阶差△E =[Ex]补-[Ey]补=00010-00100=11110=-2D

即阶差为-2,Mx右移两位,Ex加2。

[x]浮补=00100, 0.00110110(11)

③ 尾数相加或相减

④ 结果规格化

尾数不是1.M,左规格化处理,变为1.00010101(10),阶码00100减1变为00011

⑤ 舍入处理

采用就近舍入(0舍1入)法处理,得到 1.00010110。

⑥ 溢出判断和处理

阶码符号位为00,无溢出。得最终结果为 x+y = 2^011×(-0.11101010)

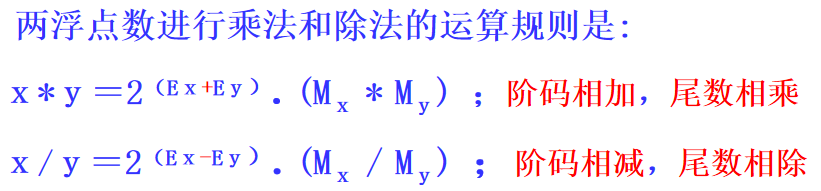

浮点数的乘、除法运算

运算步骤与上面一样

运算器的组成

运算器是由算术逻辑单元(ALU)(核心)、累加器、状态寄存器、通用寄存器组等组成的。

运算器的主要功能是完成对数据的算术和逻辑运算,由其内部的一个被称之为算术与逻辑运算部件(ALU)承担,它在给出运算结果的同时,还给出结果的某些特征,如溢出否,有无进位输出,结果是否为零、为负等,这些结果特征信息通常被保存在几个特定的触发器中。

在执行指令的过程中,必须向ALU提供其执行何种运算的控制信号。

寄存器的功能:暂存将参加运算的数据和中间结果,这些寄存器可以被汇编程序员直接访问,通称通用寄存器,以区别于那些计算机内部设置的、不能为汇编程序人员访问的专用寄存器。

算数逻辑单元(ALU)

ALU有2个单元,一个是算术单元和一个逻辑单元。

算术单元:负责计算机里的数字操作,比如加减法。

逻辑单元:负责计算机中的逻辑运算,比如与、或、非、异或等。

除此之外ALU还有辅助功能:移位,求补等。

算数单元

一位全加器:最基本的加法单元,输入两位加数及低位的进位,输出和与高位进位

串行加法器:一位全加器的简单相连,串行进位

并行加法器:使用先行进位提高加法器的运算速度

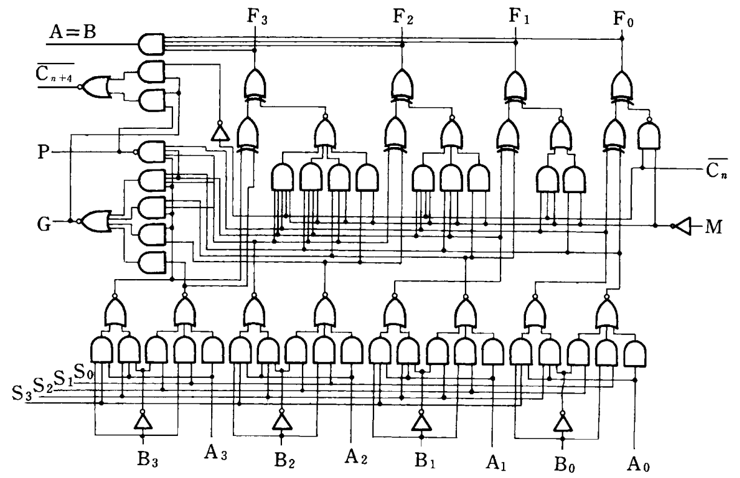

74181ALU逻辑电路图

算术逻辑运算的实现(74181ALU)

① M=L=0时,对进位信号没有影响,做算术运算

② M=H=1时,进位门被封锁,做逻辑运算

逻辑单元

逻辑单元执行逻辑操作,比如AND,OR和NOT操作,它也能做简单的数值测试,比如一个数字是不是负数。

内部总线

机器内部各部份数据传送频繁,为了减少内部数据传送线并便于控制,可以把寄存器间的数据传送通路加以归并,组成总线结构。

总线分类:

所处位置

- 内部总线(CPU内)

- 外部总线(系统总线)

逻辑结构

- 单向传送总线

- 双向传送总线

运算器的基本结构

单总线结构的运算器

双总线结构的运算器

三总线结构的运算器