大家好,我是小黄鸭,需要源码的文章末尾有我的联系方式。

实验所用的软件资源/测试电路也全部开放,地址在MOOC中国大学为:https://www.icourse163.org/learn/HUST-1205809816#/learn/announce

附带实验测试,地址在Educode上为:https://www.educoder.net/shixuns/f8tlev94/challenges

实验重点为运算器原理的考察,而并非线路和器件连接方式,但是在连接线路是要注意引脚的说明,避免浪费不必要的时间。

8位可控加减法电路

- 该实验通过全加器串行输入实现8位可控加减法。

- 主要考察加减法的转换,即通过补码实现减法,和溢出信号的检测。

4位先行进位74182

- 实现可级联的4位先行进位电路。其中 Gi,Pi 为进位生成函数和传递函数,Cin 为进位输入,C1~C4 为进位输出,G,P 为成组进位生成函数和成组进位传递函数。

- 考察对生产函数和传递函数,不断分级。

4位快速加法器设计

- 利用前一步设计好的四位先行进位电路构造四位快速加法器。

- 这里就是结合设计好的74128进行一下改装。

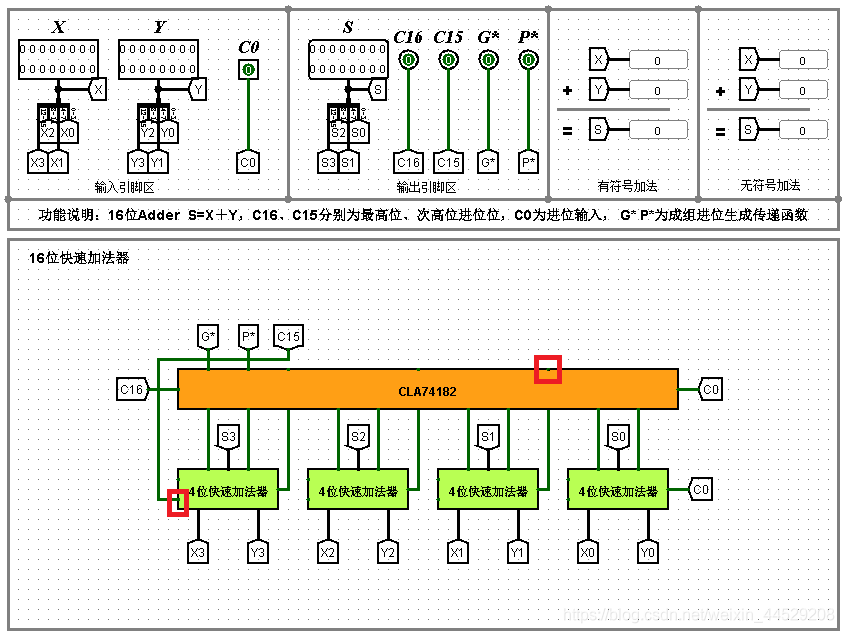

16位快速加法器

- 利用四位先行进位电路和四位快速加法器构造十六位组间先行进位,组内先行进位快速加法器

- 这里相当于由4位扩展为16位,进一步的升级。重点理解扩展的含义。

- 注意:C15接口为次高位进位。并且每4位的进位C1、C2、C3、C4是由74128的上端接口连到4位快速加法器的进位输入端。

32位快速加法器

可能方案:

-

2个16位加法器直接串联,C16 信号采用下层的进位输出

-

2个16位加法器直接串联,C16 进位输入采用上层的进位输出

-

在16位快速加法器的基础上再增加一级组间先行进位电路,类似6464位快速加法器的方法。

方法很多,有兴趣可以尝试进行对比分析。

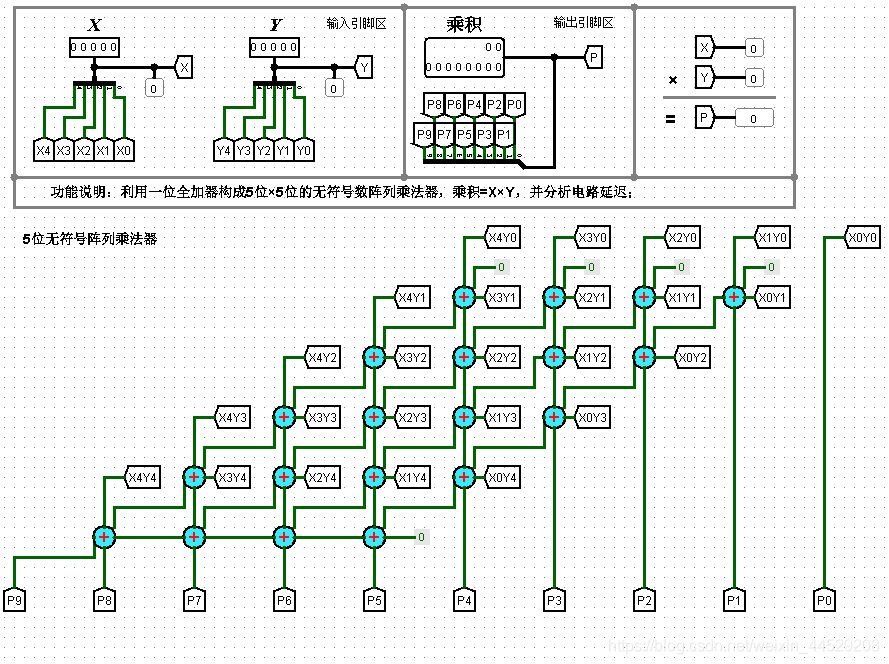

5位阵列乘法器

- 在5位阵列乘法器中实现斜向进位的阵列乘法器。

- 上下上下,左右左右,哈哈哈哈

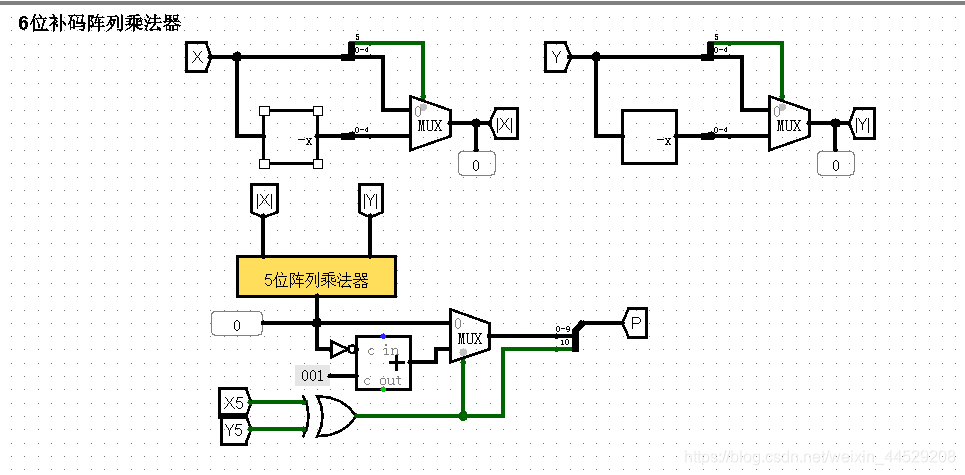

6位有符号补码阵列乘法器

- 在6位补码阵列乘法器中利用5位阵列乘法器以及求补器等部件实现补码阵列乘法器

- 用到了分离器和其他几个运算器。有补码器,加法器,数据选择器。如下图。

数据选择器:

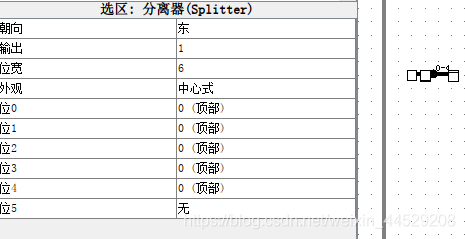

分离器:

补码器:

5位无符号乘法流水线

- 在6位补码阵列乘法器中利用5位阵列乘法器以及求补器等部件实现补码阵列乘法器。

- 用到了扩展器。

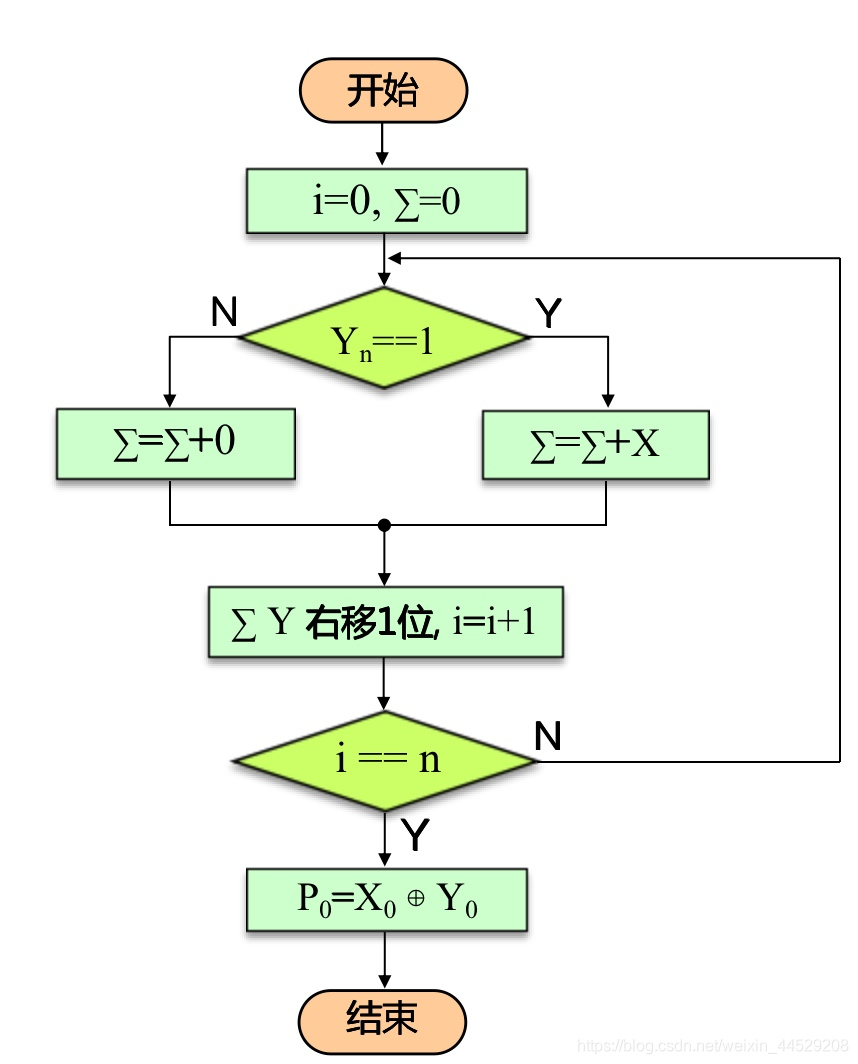

原码一位乘法器

重点还是原理,这里用到了分线器和之前用到的中心式分离器

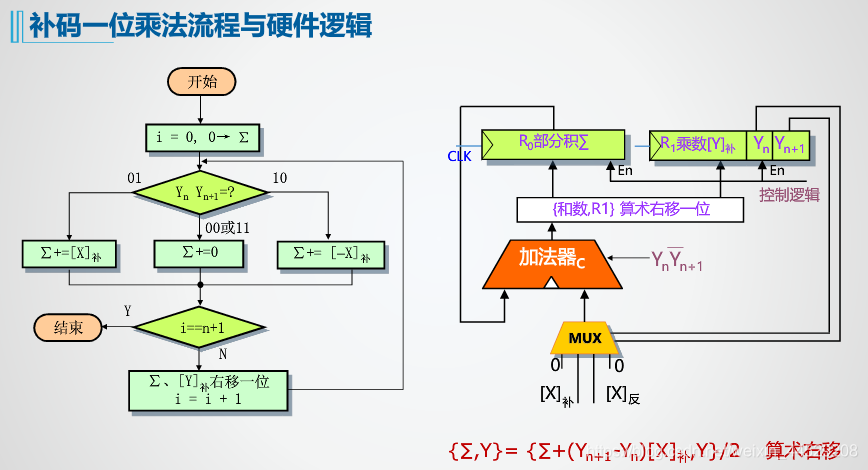

补码一位乘法器

这个实验挺多坑的,例如yn+1位的输入,y的右移和x的右移,如果实在不懂可评论或者私聊。

32位算术逻辑运算单元ALU

ALU是根据OP字段来决定对应的功能,对应关系如下:

先构建好各OP值所对应的算术逻辑操作,最后用数据选择器(MUX)来连接就可。注意不同输出接口的要求。

持续更新,如有问题或者建议可在下方留言或者私聊。需要源码+q453682174