FPGA小脚丫开发板学习笔记:VHDL组合逻辑-时序逻辑练习

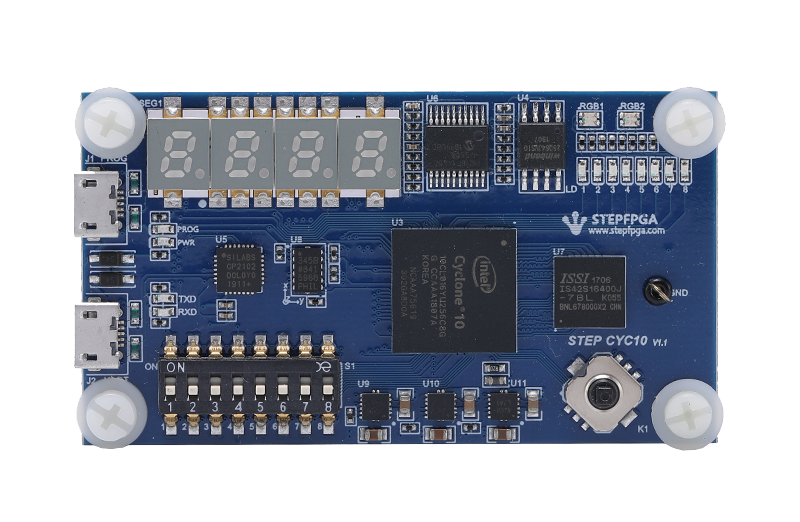

板子:Altera Cyclone10 STEP小脚丫FPGA开发板

IDE:QuartusII 18.1(Educational)

仿真软件:Modelsim-Alterl

芯片系列:Cydone 10 LP

芯片核心:10CL016

芯片名称:10CL016YU256C8G

文章目录

〇、什么是FPGA?

突然发现自己连FPGA的全称是什么都不知道,所以在这里临时加一条

1. FPGA的概念

FPGA(Field Programmable Gate Array)是在PAL (可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

全称Field Programmable Gate Array,译为**“现场 可编程 门 阵列”** 。

我们可以把FPGA当做是数字世界的乐高(Lego),它由几种最基本的单元(每种单元数量有很多很多)让你组成自己想实现的功能。能玩好乐高就一定能玩好FPGA。乐高玩得好不好,取决于什么因素?

通过一些最基本的积木块可以拼出任何复杂的物体

2. 为什么FPGA≈乐高

-

第一:一套乐高中都有很多单元,每种单元各有自己的特性,不同单元之间的拼接方法也是多样的

-

第二:从几千个乐高piece里面组装一辆车一栋楼亦或是一座城是很困难的,但如果有图纸就会变得很简单,亦或是把我们的思维当作一张图纸来把这几千个piece构建成一座梦幻都市。

-

第三:无限次地拆分与重组,乐高可以将成品拆分再构建成另一个成品,FPGA同样能加载一个新的设计方案并且只需几百毫秒,利用重配置可以减少硬件的开销。

-

第四:逻辑单元越多,FPGA便能越强大。当我们的乐高piece够多时,组装一个1:1比例的法拉利跑车也变为可能,而当FPGA的逻辑单元足够多时,他甚至能成为一个5G基站的核心。

逻辑门单元是构成一切数字逻辑器件的基本单元,在数字世界里你想做任何事情、实现任何功能,都可以通过逻辑门的堆砌来实现,也就是说FPGA在数字领域里几乎无所不能,因此n年前我国的某一个FPGA公司在向国务院领导描述其产品的时候称他们做的是“万能芯片”(用这种通俗易懂的说法忽悠国家的经费)。万能有些夸张,但FPGA高度灵活,理论上来讲,只要有足够的资源(积木数量足够多)几乎可以实现数字域的任何功能,受限的是速度、功耗以及系统的成本。

一、在QuartusII 中用原理图输入法设计 4 位加法器

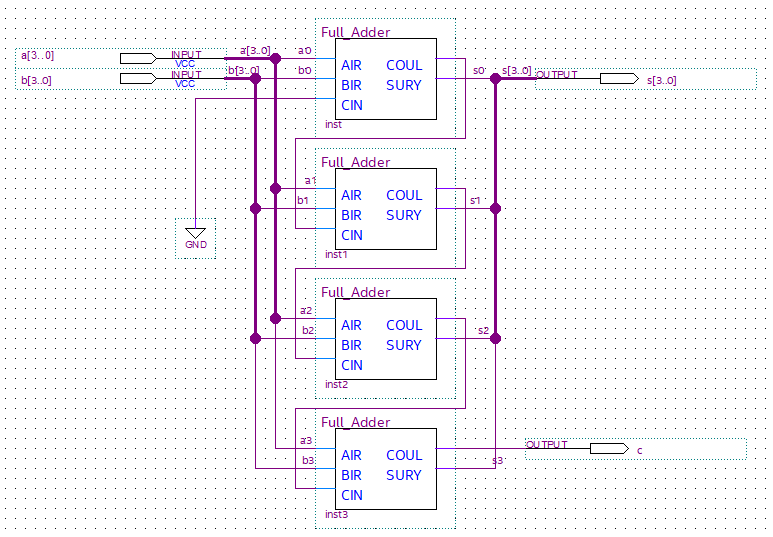

**原理:**一个4位全加器可以由4个1位全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相临的高位加法器的最低进位输入信号cin相接(串行进位加法器)。

1. New一个原理图

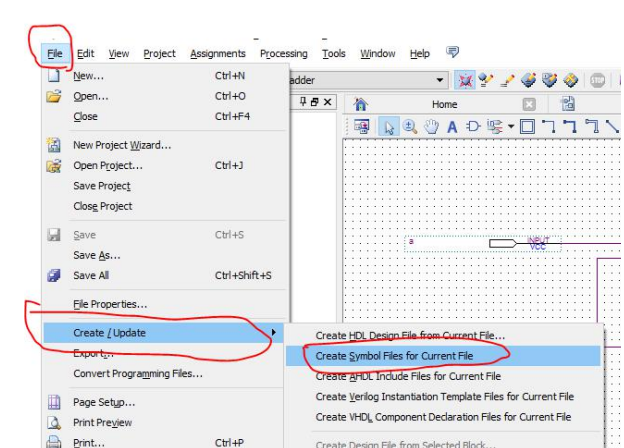

- 在上一个工程文件《FPGA实验记录一:1位全加器设计》的基础上直接新建一个原理图,并把原来的一位全加器直接导出为可调用元件

-

建立一个更高层次的原理图设计,利用实验一获得的1位全加器构成4位全加器:

注意总线连接方式必须对连线命名,方法是单击要命名的连线,出现光标后直接输入连线的名字,如总线a[3…0],或单线a0(✌✌✌!!把标准两个字打在公屏上!!✌✌✌)

-

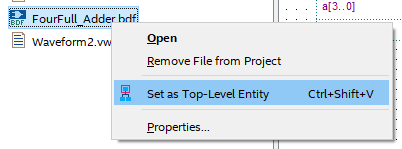

将新的原理图设置为顶层文件后并编译

2. New一个波形仿真文件

-

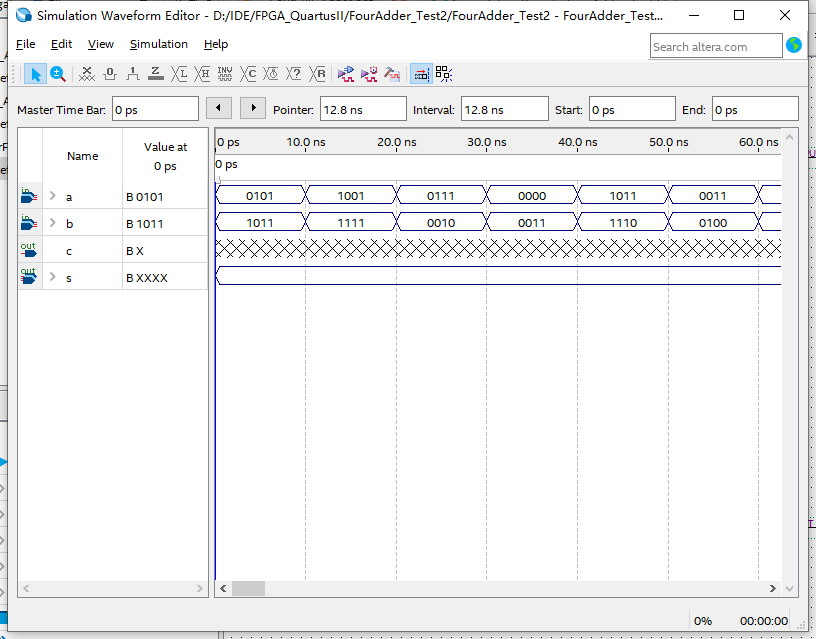

新建波形文件Waveform2作为四位全加器的波形仿真文件,用老方法将所有input和output添加到仿真文件中,并使用Random随机波形

-

点击

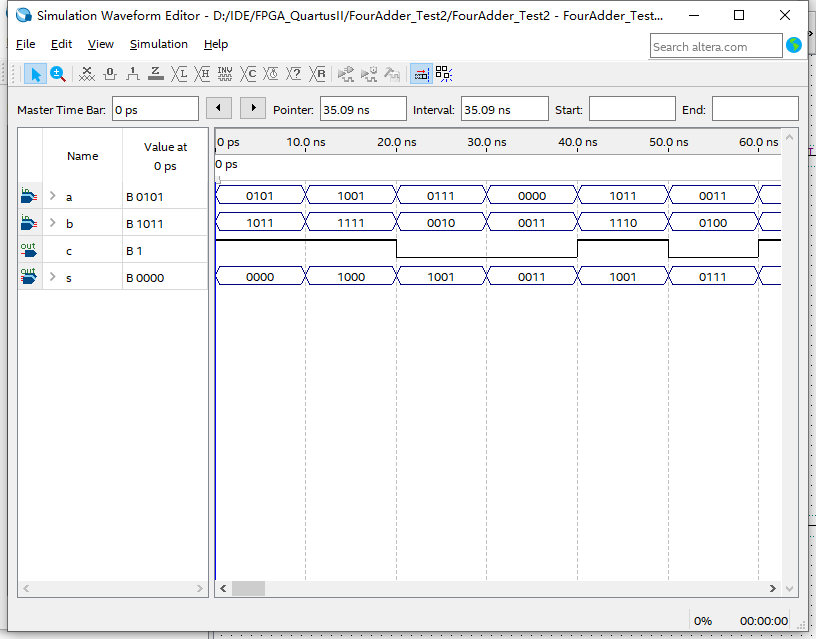

进行仿真,等待片刻得到结果

进行仿真,等待片刻得到结果

3. 下载与硬件测试

-

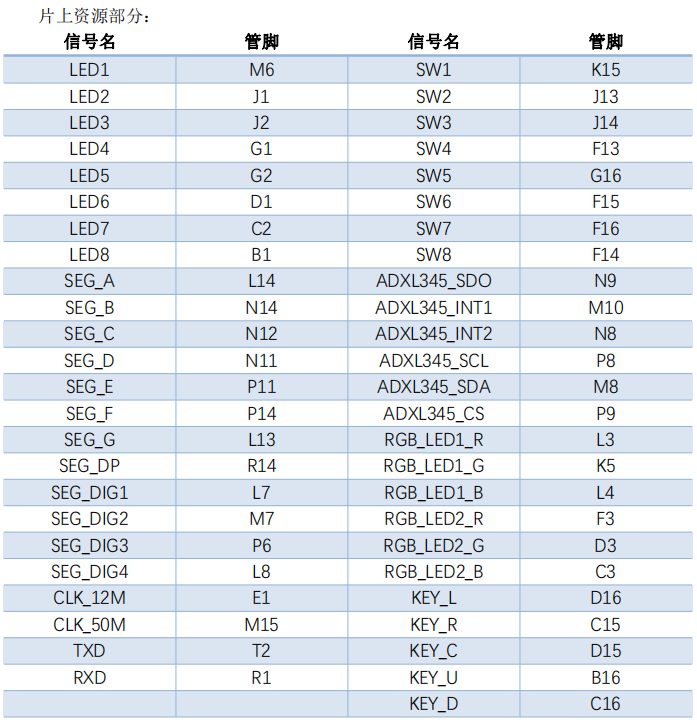

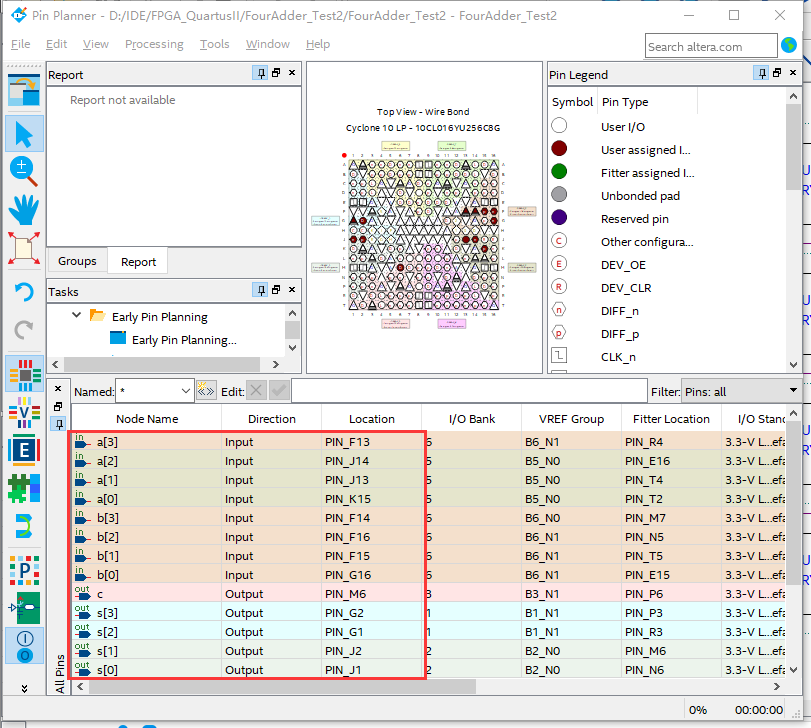

绑定引脚:将a[0…3]和b[0…3]两根总线拆分为八根input输入线分别绑定Switch1-8(小脚丫开发板刚好八个开关);c与s[0…3]分别绑定在LED1-5上。(引脚参考手册见末尾)

-

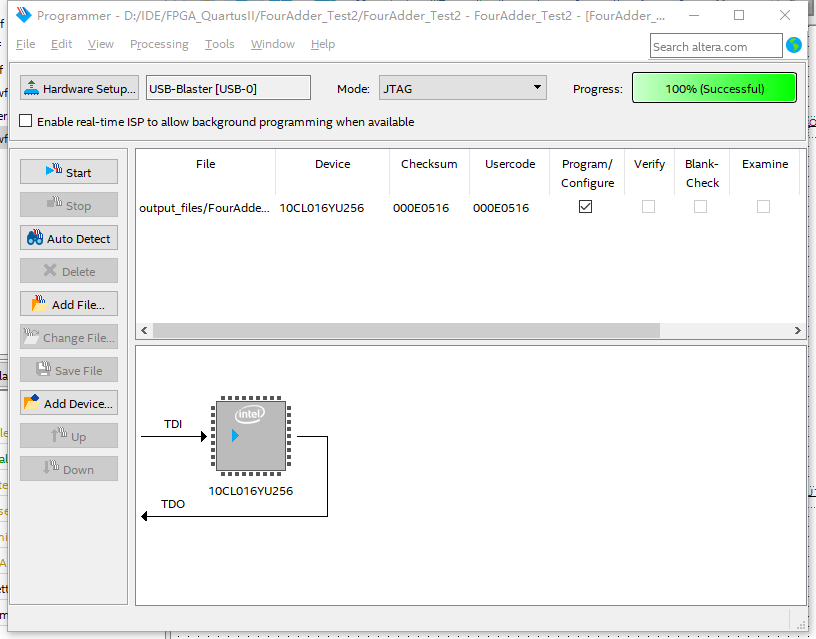

下载程序至开发板

-

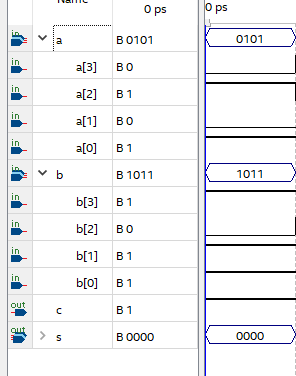

根据波形文件的仿真结果进行测验:

二、应用QuartusII 完成基本组合电路设计

0. VHDL

VHDL 的英文全名是VHSIC Hardware Description Language(超高速集成电路硬件描述语言)。VHSIC是Very High Speed Integrated Circuit的缩写,是20世纪80年代在美国国防部的资助下始创的,并最终导致了VHDL语言的出现。1987 年底,VHDL被 IEEE 和美国国防部确认为标准硬件描述语言。VHDL 用于描述数字系统的结构,行为,功能和接口。除了含有许多具有硬件特征的语句外,VHDL的语言形式和描述风格与句法是十分类似于一般的计算机高级语言。VHDL的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件,一个电路模块或一个系统)分成外部(或称可视部分,及端口)和内部(或称不可视部分),既涉及实体的内部功能和算法完成部分。在对一个设计实体定义了外部界面后,一旦其内部开发完成后,其他的设计就可以直接调用这个实体。这种将设计实体分成内外部分的概念是VHDL系统设计的基本点。

1. 二选一多路选择器

完成2选1多路选择器的文本编辑输入(mux21a.vhd)和仿真测试等步骤。最后在实验系统上进行硬件测试,验证本项设计的功能。

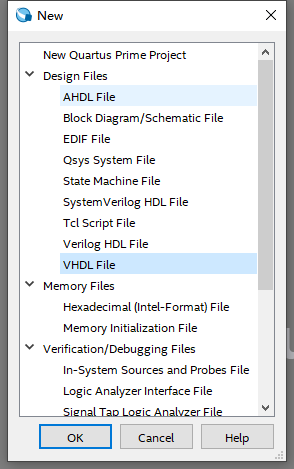

1.1 新建工程并新建一个VHDL文件

1.2 编写代码

代码解释全在注释里,基本每一句都读了。

LIBRARY IEEE;

--LIBRARY:库 当作import即可

--IEEE库:由IEEE(美国电子电机工程师学会)制定的标准库 LPM库

--库:库分为ieee库,std库,work库。

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

--USE:使用IEEE库中的STD_LOGIC_UNSIGNED的所有内容

--ieee库列举常用的包:std_logic_1164:逻辑系统;std_logic_arith:数据类型的转换;std_logic_signed;std_logic_unsigned。

--“.”:包含关系,类似于Java的包

--“;”:表示语句结束

ENTITY mux21a IS

--实体名:mux21a 是

PORT ( IN0,IN1,S1:in BIT; --port_name : signal_mode signal_type;

--引脚IN0,IN1,S1;为输入单向引脚;输入为二进制高低电频

--STD_LOGIC是IEEE在1993年制定的新的标准(IEEE STD1164),它具有9种不同的值

COUTY : OUT BIT);

--引脚COUTY;为输出单向引脚;输入为二进制高低电频

END mux21a;

--ENTITY到END位实体结构,用来描述电路的输入输出引脚

--singal_mode有四种:in,out;inout;buffer

--IN,OUT是单向引脚,INOUT是双向引脚,BUFFER输出一个引脚,但是输出信号可供电路内部使用 注意啦:OUT不能供电路内部使用

--signal_type包括BIT;STD_LOGIC;INTEGER(BIT为二进制,两种值;STD_LOGIC有九种;)

ARCHITECTURE behav OF mux21a IS

--mux21a实体的行为逻辑是:

--ARCHITECTURE部分为构造体(用来描述电路行为和实现功能),对信号和常量等进行声明

BEGIN

--代码(BEGIN-END):描述电路行为和实现功能

COUTY<=IN0 when S1='0' ELSE IN1;

--当S1处于低电平时,COUNT输出IN0;反之,输出IN1

END behav;

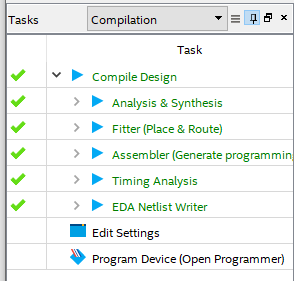

1.3 编译即仿真

- 编译

-

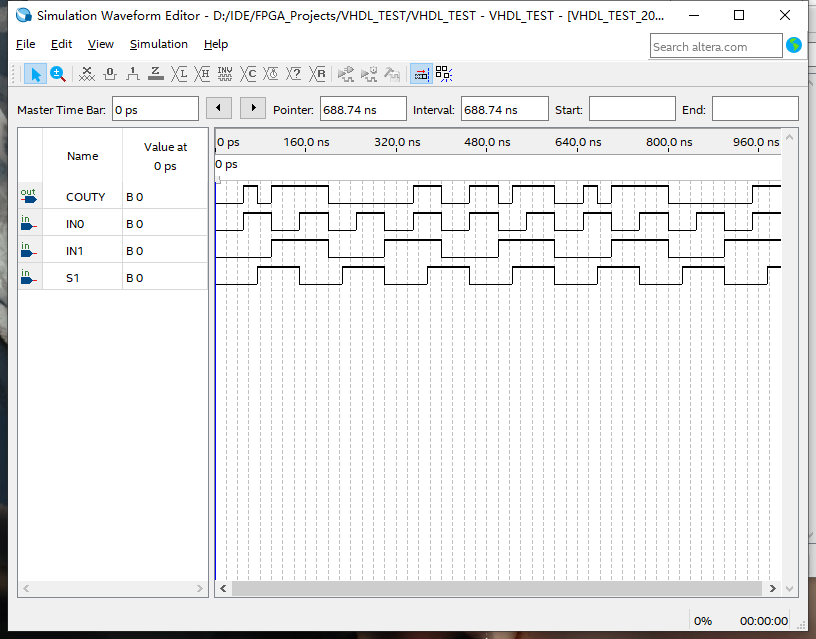

仿真

由仿真结果可知,我们可知当S1处于高电平时,COUNT输出IN1;反之,输出IN0.所以所设计的实验能够满足要求。

2. 双二选一多路选择器

本实验中直接利用上题的mux21a。由上题可知,mux21a由2个数据输入口(IN0,IN1),1个数据选择端(S1),一个输出口(COUTY)构成。设有两个mux21a,分别为U1和U2。为了充分利用U1和U2的数据选择端,我们将U1的输出口(COUNT)接到U2的输入口IN0,这样U2通过自身的选择端(S1)就可以选择U1的输出或则自己IN0的输入数据,实现2选1选择器到双2选1多路选择器的扩展。

2.1 编码

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY dmux21a IS

--实体双二选一多路选择器是

PORT ( IN0,IN1,IN2,S0,S1:in BIT;

--输入引脚为IN0,IN1,IN2,S0,S1,输入模式为BIT

COUTY : OUT BIT);

--输出引脚为COUTY,输出模式为BIT

END dmux21a;

ARCHITECTURE BHV OF dmux21a IS

--实体双二选一多路选择器的逻辑行为模式是

COMPONENT MUX21A

--元件名称是MUX21A 它的构造如下所示:

PORT(IN0,IN1,S1:IN BIT;

COUTY :OUT BIT);

END COMPONENT;

--元件声明和实体声明一致,元件就是一个实体

SIGNAL tmp : BIT;

--声明一个信号为tmp,模式为bit

BEGIN

u1 : MUX21A PORT MAP(IN0, IN1, S0, tmp);

--元件u1为MUX21A,引脚为IN0,IN1,S0,TMP

u2 : MUX21A PORT MAP(IN2, tmp, S1, COUTY);

END BHV;

2.2 编译并仿真

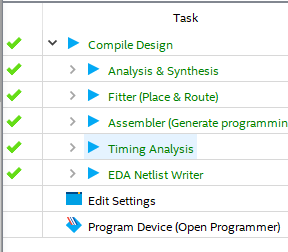

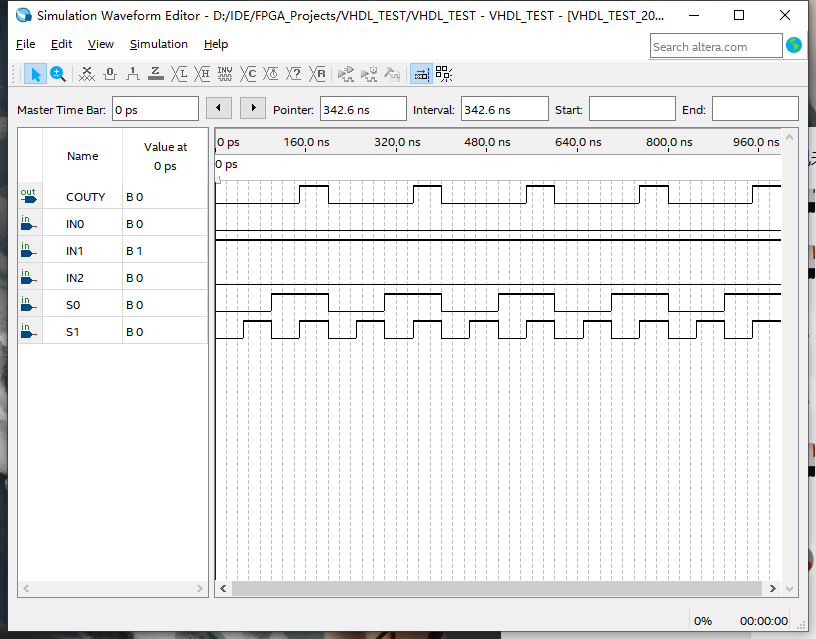

-

将dmux21a设置为顶层文件然后进行编译

-

新建波形文件进行仿真

波形图预测:当S1=0时输出IN2的波形;当S1=1,S0=1,输出IN1的波形;当S1=1,S0=0,输出IN0的波形。

由波形图可知,仿真结果与预测结果一致。

波形仿真时曾出现error loading design错误,网上说法有很多,但我这里是因为笔记本没电了不足以支持完成仿真导致的

-

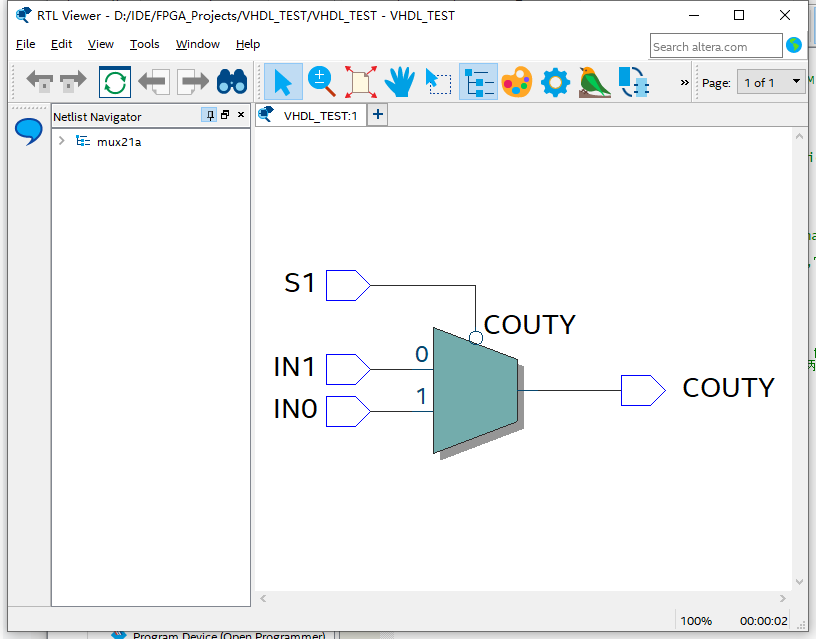

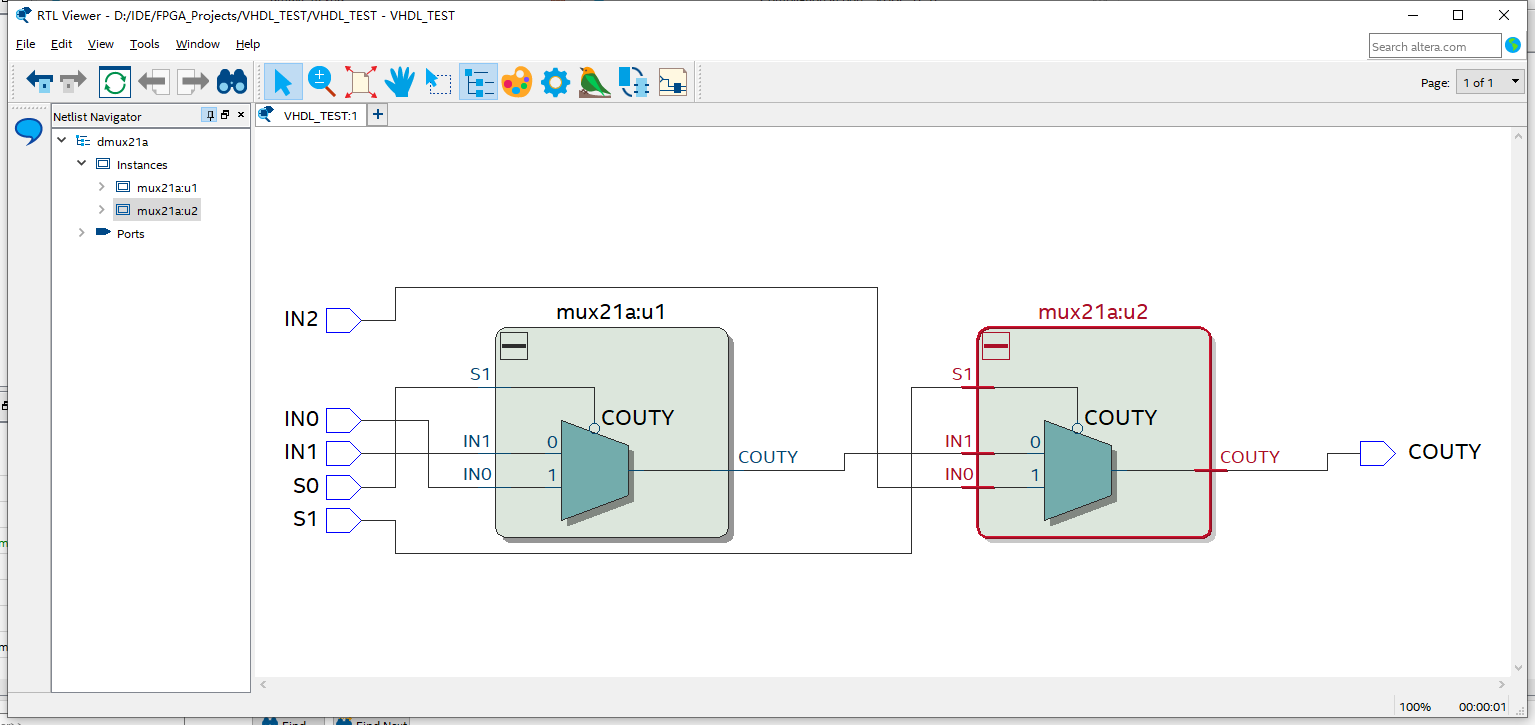

查看RTL电路

Tools->Netlist Viewers->RTL Viewer

-

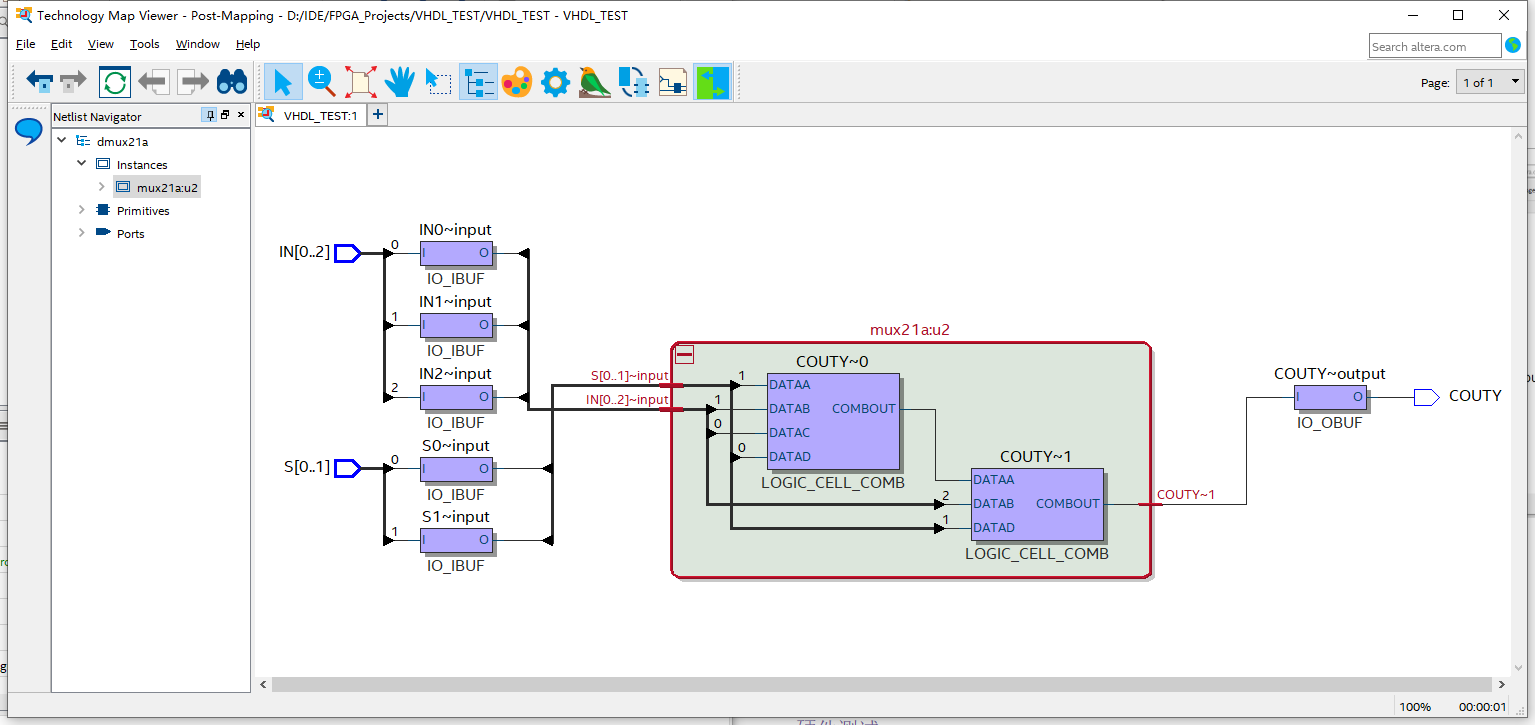

查看门电路

Tools->Netlist Viewers->Technology Map Viewer

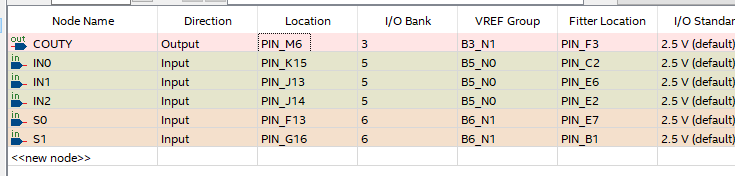

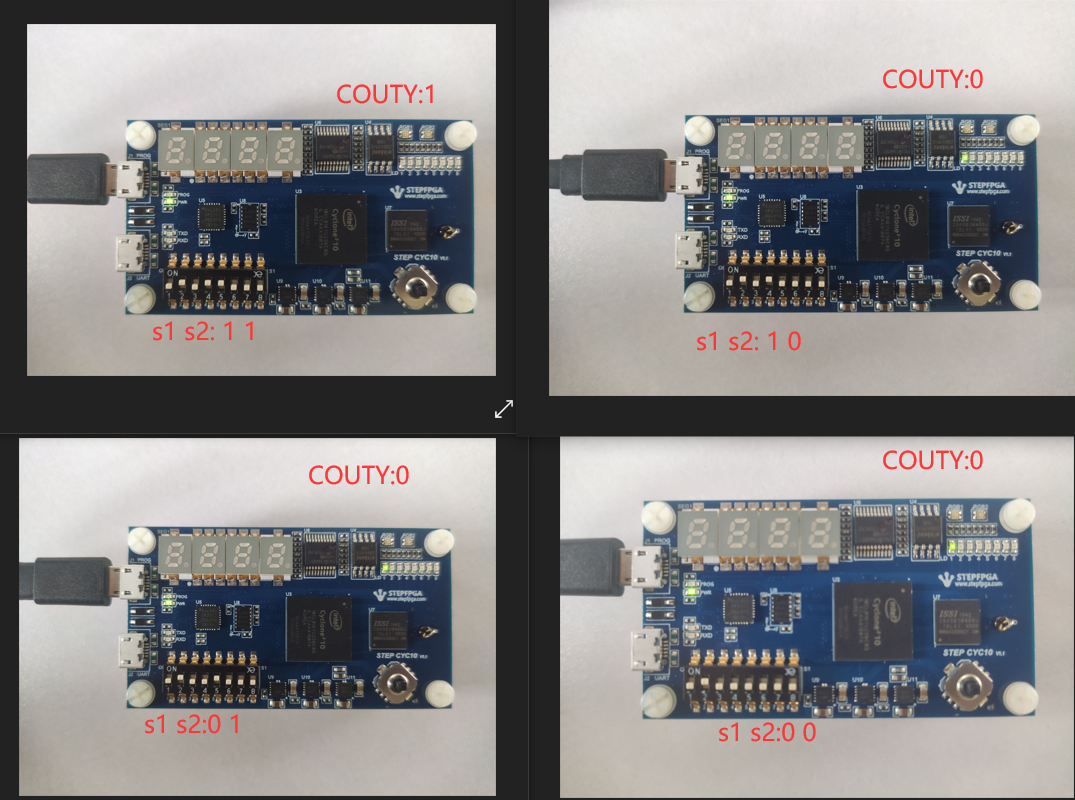

2.3 硬件测试

-

绑定引脚

将COUTY绑定在LED1,五个输入引脚分别绑定给SW1-5

-

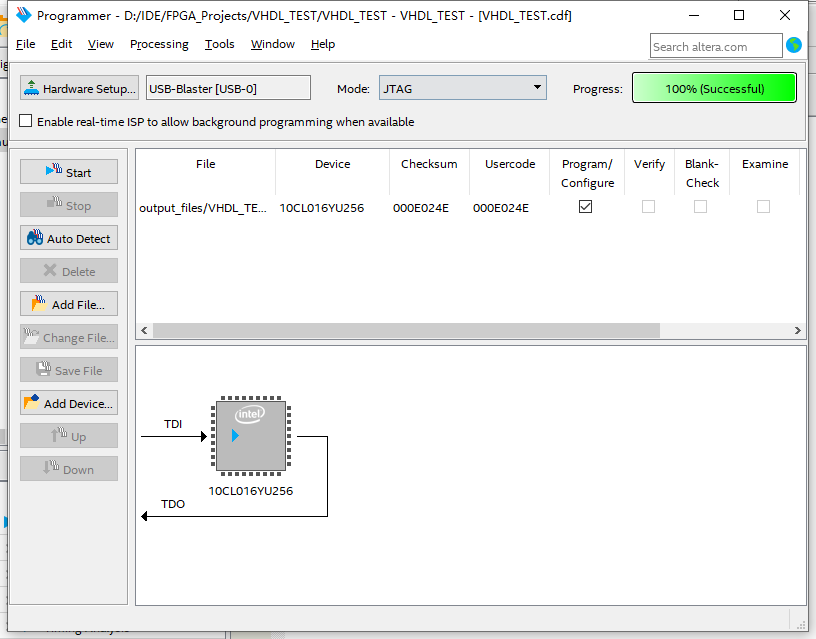

下载

-

测试

测试预测:IN0,IN1,IN2分别恒为0,1,0

当S2=0时输出IN2的波形;

当S2=1,S1=1,输出IN1的波形;

当S2=1,S1=0,输出IN0的波形

因为做图的时候把S0,S1做成S1,S2了,所以文字也将错就错了。

由硬件测试图可知,仿真结果与预测结果一致,实验成功

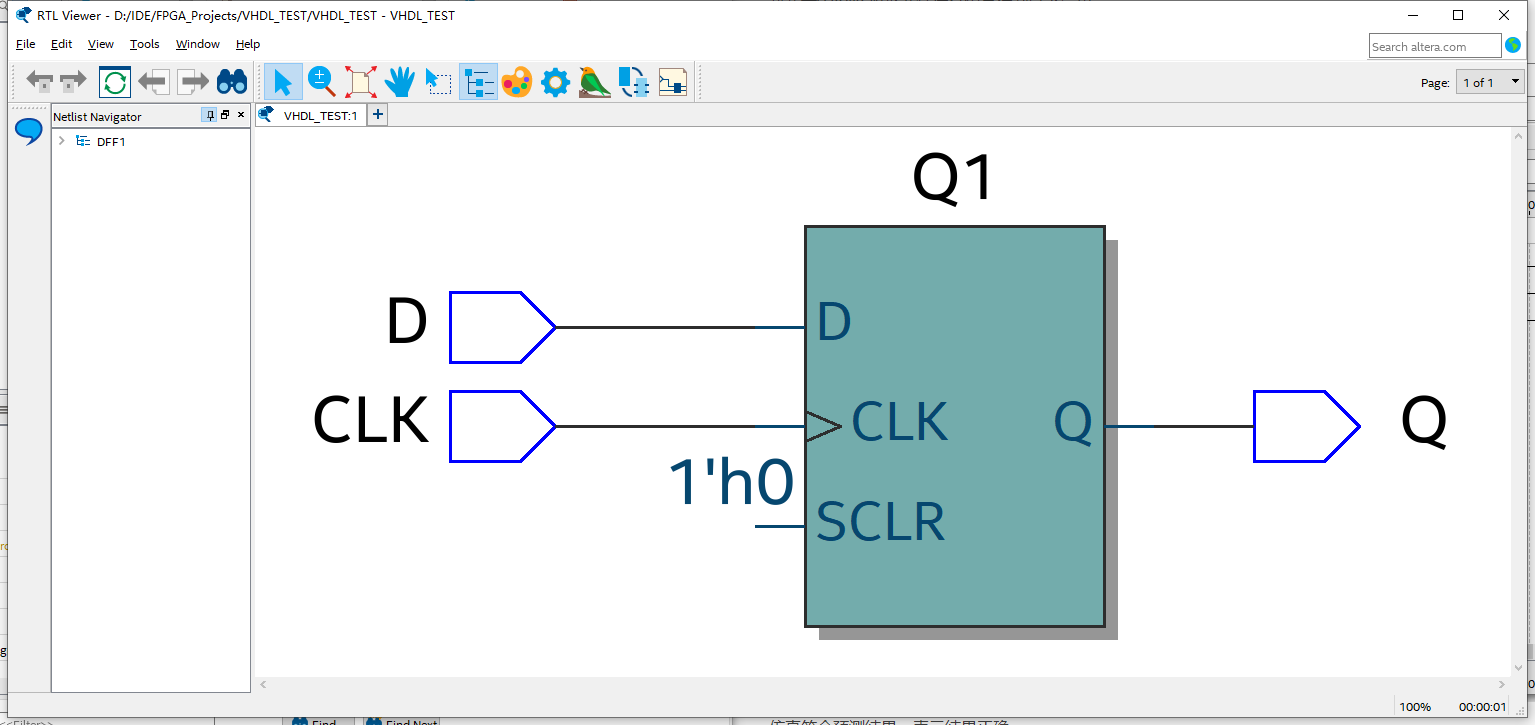

三、应用QuartusII 完成基本时序电路的设计

1. 触发器

在实际的数字系统中往往包含大量的存储单元,而且经常要求他们在同一时刻同步动作,为达到这个目的,在每个存储单元电路上引入一个时钟脉冲(CLK)作为控制信号,只有当CLK到来时电路才被“触发”而动作,并根据输入信号改变输出状态。把这种在时钟信号触发时才能动作的存储单元电路称为触发器,以区别没有时钟信号控制的锁存器。

**实验内容1:**用VHDL文本设计触发器,设计触发器(使用例4-1),给出程序设计、软件编译、仿真分析、硬件测试及详细实验过程。

**实验原理:**由数电知识可知,D触发器由输入的时钟信号(CLK)、数据输入口(D)和数据输出(Q)构成。本程序通过进程监视CLK和D\,当CLK为上升沿的时候,将D赋值给Q,要完成这个赋值操作,必须再借助一个信号S来进行值的传递。

1.1 代码

新建一个VHDL文件,并输入下列代码

LIBRARY IEEE ;

--使用IEEE库

USE IEEE.STD_LOGIC_1164.ALL ;

--使用IEEE库中STD_LOGIC_1164中的所有内容

ENTITY DFF1 IS

--实体DDF1是

PORT (CLK : IN STD_LOGIC ;

--输入引脚CLK,输入模式为STD_LOGIC(因为是时序逻辑电路所以不能使用BIT输入模式)

D : IN STD_LOGIC ;

--输入引脚D,输入模式为STD_LOGIC

Q : OUT STD_LOGIC );

END DFF1;

ARCHITECTURE bhv OF DFF1 IS

--DFF1的逻辑行为模式为:

SIGNAL Q1 : STD_LOGIC ; --类似于在芯片内部定义一个数据的暂存节 点

BEGIN

PROCESS (CLK,Q1)

--PROCESS进程 (clk,rst)为敏感信号列表:敏感信号中的某个信号发生变化,PROCESS中的代码就顺序执行一次。类似与C中的条件循环代码,VHDL的条件为信号的变化,这里就是说时钟信号的上升下降沿的每次出现,或者Q1每变一次程序就会执行一次

BEGIN

IF CLK'EVENT AND CLK = '1'THEN

--如果CLK发生了变化,那么返回布尔值TRUE,以此来判断是否出现了上升沿,即即CLK是否='1'

Q1 <= D ;

--如果CLK=1那么就把D的值赋予给Q1

--“<=”给信号赋值,“:=”给变量赋值

END IF;

--IF语句是用于顺序代码的,只能用于PROCESS,FUNCTION,PROCEDURE中。 没什么好讲的,记住就可以了。

END PROCESS ;

Q <= Q1 ; --将内部的暂存数据向端口输出(双横线--是注释符号)

END bhv;

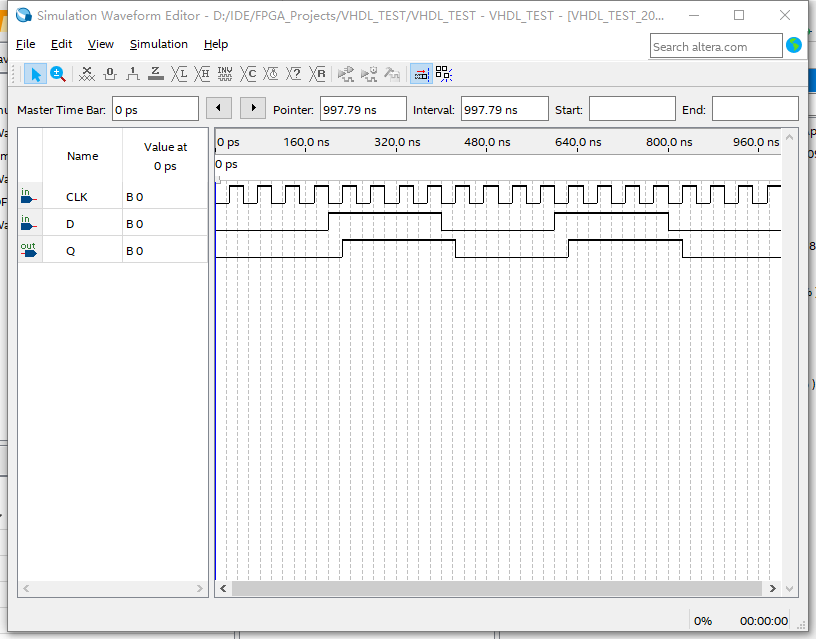

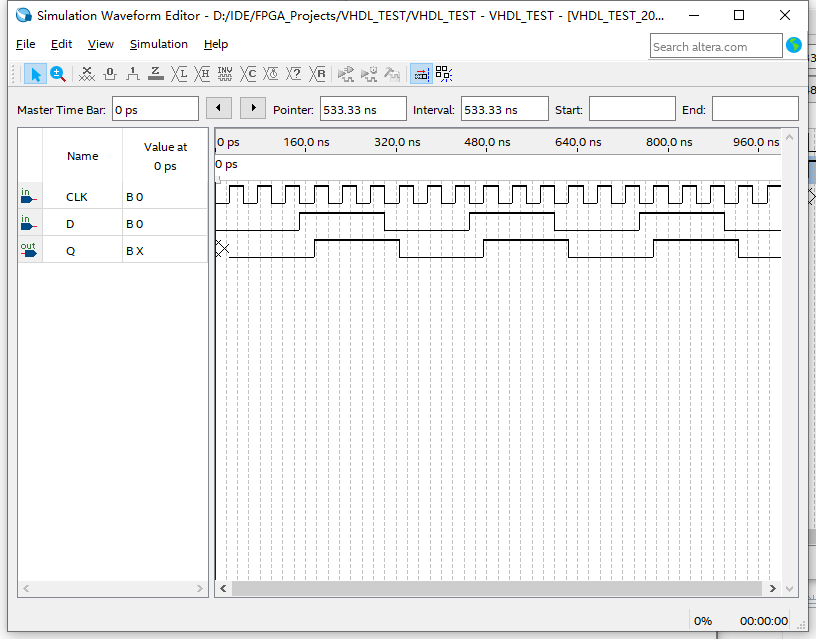

1.2 仿真

新建一个VWF波形文件进行仿真得到以下结果

**仿真预测:**输入一组波形,当且仅当CLK为上升沿的时候,Q输出D的值;否则,Q保持原值不变。

仿真符合预测结果,表示结果正确

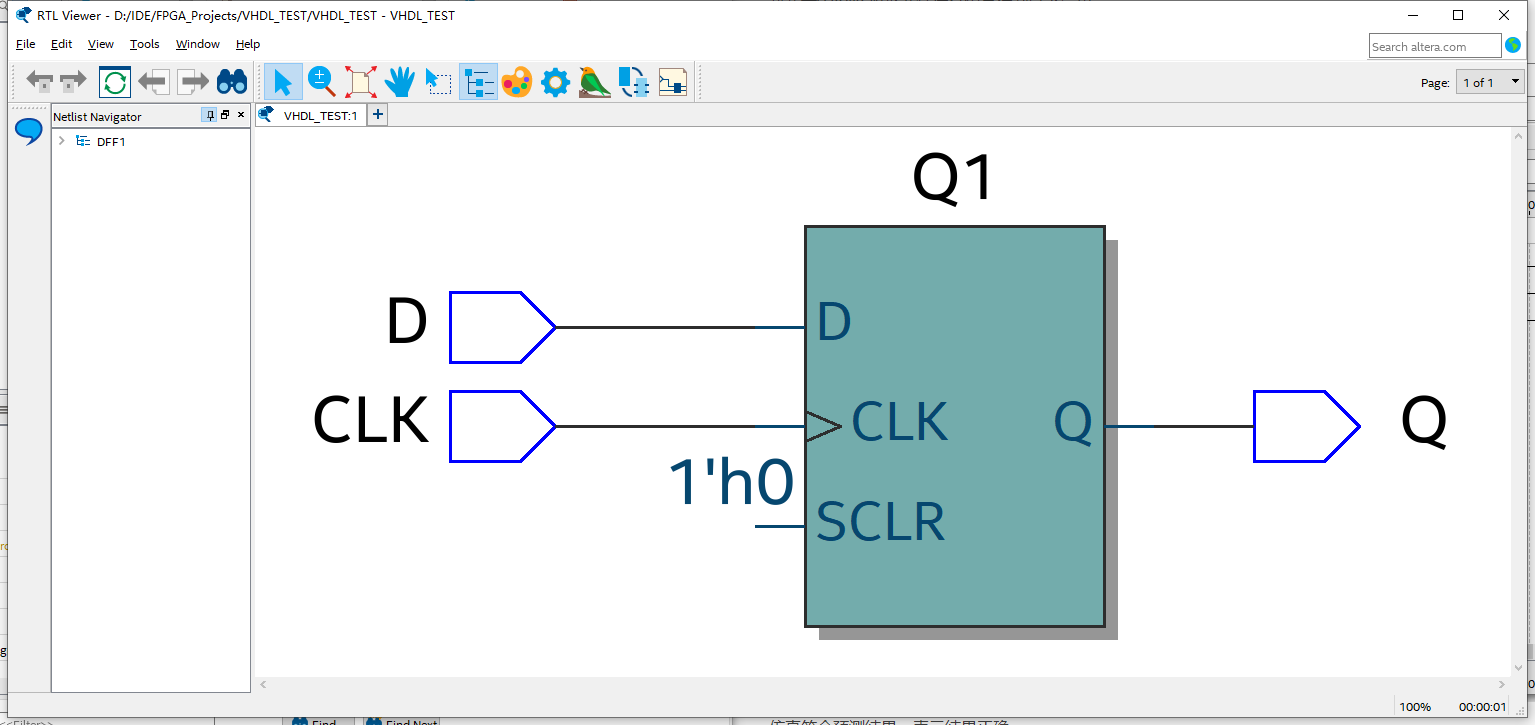

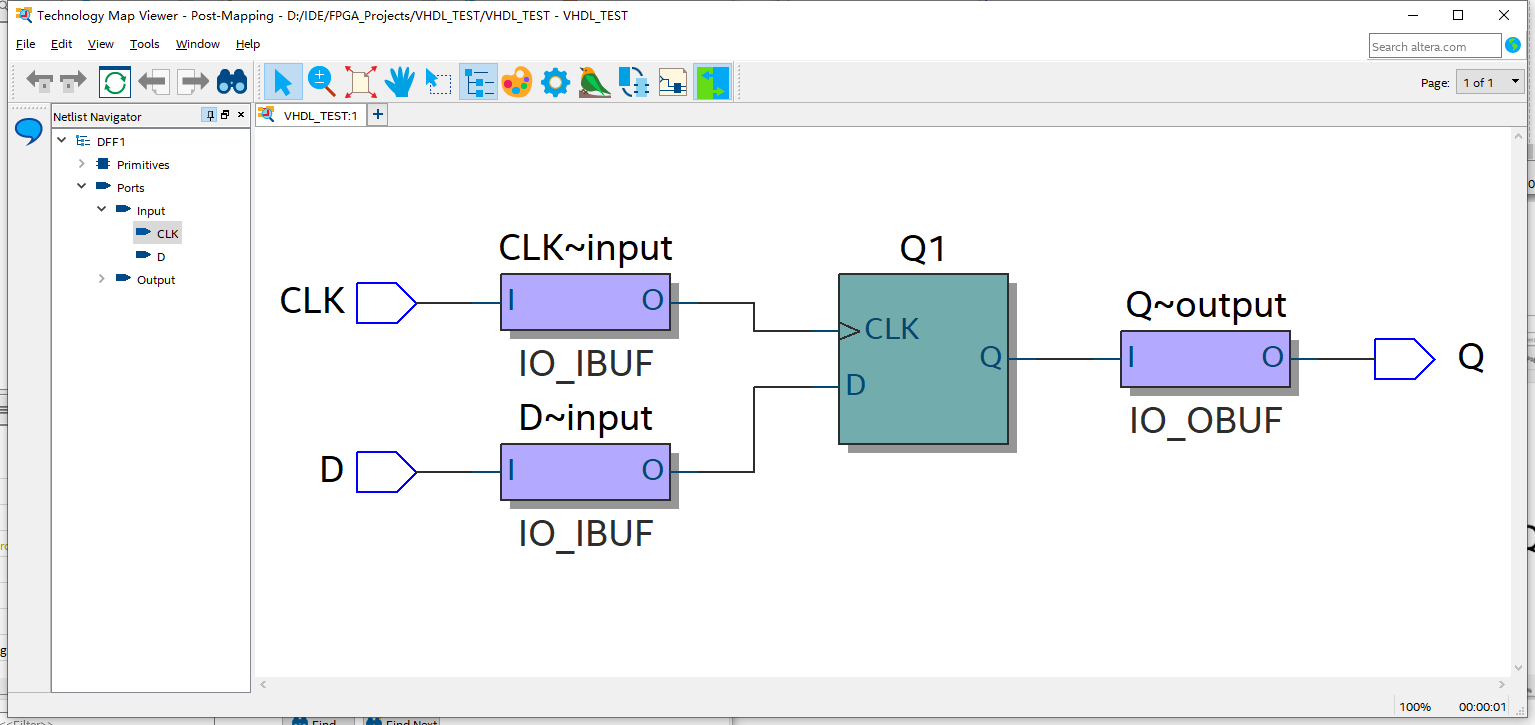

1.3 RTL电路与门电路

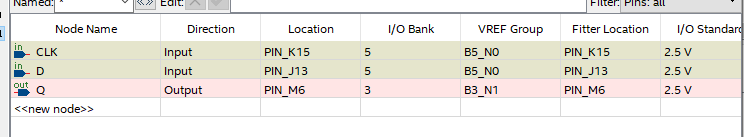

1.4 硬件测试

-

绑定引脚

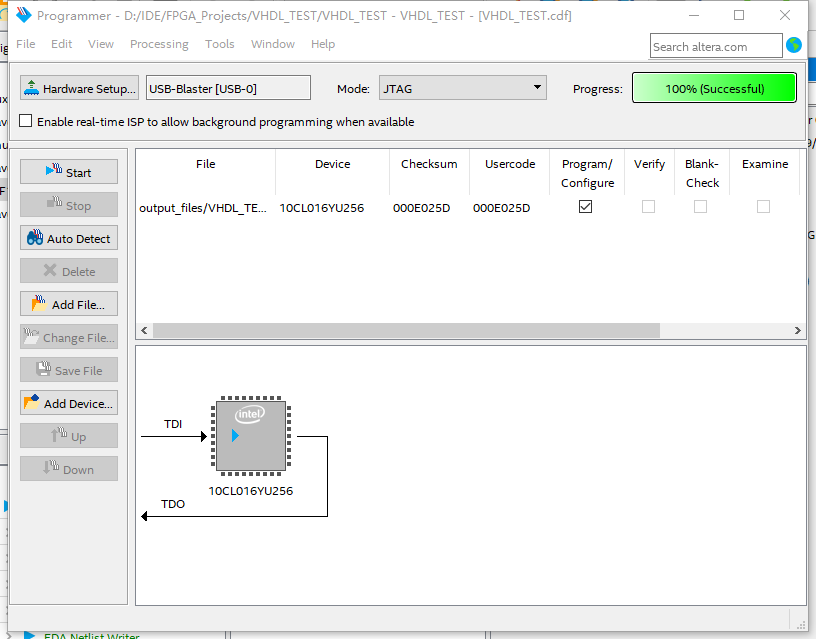

clk与D分别绑定在SW1-2,Q绑定与LED1

-

下载测试

-

仿真预测,当CLK处于上升沿时将D的值赋予Q否则Q保持不变

与预测结果一致,实验成功

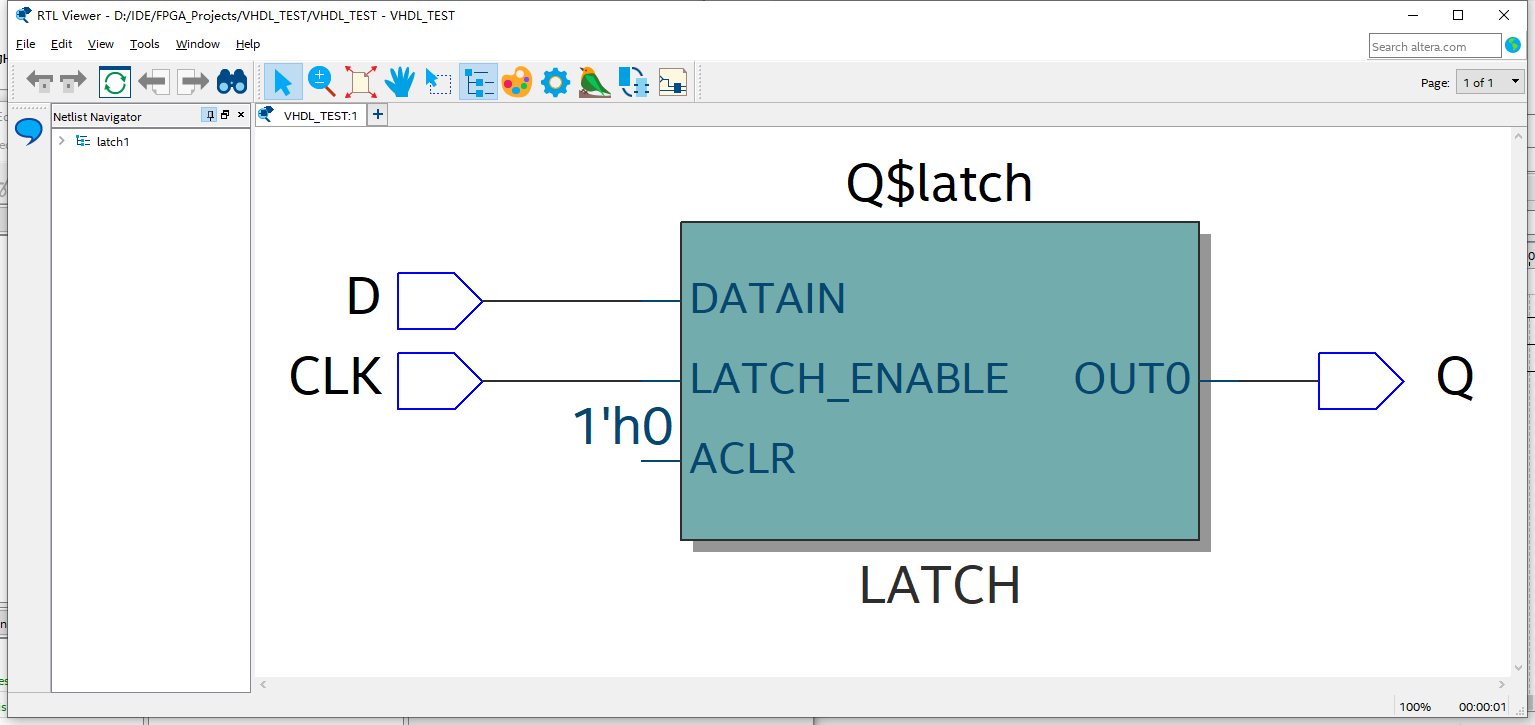

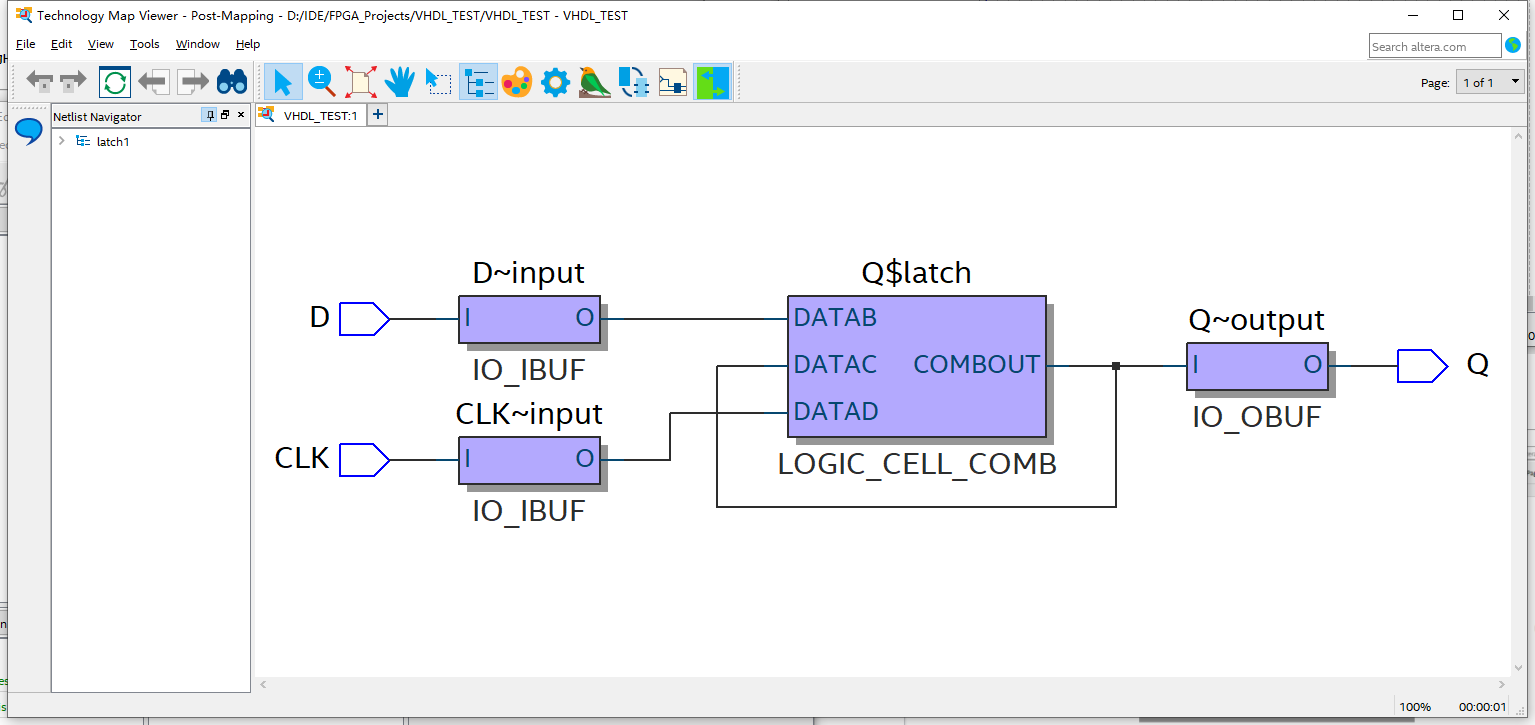

2. 锁存器

锁存器(Latch)是一种对脉冲电平敏感的存储单元电路,它们可以在特定输入脉冲电平作用下改变状态。锁存,就是把信号暂存以维持某种电平状态。锁存器的最主要作用是缓存,其次完成高速的控制器与慢速的外设的不同步问题,再其次是解决驱动的问题,最后是解决一个 I/O 口既能输出也能输入的问题。锁存器是利用电平控制数据的输入,它包括不带使能控制的锁存器和带使能控制的锁存器。

2.1 代码

新建VHDL文件latch1,并输入下列代码

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ;

ENTITY latch1 IS

--实体 latch1 是

PORT (CLK : IN STD_LOGIC ;

--CLK为输入引脚,输入模式为STD_LOGIC

D : IN STD_LOGIC ;

--D为输入引脚,输入模式为STD_LOGIC

Q : OUT STD_LOGIC );

--Q为输出引脚,输出模式为STD_LOGIC

END latch1;

ARCHITECTURE bhv OF latch1 IS

--latch1的逻辑行为模式是

BEGIN

PROCESS (CLK,D)

BEGIN

IF CLK = '1' --电平触发型寄存器

THEN Q <= D ;

--当CLK处于上升沿时,将D的值赋予给Q

END IF;

END PROCESS ;

END bhv;

2.2 仿真

新建波形文件并进行仿真

2.3 查看RTL电路与门电路

2.4 下载测试

直接上测试结果,不然太墨迹了

测试结果与预测结果相同,试验成功

四、总结

通过第二次学习的三个实验内容对我的FPGA的基础知识很有帮助。

五、参考文章

《实验一:1位全加器设计—— 原理图与VHDL设计初步》

《STEP-CYC10 硬件手册》

STEP 10资源参考: