Xilinx_ROM_IP核的使用

说明:coe文件的制作,ROM文件的读取。

环境:Vivado2018.3。

IP核:Block Memory Generator。

参考手册:

UG473: 7 Series FPGAs Memory Resources

PG058 :Block Memory Generator v8.4。

需要软件:

Guagle_wave

UltraEdit

1.coe文件的制作(可制作指定波形)

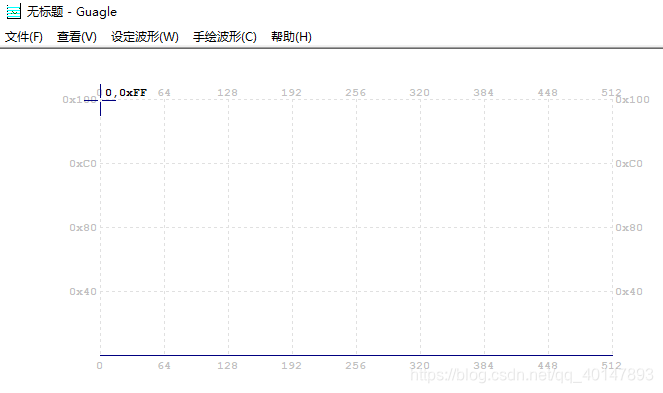

1.打开Guagle_wave软件

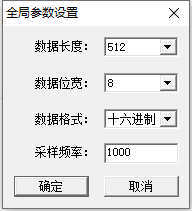

2. 菜单栏–>查看–>全局参数设定

可以设置数据长度和数据位宽。

3.设置波形或者手绘波形

4.保存为.mif文件(点击保存,别点击另存为,可能会导致空文件)

5.改后缀为.coe

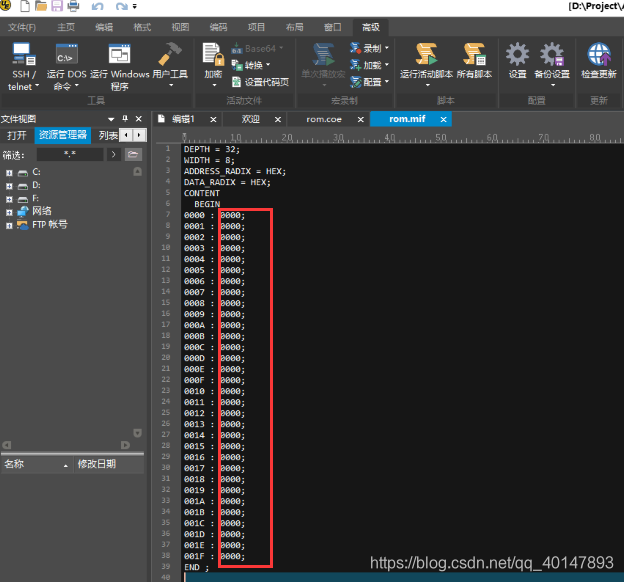

6.用UltraEdit打开文件做以下更改

只保留红框数据,数据后面分号改为逗号,最后一个数据后为逗号,并在最前面添加

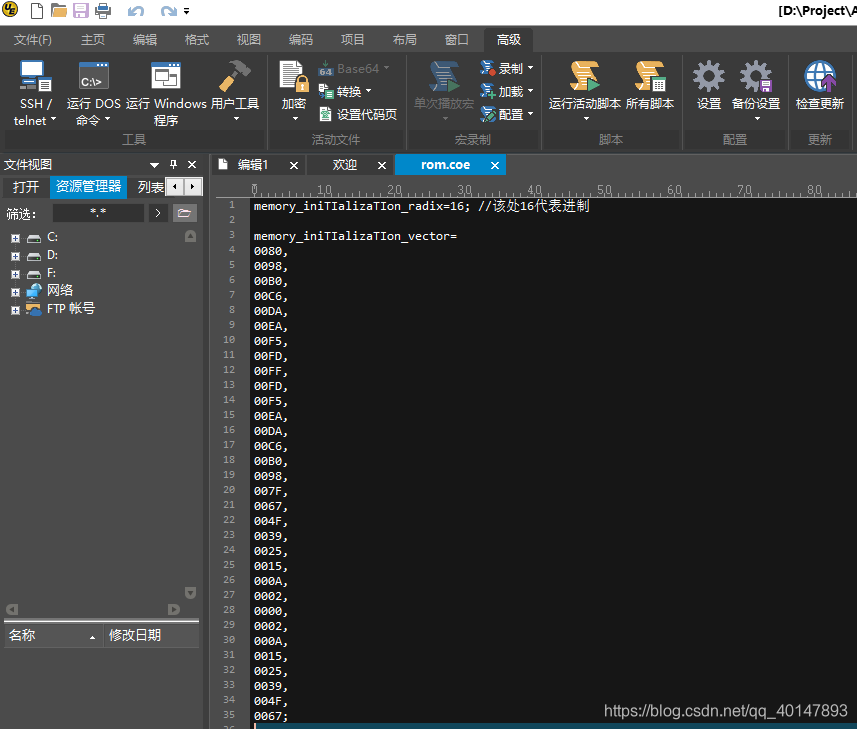

memory_iniTIalizaTIon_radix=16; //该处16代表进制

memory_iniTIalizaTIon_vector=

↓

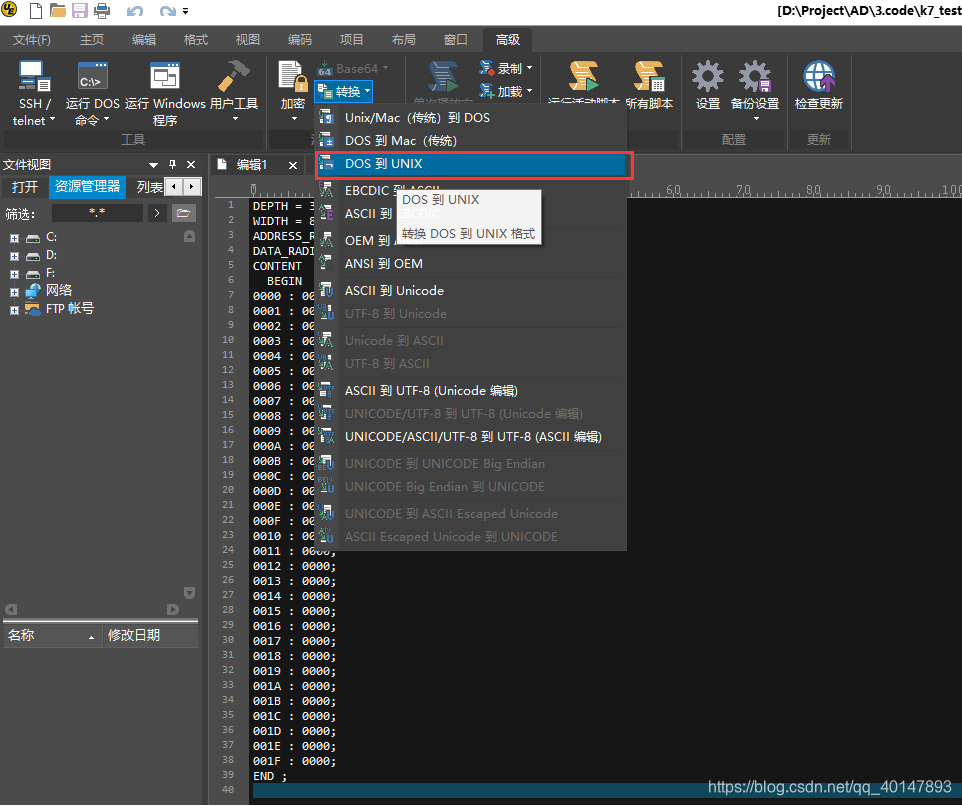

7.最后一步

由于coe格式文件最初为unix系统,在windows系统中需要转化以下格式

coe文件制作完成,这样有利于生成指定的波形,如果ROM只用需要生成指定的值,手动输入也可以。

2.ROM IP核配置及应用

只读存储器(Read-Only Memory,ROM)以非破坏性读出方式工作,只能读出无法写入信息。

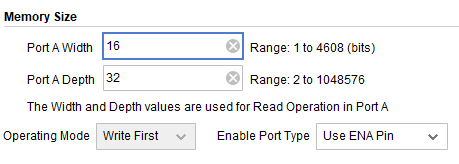

IP核深度与宽度配置:

ROM端口:

ROM读代码:

module top

(

input clk_25m

);

/********************************************************

* 时钟

*********************************************************/

wire clk_100m;

wire clk_locked;

clk_wiz_0 clk

(

.clk_out1(clk_100m),

.locked(clk_locked),

.clk_in1(clk_25m)

);

/********************************************************

* 复位

*********************************************************/

wire RSTn;

assign RSTn = clk_locked;

/********************************************************

* ROM

*********************************************************/

wire rom_ena;

wire[4:0] rom_addra;

wire[15:0] rom_douta;

reg rom_ena_r;

reg[4:0] rom_addra_r;

assign rom_ena = rom_ena_r;

assign rom_addra = rom_addra_r;

reg[7:0] rom_cnt;

//ROM深度为32、宽度为16

always@(posedge clk_25m or negedge RSTn)

begin

if(!RSTn)

begin

rom_cnt <= 8'd0;

rom_ena_r <= 1'b0;

rom_addra_r <= 5'h00;

end

else

begin

rom_ena_r <= 1'b1;

rom_cnt <= (rom_cnt==8'd31)?8'd0:rom_cnt+8'd1;

rom_addra_r <= rom_cnt;

end

end

blk_mem_gen_0 rom (

.clka(clk_25m), // input wire clka

.ena(rom_ena), // input wire ena

.addra(rom_addra), // input wire [4 : 0] addra

.douta(rom_douta) // output wire [15 : 0] douta

);

/********************************************************

* ila

*********************************************************/

ila_0 ila (

.clk(clk_100m), // input wire clk

.probe0(clk_25m), // input wire [0:0] probe0

.probe1(rom_ena), // input wire [0:0] probe1

.probe2(rom_addra), // input wire [4:0] probe2

.probe3(rom_douta) // input wire [15:0] probe3

);

endmodule

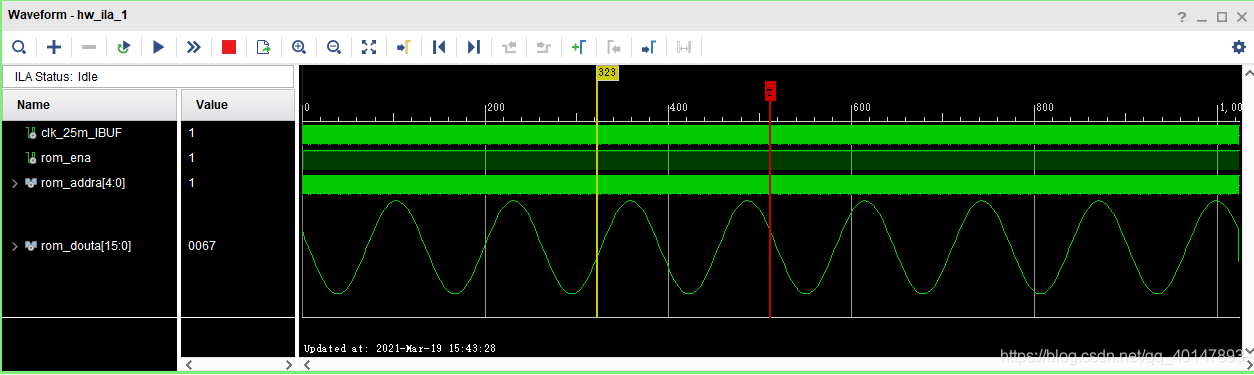

波形: