最近做的项目中用到了RS编码,FPGA代码中是通过调用Reed-Solomon Encoder IP核来实现的。这里以R-S(255,223)为例,分别对单通道和多通道两种情况进行了仿真验证,下面给出具体的fpga ip核配置以及仿真结果。

(一)单通道

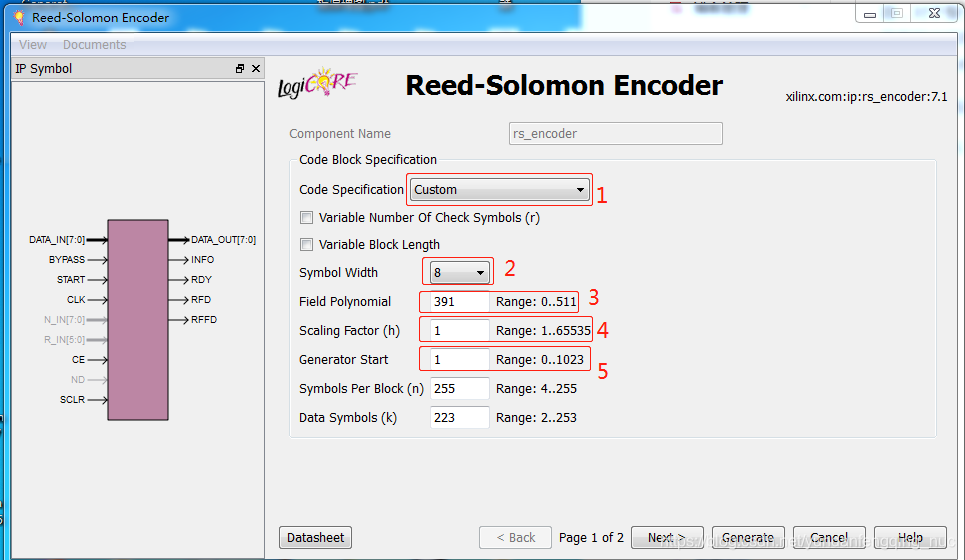

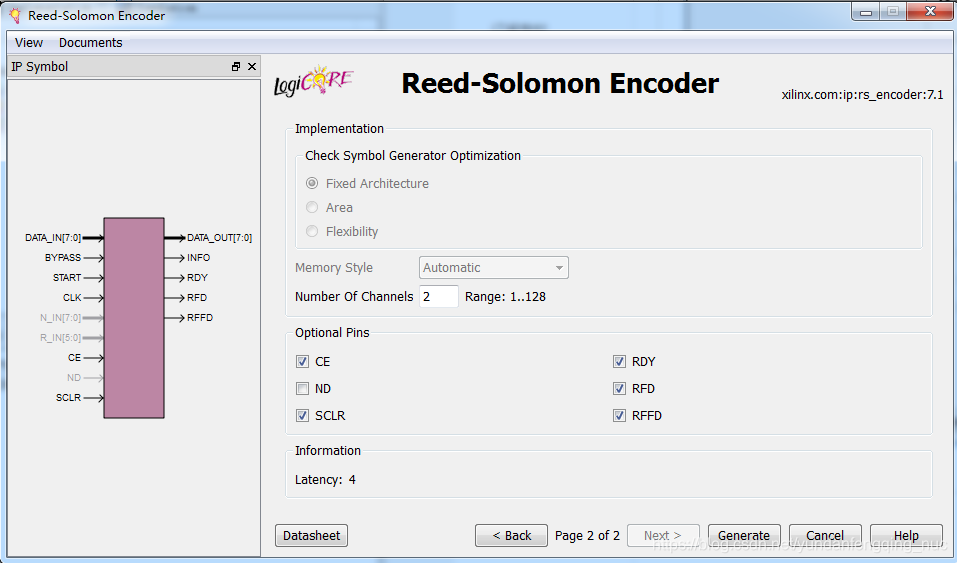

FPGA中RS IP核的配置如下图所示:

标注1:编码说明,这里选择Custom,后面将与CCSDS进行对比。

标注2:符号宽度:这里选择8。

标注3:这里与域生成多项式保持一致,本例中域生成多项式为:F(x) = x8 + x7 + x2 + x + 1(在GF(2)上定义));

x8 + x7 + x2 + x + 1 => 110000111 => 391,所以这里设置为391。

标注4:比例因子,这里设置为1,matlab仿真与fpga仿真结果一致。

标注5:这里设置为1,因为matlab中rsenc函数生成多项式下标默认从1开始,为了与matlab保持一致,这里设置为1。

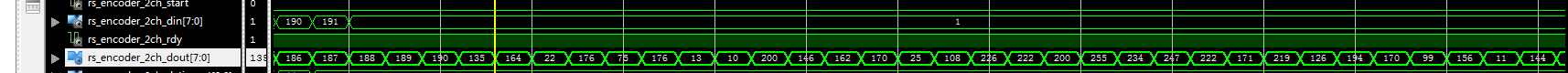

这里分别对两组数的rs编码进行了fpga仿真验证,其中一组数为从1开始依次递增的奇数数组,另一组数为从2开始依次递增的偶数数组,下图为fpga仿真结果

奇数组仿真结果输出为:135 22 75 13 200 162 25 226 200 234 222 219 194 99 11 14 5 118 142 109 29 128 78 200 129 148 85 95 252 94 204 223

偶数组仿真结果输出:164 176 176 10 146 170 108 222 255 247 171 126 170 156 144 145 74 16 179 45 151 199 16 12 219 236 139 54 83 128 190 26

这里给出fpga代码和matlab代码:

reg [7:0] dat_in ;

reg [7:0] dat_in1 ;

reg [7:0] dat_in2 ;

reg [9:0] dat_cnt ;

reg flag1 ;

reg flag2 ;

always @ (posedge I_clk or posedge I_rst)

begin

if(I_rst)

dat_cnt <= 0;

else if(dat_cnt < 512)

dat_cnt <= dat_cnt + 1;

else

dat_cnt <= 600;

end

always @ (posedge I_clk or posedge I_rst)

begin

if(I_rst)

begin

flag1 <= 0;

flag2 <= 0;

end

else

case(dat_cnt)

1:begin flag1 <= 1; flag2 <= 0;end

224:begin flag1 <= 0; flag2 <= 0;end

256:begin flag1 <= 0; flag2 <= 1; end

479:begin flag1 <= 0; flag2 <= 0;end

default:begin flag1 <= flag1; flag2 <= flag2;end

endcase

end

always @ (posedge I_clk or posedge I_rst)

begin

if(I_rst)

dat_in1 <= 1;

else if(flag1)

dat_in1 <= dat_in1 + 2;

else

dat_in1 <= dat_in1;

end

always @ (posedge I_clk or posedge I_rst)

begin

if(I_rst)

dat_in2 <= 2;

else if(flag2)

dat_in2 <= dat_in2 + 2;

else

dat_in2 <= dat_in2;

end

always @ (posedge I_clk or posedge I_rst)

begin

if(I_rst)

dat_in <= 0;

else if(flag1)

dat_in <= dat_in1;

else if(flag2)

dat_in <= dat_in2;

else

dat_in <= dat_in;

end

assign start = ((dat_cnt == 3) || (dat_cnt == 258))? 1 : 0;

rs_encoder rs_encoder_inst(

.sclr (I_rst),

.ce (1'b1),

.rfd (rfd),

.start (start),

.rdy (rdy),

.clk (I_clk),

.rffd (rffd),

.info (info),

.bypass (1'b0),

.data_in (dat_in),

.data_out (dout)

);

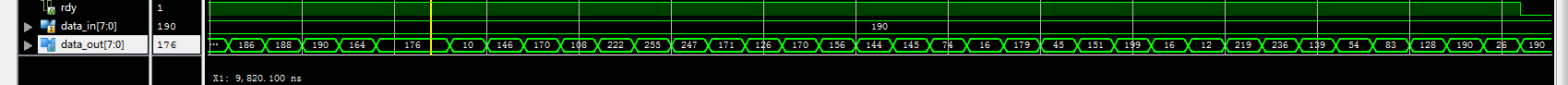

(二)多通道,这里以2通道为例

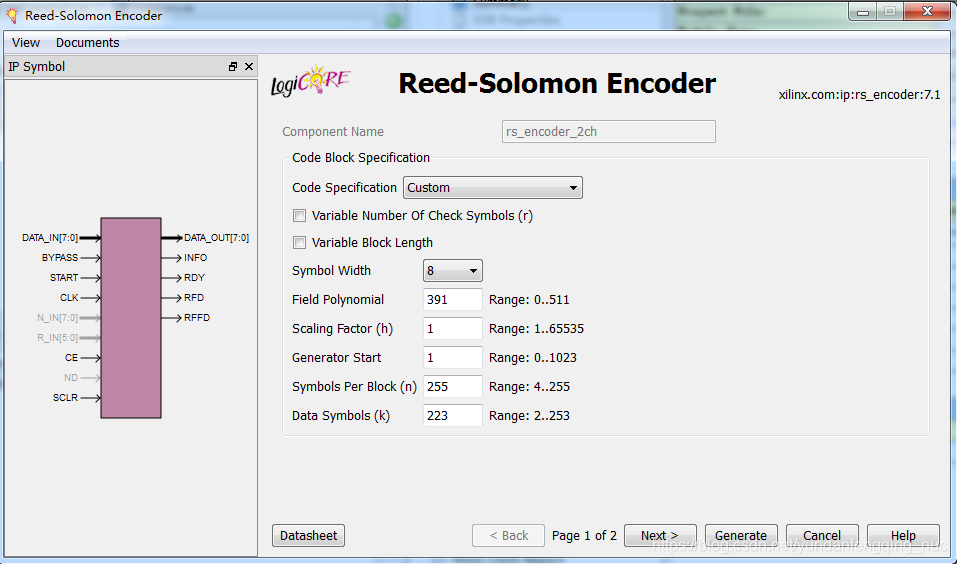

此时RS IP核配置如下图:

2通道时,输入数据为从1开始依次递增1的一组数据,2个通道输入的数据个数为223*2=446

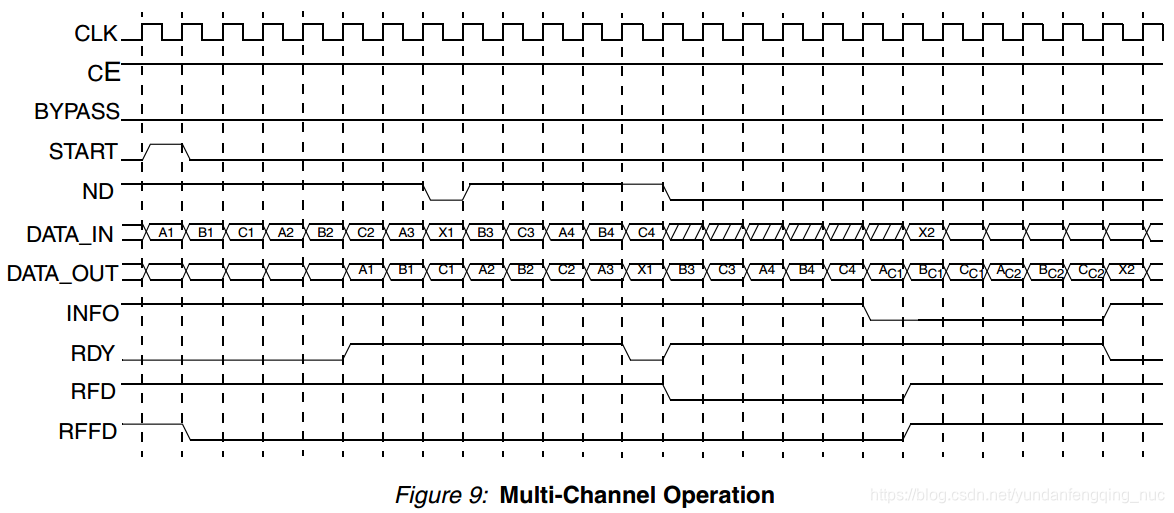

多通道时RS IP核编码时序如上图所示,输入数据依次为通道1的数据1,通道2的数据1,通道1的数据2,通道2的数据2,。。。。。,输出结果check symbol部分依次为通道1的check symbol1,通道2的check symbol2,通道1的check symbol2,通道2的check symbol2,。。。。

FPGA仿真结果为:135 164 22 176 75 176 13 10 200 146 162 170 25 108 226 222 200 255 234 247 222 171 219 126 194 170 99 156 11 144 14 145 5 74 118 16 142 179 109 45 29 151 128 199 78 16 200 12 129 219 148 236 85 139 95 54 252 83 94 128 204 190 223 26