Xilinx AXI Uartlite IP核的使用

说明:通过AXI Uartlite IP核实现FPGA与PC的串口通信。

环境:Vivado2018.3。

IP核:AXI Uartlite(2.0)。

参考手册:pg142-axi-uartlite。

AXI协议资料:AXI

1.串口通信协议

1.1基础知识:

| 因 | 果 |

|---|---|

| 系统时钟-50M | 时钟周期 1 50 ∗ 1 0 6 { {\rm{1}} \over { {\rm{50*1}}{ {\rm{0}}^{\rm{6}}}}} 50∗1061 |

| 假设1个时钟周期可以计数1次(其实FPGA就是这样) | 50M时钟1s计数50 000 000个 |

| 系统时钟-50M | 计1个数需要 1 50 ∗ 1 0 6 { {\rm{1}} \over { {\rm{50*1}}{ {\rm{0}}^{\rm{6}}}}} 50∗1061s |

| 波特率-115200 | 1s传输二进制的位数115200bit |

| 波特率-115200 | 传输1bit需要 1/115200s=8.68us |

| 50M系统时钟------波特率为115200 | 传输1bit需要计数 ( 50 ∗ 1 0 6 / 115200 ) = 434 ({\rm{50*1}}{ {\rm{0}}^{\rm{6}}}/{\rm{115200}}) = 434 (50∗106/115200)=434 |

以上重点是推导出50M系统时钟—波特率为115200条件下传输1bit需要计数个数为434。

1.2串口传输格式

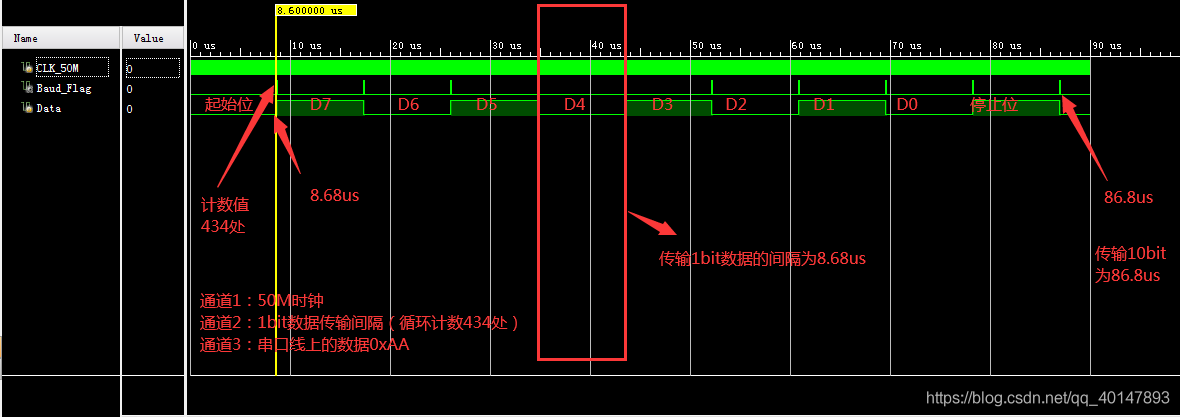

●我们通常用的串口传输格式为:1bit起始位+8bit数据位+1bit停止位(无奇偶校验位),如下图所示:

所以传输1Byte数据串口需要传输10bit数据。上面计算得传输1Bit需要的时间为8.68us,则传输1Byte需要时间为8.68*10=86.8us。

1.3深入理解波特率

由基础知识知50M系统时钟—波特率为115200条件下传输1bit需要计数个数为434。那么1Byte(串口传输格式为:1bit起始位+8bit数据位+1bit停止位)是不是循环计数10次434就可以传输完毕。

直接上图:图中描述了1Byte数据传输的示意图,重点都在图里!!!。

2.串口是怎样传输数据的

➹通过逻辑分析仪捕捉串口传输的数据来了解串口传输数据的实质。

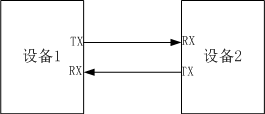

串行接口简称为串口,串行接口 (Serial Interface)是指数据一位一位地顺序传送。实现双向通信就需要一对传输线,即TX与RX线。

电路连接方式:

串口如果要实现双向传输,则设备1与设备2,TX与RX要交叉相连。

2.1串口数据解析

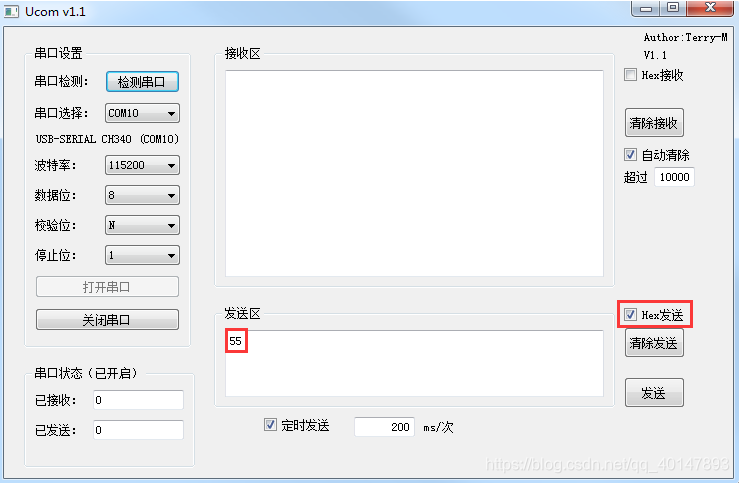

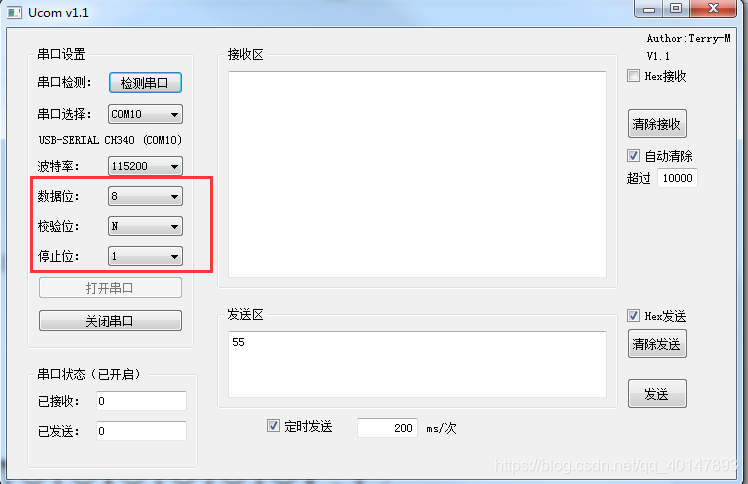

利用电脑端的串口助手通过CH340串口模块将数据0x55发送出去,并通过逻辑分析仪来捕捉数据。下图为串口发送的数据,是以十六进制(hex)形式发送的。

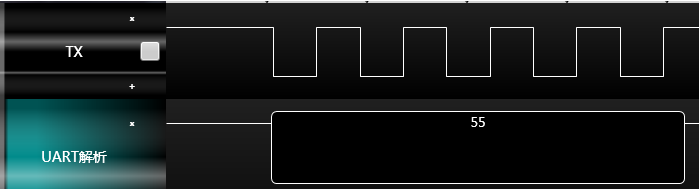

逻辑分析仪捕捉数据:

我们看到逻辑分析仪成功将数据0x55捕捉到。接下来看串口的数据构成是怎样的。

查阅资料,串口传输一帧数据如下图所示:

所谓串口的一帧数据即串行的发送一次数据(比如0x55(0101_0101))时TX数据线上的电平变化。由上图可知串口一帧数据的构成为:起始位(1bit)+数据(8bit)+奇偶校验位+停止位(1bit),8bit数据传输的方式为先低位(LSB)再高位(MSB)即通过(D0_D1_D2_D3_D4_D5_D6_D7)的顺序将数据依次放置在TX数据线上。我们再看我们所用的串口助手:

我们的设置为传输数据位为8bit,检验位为0bit即没有校验位,停止位为1bit。所以我们串口一帧数据的构成为:起始位(1bit)+数据(8bit)+停止位(1bit),所以串口一帧数据的传输单位为10bit,平时我们所说的串口传输单位为1Byte即8bit是指传输的有效数据,即起始位(1bit)+数据(8bit)+停止位(1bit)中的8bit数据,那为什么要多此一举的在收尾处各加1bit的数据呢,其实是为了接收设备能去正确的接收到8bit的有效数据,起始位相当于一帧数据的帧头,停止位相当于一帧数据的帧尾。

3.AXI Lite协议

3.1 AXI介绍

AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。它的地址/控制和数据相位是分离的,支持不对齐的数据传输,同时在突发传输中,只需要首地址,同时分离的读写数据通道、并支持Outstanding传输访问和乱序访问,并更加容易进行时序收敛。AXI 是AMBA 中一个新的高性能协议。AXI 技术丰富了现有的AMBA 标准内容,满足超高性能和复杂的片上系统(SoC)设计的需求。

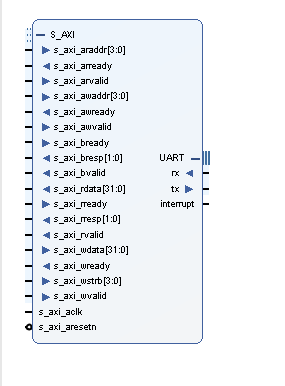

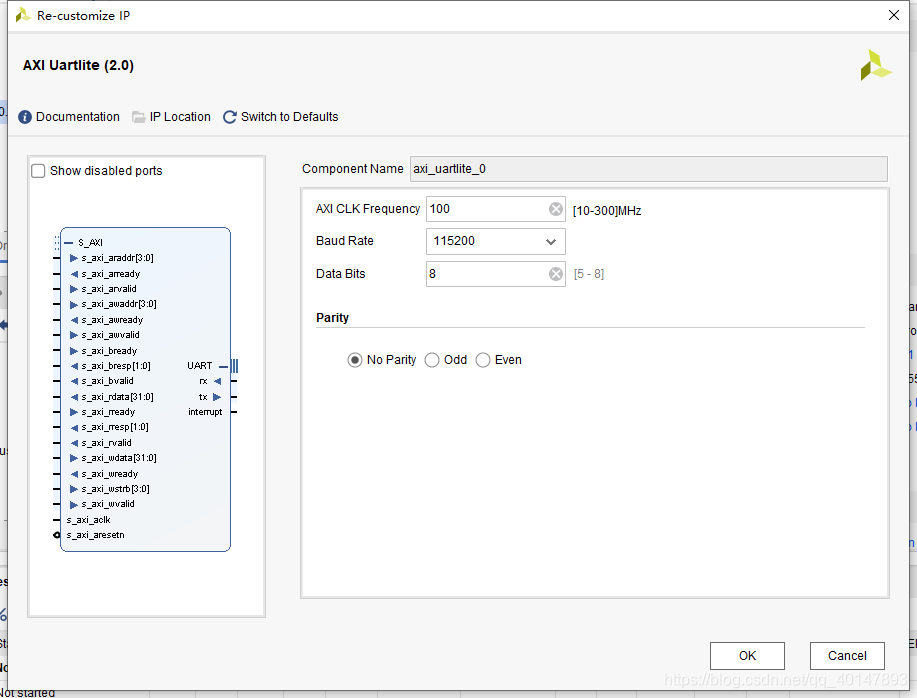

3.2 Uart_AXI_Lite接口

打开IP核如下:

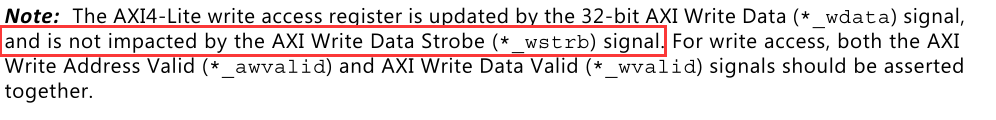

注意:s_axi_wstrb在该IP中不起作用。

3.3 AXI-Lite接口介绍

AXI4-Lite接口是AXI4接口的一个子集

AXI4-Lite特点:

1、所有的传输突发均为1。

2、所有数据访问的大小与数据总线的宽度相同。

3、支持32bit或64bit数据总线宽度。

4、所有访问等效于AWCACHE或ARCACHE等于b0000。

不支持独占访问。

AXI4-Lite不支持的信号

AWLEN,ARLEN

突发长度定义为长度1,等于AWLEN或

ARLEN等于零。

AWSIZE,ARSIZE

所有访问都定义为与数据总线的宽度相同。支持固定的32位或64位数据总线宽度。

AWBURST, ARBURST

突发类型没有意义,因为突发长度为1,因此所有的突发类型相同。

AWLOCK, ARLOCK

所有访问都定义为“普通访问”,等效于AWLOCK或 ARLOCK为b0。

AWCACHE , ARCACHE

所有访问等效于AWCACHE或 ARCACHE等于b0000。

WLAST, RLAST

所有突发长度为1,等价于WLAST, RLAST总是被断言。

RRESP, BRESP

RRESP、BRESP不支持EXOKAY响应通道。

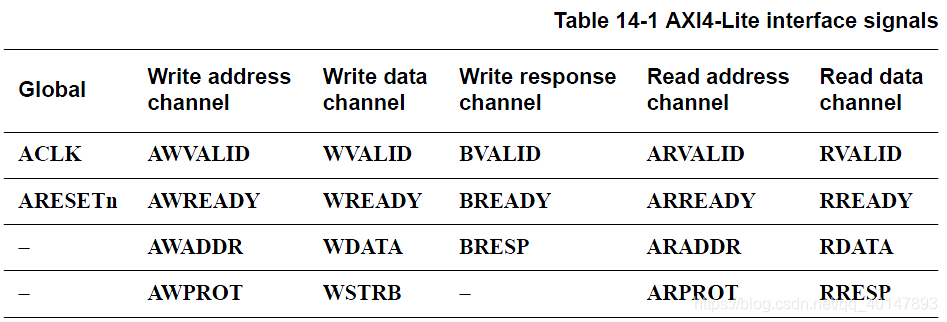

3.4 AXI-Lite接口信号

全局信号:

| ACLK | 主 | 全局时钟信号,所有的信号都在此上升沿采样 |

|---|---|---|

| ARESETn | 主 | 全局复位信号,该信号低电平有效 |

写地址通道:

| AWVALID | 主 | 写地址有效。表示有效的写地址和控制信息。1:地址可用、0:地址不可用 |

|---|---|---|

| AWREADY | 从 | 接收地址准备。表明从机已经准备好接收地址信息。1:从机准备就绪、0:从机未准备就绪 |

| AWADDR | 主 | 写地址。写地址总线给出写突发中第一次传输的地址。 |

| AWPROT | 主 | 保护类型 |

写数据通道:

| WVALID | 主 | 写有效。表明写数据有效。1:写数据可用、0:写数据不可用。 |

|---|---|---|

| WREADY | 从 | 接收数据准备。1:从机准备就绪、0:从机为准备就绪、 |

| WDATA | 主 | [31:0],写数据。写数据总线的宽度可以为8、16、32、64、128、256、512或1024。 |

| WSTRB | 主 | [3:0],写数据选择。该信号指示存储器中更新的字节通道。WSTRB[n]对应选通WDATA[8×n]+7:(8×n)。 |

写响应通道:

| BVALID | 从 | 写入响应有效。1:写响应可用、0:写响应不可用。 |

|---|---|---|

| BREADY | 主 | 接收响应准备就绪。1:主机准备接收就绪、0:主机未准备接收就绪 |

| BRESP | 从 | [1:0]写响应。该信号指示写事务的状态。允许的响应为OKAY、EXOKAY、SLVERR、DECERR |

读地址通道:

| ARVALID | 主 | 读地址有效。1:读取地址有效、0:读地址无效 |

|---|---|---|

| ARREADY | 从 | 读取地址准备就绪。1:从机地址准备就绪、0:从机地址未准备就绪。 |

| ARADDR | 主 | [31:0],读取地址。读取地址总线提供读取突发事务的初始地址 |

| ARPROT | 主 | 保护类型 |

读数据通道:

| RVALID | 从 | 读数据有效。1:读取数据可用、0:读取数据不可用 |

|---|---|---|

| RREADY | 主 | 读取数据就绪。1:主机准备就绪、0:主机为准备就绪。 |

| RDATA | 从 | [31;0],读取数据。读取数据总线的宽度可以为8、16、32、64、128、256、512或1024。 |

| RRESP | 从 | 读取响应。该信号指示读取传输的状态允许的响应为OKAY、EXOKAY、SLVERR、DECERR |

OKAY、EXOKAY、SLVERR、DECERR:

3.5 AXI-Lite读写

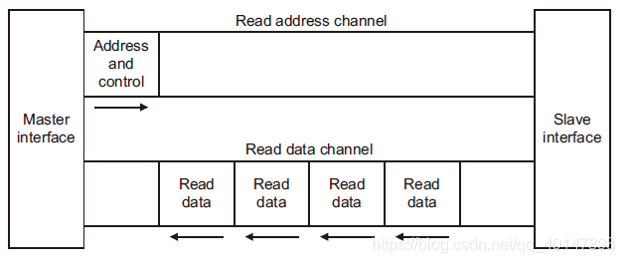

读地址通道:

每个读事务都有自己的地址通道。适当的地址通道携带通信所需的所有地址和控制信息。AXI协议支持以下机制:

可变的突发长度,每个突发长度从1-16个数据。

(连续传输的周期数就是突发长度。)

突发传送的大小为8-1024bit

…

读取数据通道:

读取数据通道可同时传输读取数据和来自设备从设备到主设备的响应信息。

数据总线,可以是8、16、32、64、128、256、512或1024bit。

一个指示读取事务完成状态的读取响应

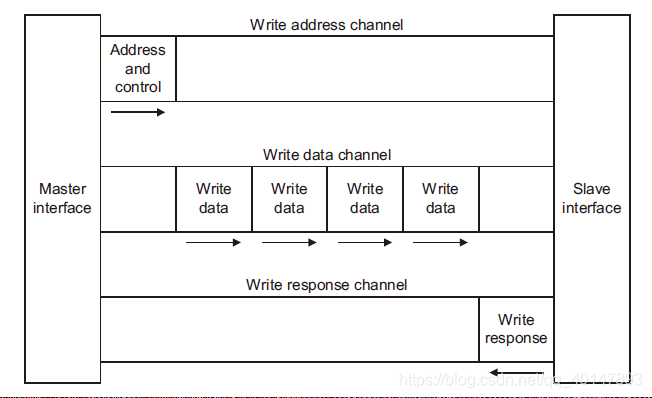

写地址通道:

每个写事务都有自己的地址通道。适当的地址通道携带通信所需的所有地址和控制信息。AXI协议支持以下机制:

可变的突发长度,每个突发长度从1-16个数据。

(连续传输的周期数就是突发长度。)

突发传送的大小为8-1024bit

…

写数据通道:

将写数据从主机传送到从机

数据总线,可以是8、16、32、64、128、256、512或1024bit。

每八个数据位的一个字节通道选通脉冲,指示数据总线的哪个字节有效。

写响应通道:

写通道响应为从设备提供了一种响应事务的方法。所有写事务使用完成信令。

完成信号对于每个脉冲串仅发生一次,而不是针对其中的每个单独的数据传输发生一次突变。

3.6 AXI-Lite握手过程

所有五个通道都使用相同的VLAID/READY握手机制来传输和控制信息。这种双向流量控制机制使主机和从机都可以控制数据和信息的移动速率。主机,指示何时有数据或控制信息。从机,产生READY信号,以指示它接收数据或控制信息。传输仅当VALID和READY信号均为高时。

通道握手信号之间的依赖:

为避免出现死锁情况,必须观察到两者之间存在的依赖关系。

握手信号。

在任何传输中:

●一个AXI组件的VALID信号不得取决于READY信号。

●READY信号可以等待VALID信号的断言。

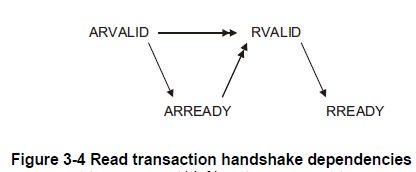

读取握手依赖关系:

| 读取握手信号 | 发起者 | 说明 |

|---|---|---|

| ARVALID | 主 | 读地址有效。1:读取地址有效、0:读地址无效 |

| RVALID | 从 | 读数据有效。1:读取数据可用、0:读取数据不可用 |

| ARREADY | 从 | 读取地址准备就绪。1:从机地址准备就绪、0:从机地址未准备就绪。 |

| RREADY | 主 | 读取数据就绪。1:主机准备就绪、0:主机为准备就绪。 |

从机可以在声明ARREADY之前等待ARVALID声明

从设备必须等待ARVALID和ARREADY都被声明后才能开始

通过声明RVALID返回读取的数据。

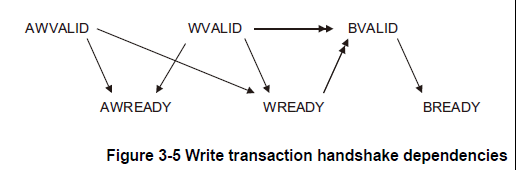

写入握手依赖关系:

| 写入握手信号 | 发起者 | 说明 |

|---|---|---|

| AWVALID | 主 | 写地址有效。表示有效的写地址和控制信息。1:地址可用、0:地址不可用 |

| AWREADY | 从 | 接收地址准备。表明从机已经准备好接收地址信息。1:从机准备就绪、0:从机未准备就绪 |

| WVALID | 主 | 写有效。表明写数据有效。1:写数据可用、0:写数据不可用。 |

| WREADY | 从 | 接收数据准备。1:从机准备就绪、0:从机为准备就绪、 |

| BVALID | 从 | 写入响应有效。1:写响应可用、0:写响应不可用。 |

| BREADY | 主 | 接收响应准备就绪。1:主机准备接收就绪、0:主机未准备接收就绪 |

主机不得在等待从机断言AWREADY或WREADY之前断言AWVALID或WVALID

从机可以在声明AWREADY之前等待AWVALID或WVALID或两者

从机可以在声明WREADY之前等待AWVALID或WVALID或两者

从机必须在声明前等待WVALID和WREADY在BVALID断言之前声明。

握手方式:

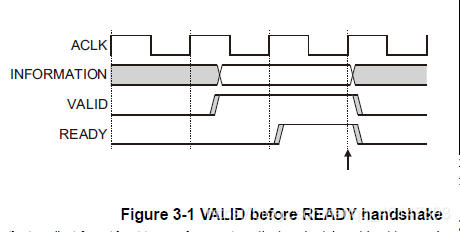

VALID在READY之前:

主机放置数据或控制信号,并将VALID信号驱动为高电平。

来自主机的数据或控制信息保持稳定,直到目标驱动READY信号为高电平,表示它接受数据或控制信息,箭头显示何时开始传输。

在声明VALID之前,不允许等待READY声明。一旦VALID被

断言它必须保持断言直到握手发生。

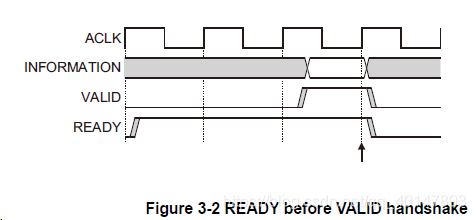

READY在VALID之前:

目标驱动器在数据或控制信息被写入之前就驱动READY为高,这表明从机可以在一个接收器中接受数据或控制信息生效后立即循环。允许在声明相应的READY之前等待VALID声明。 如果声明了READY ,则允许在声明VALID之前取消声明READY 。

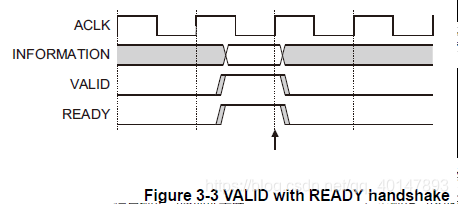

VALID和READY同时:

主机和从机恰好在同一周期内指示他们可以传输数据或控制信息。

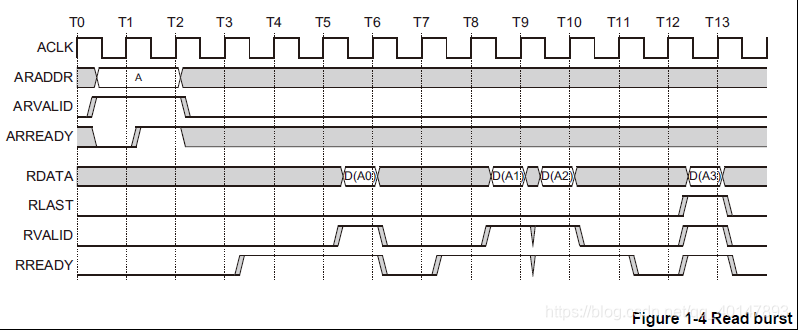

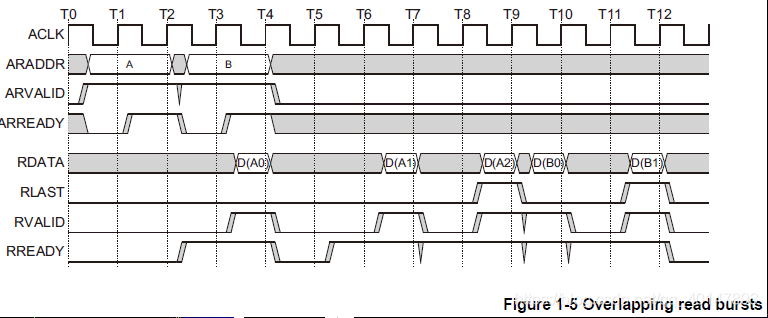

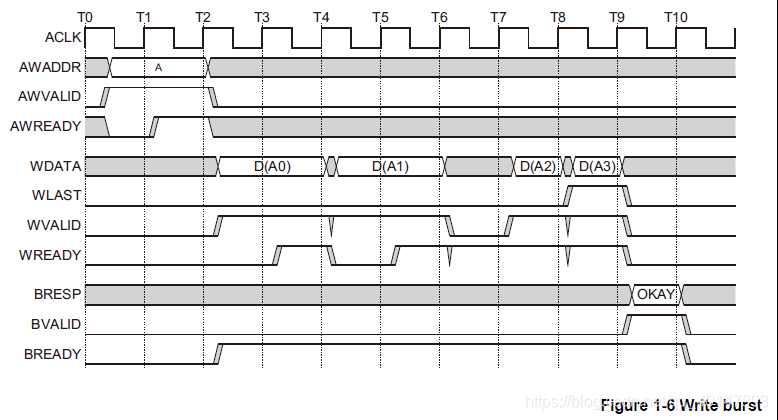

3.7 AXI-Lite读写时序

AXI-Lite读:

地址出现在地址总线上后,数据传输将在读取的数据通道上进行。从机将VALID信号保持为低电平,直到读取数据可用为止。对于最终数据传输突发时,从机将RLAST信号置位,表明正在传输最后一个数据项。

AXI-Lite重叠突发读取:

显示了从机接收到第一个突发地址后,主机如何驱动另一个突发地址使得从机能够与第二个突发并行的开始处理第二个突发数据,一次完成传输。

AXI-Lite写:

当主机发送地址和和控制信息至写地址通道,然后主机发送每个数据至写数据通道。当主机发送最后一个数据项时,WLAST信号变为高。当从机接收了所有数据项后,它将写响应返回至主机表示写操作完成。

4.AXI Uartlite实践

4.1 AXI Uartlite IP核配置

IP核的配置如下所示:

AXI时钟为100MHz

通信的波特率为115200。

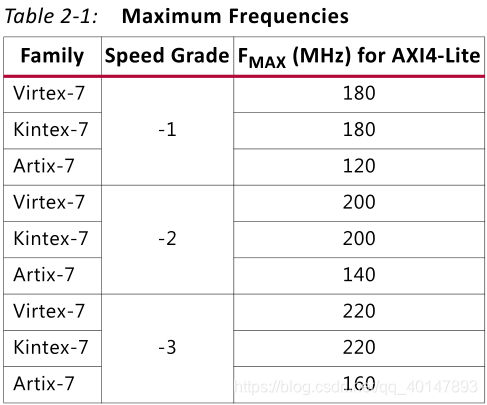

注意各系列的最大AXI时钟:

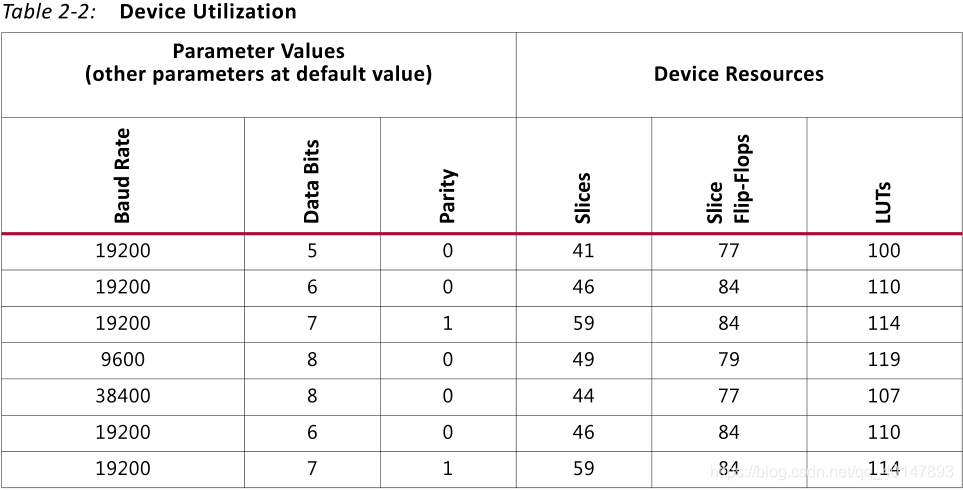

7系列AXI Uartlite IP在不同波特率下的的资源使用情况:

例化:

axi_uartlite_0 uart

(

.s_axi_aclk(s_axi_aclk), // input wire s_axi_aclk

.s_axi_aresetn(s_axi_aresetn), // input wire s_axi_aresetn

.interrupt(interrupt), // output wire interrupt

.s_axi_awaddr(s_axi_awaddr), // input wire [3 : 0] s_axi_awaddr

.s_axi_awvalid(s_axi_awvalid), // input wire s_axi_awvalid

.s_axi_awready(s_axi_awready), // output wire s_axi_awready

.s_axi_wdata(s_axi_wdata), // input wire [31 : 0] s_axi_wdata

.s_axi_wstrb(s_axi_wstrb), // input wire [3 : 0] s_axi_wstrb

.s_axi_wvalid(s_axi_wvalid), // input wire s_axi_wvalid

.s_axi_wready(s_axi_wready), // output wire s_axi_wready

.s_axi_bresp(s_axi_bresp), // output wire [1 : 0] s_axi_bresp

.s_axi_bvalid(s_axi_bvalid), // output wire s_axi_bvalid

.s_axi_bready(s_axi_bready), // input wire s_axi_bready

.s_axi_araddr(s_axi_araddr), // input wire [3 : 0] s_axi_araddr

.s_axi_arvalid(s_axi_arvalid), // input wire s_axi_arvalid

.s_axi_arready(s_axi_arready), // output wire s_axi_arready

.s_axi_rdata(s_axi_rdata), // output wire [31 : 0] s_axi_rdata

.s_axi_rresp(s_axi_rresp), // output wire [1 : 0] s_axi_rresp

.s_axi_rvalid(s_axi_rvalid), // output wire s_axi_rvalid

.s_axi_rready(s_axi_rready), // input wire s_axi_rready

.rx(rx), // input wire rx

.tx(tx) // output wire tx

);

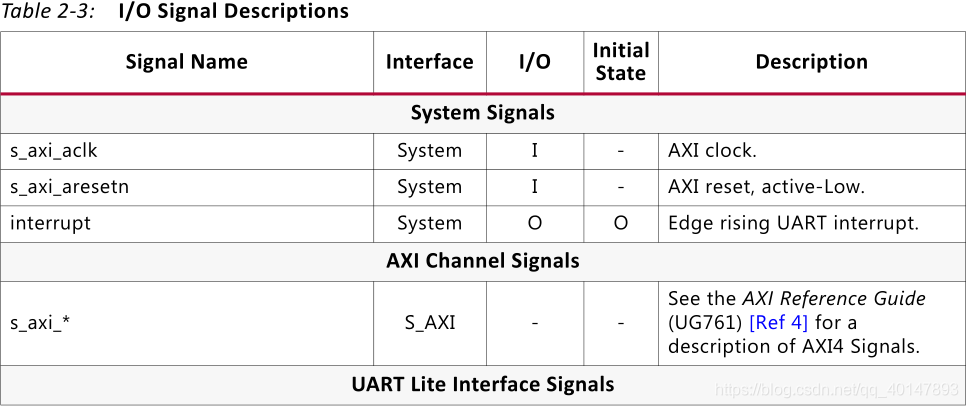

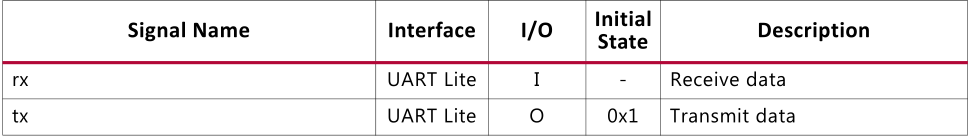

4.2 AXI Uartlite IP 端口介绍

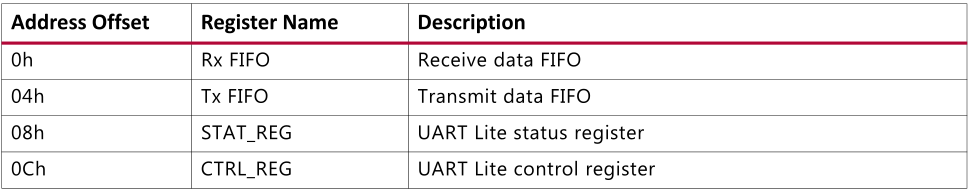

4.2 AXI Uartlite IP 寄存器地址映射

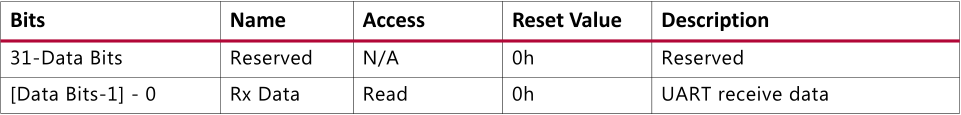

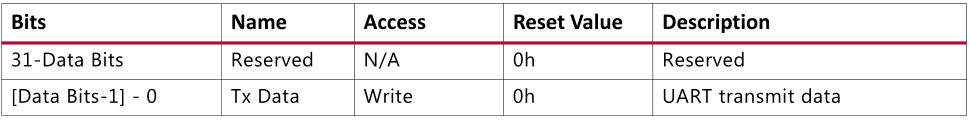

0h:RX FIFO

AXI Lite数据位为32bit,RX占s_axi_rdata[31:0]的低7bit即 RX_DATA=s_axi_rdata[7:0]。

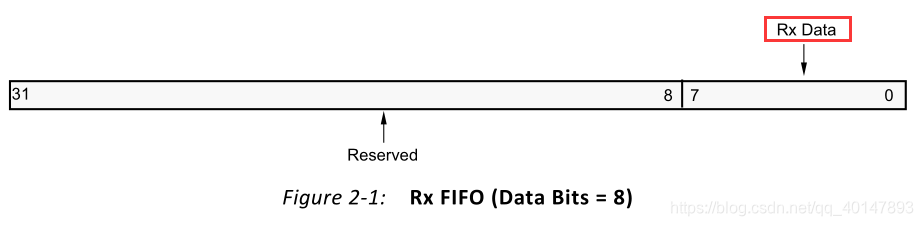

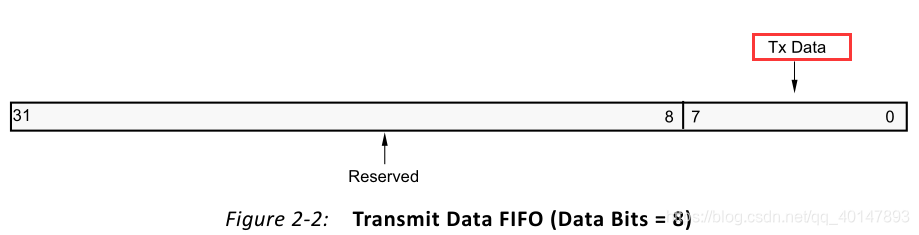

04h:TX FIFO

AXI Lite数据位为32bit,TX占s_axi_wdata[31:0]的低7bit即 TX_DATA=s_axi_wdata[7:0]。

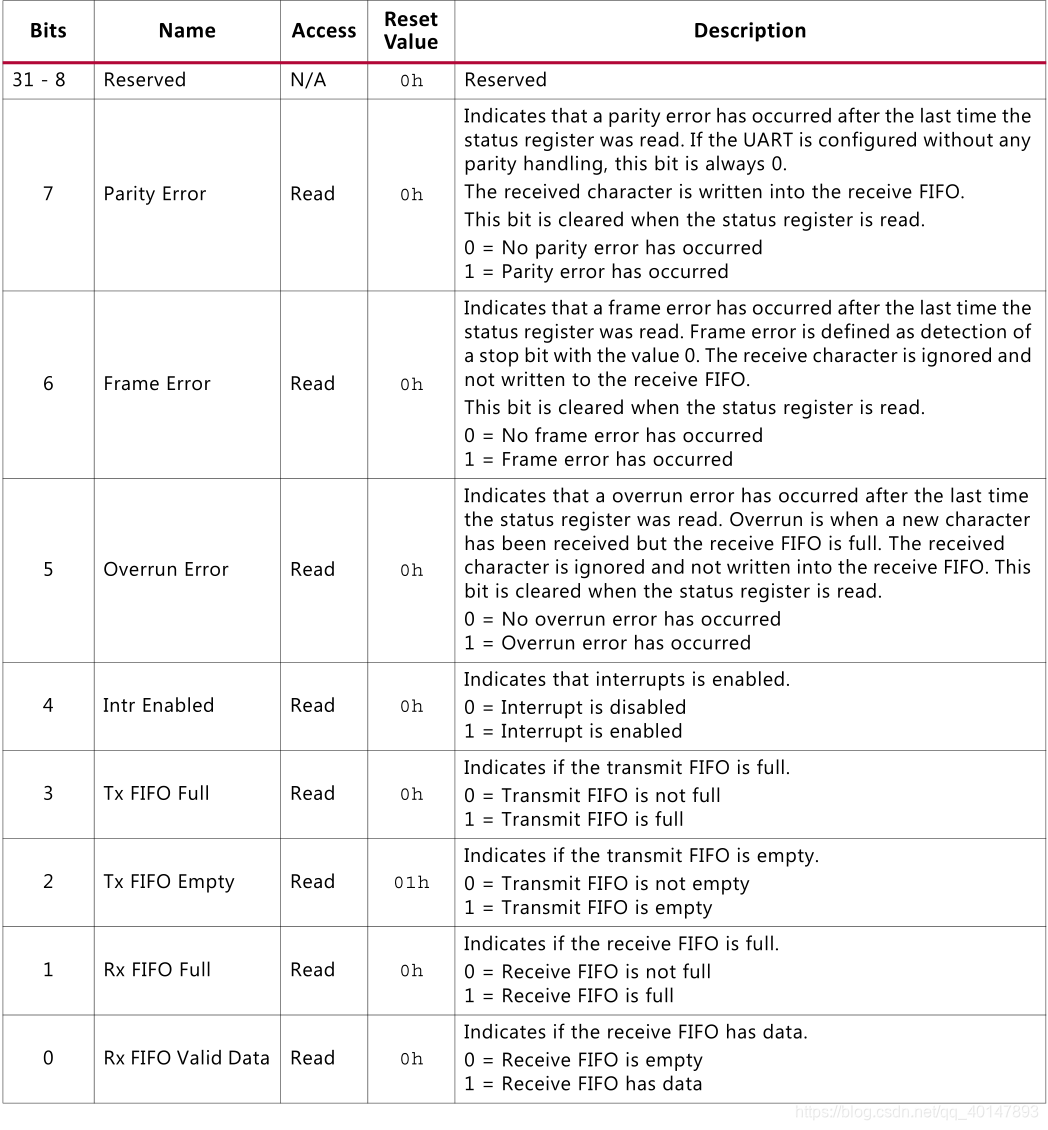

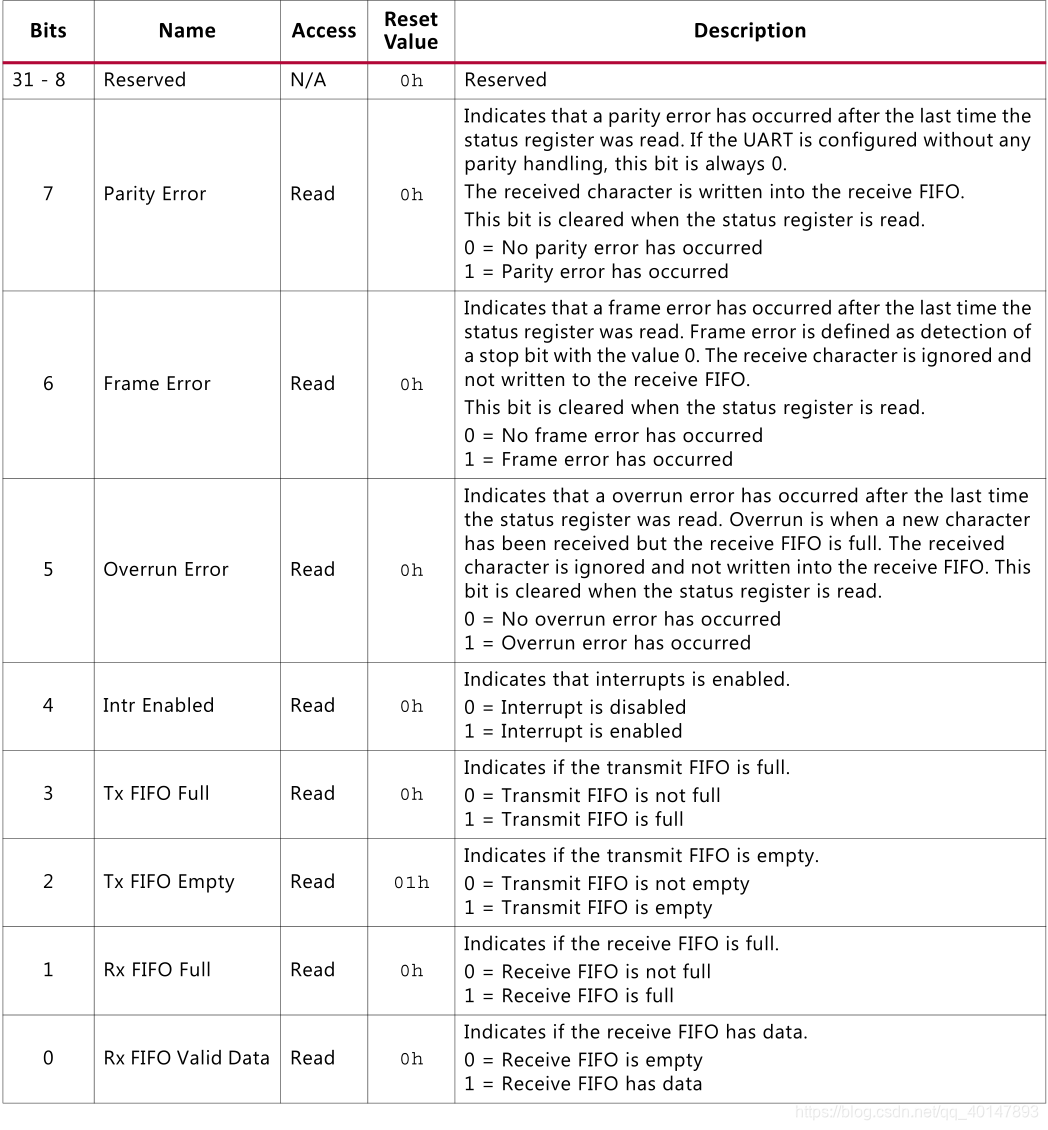

08h:STAT_REG

状态寄存器,包含接收核发送数据FIFO的状态。

D4:0中断为关闭状态,1中断为打开状态

D3:0发送数据FIFO非满,1发送数据FIFO为满

D2:0发送数据FIFO非空,1发送数据FIFO为空

D1:0接收数据FIFO非满,1接收数据FIFO为满

D0:0接收数据FIFO为空,1接收数据FIFO有数据

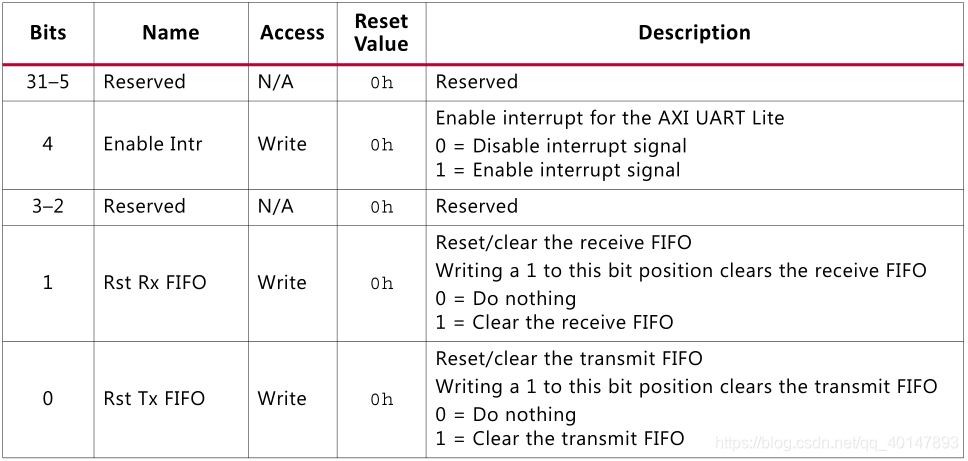

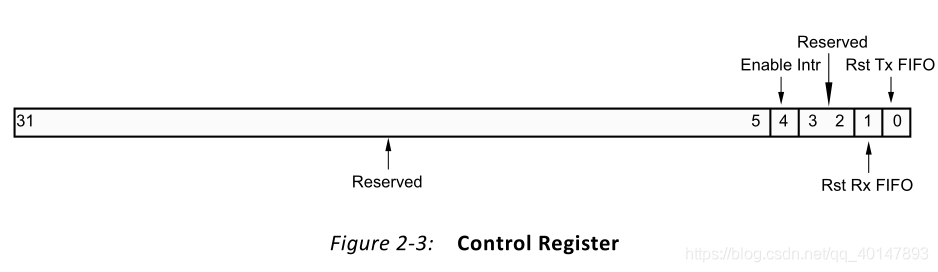

0Ch:CTRL_REG

D4:0关闭中断,1使能中断,(串口中断即接受或发送一帧数据 interrupt端口产生一个脉冲)

D1:1清除接受FIFO

D0:1清除发送FIFO

4.3 AXI Uartlite IP AXI协议配置

AXI Uartlite IP是用户通过AXI Lite协议进行数据的发送和接收的,在IP配置好波特率之后,发送数据即往地址04h的寄存器低8bit中写入数据,接收数据即读取地址00h的低8bit。

在串口通信之前首先对AXI Uartlite IP 进行配置。

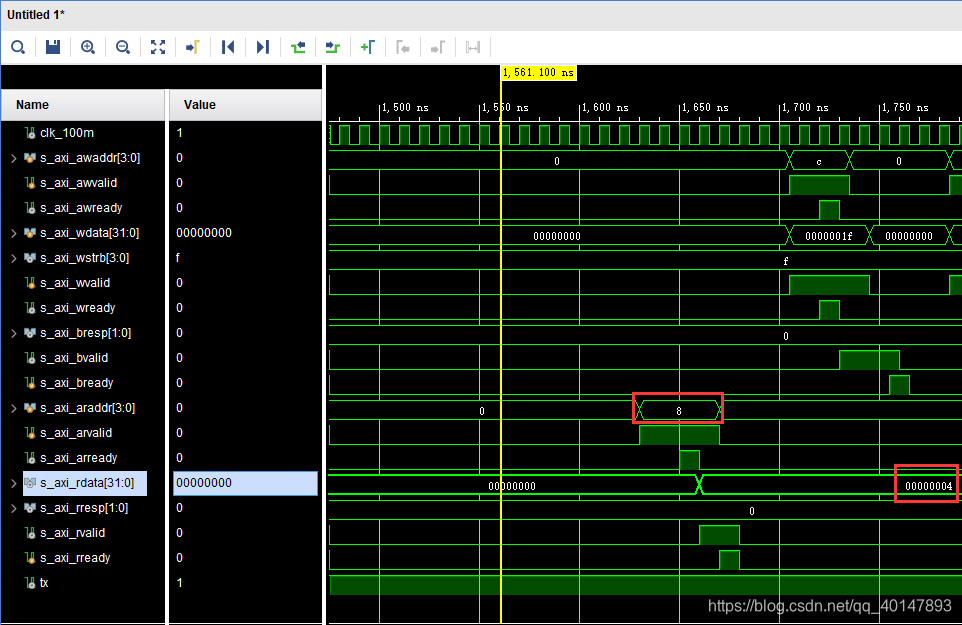

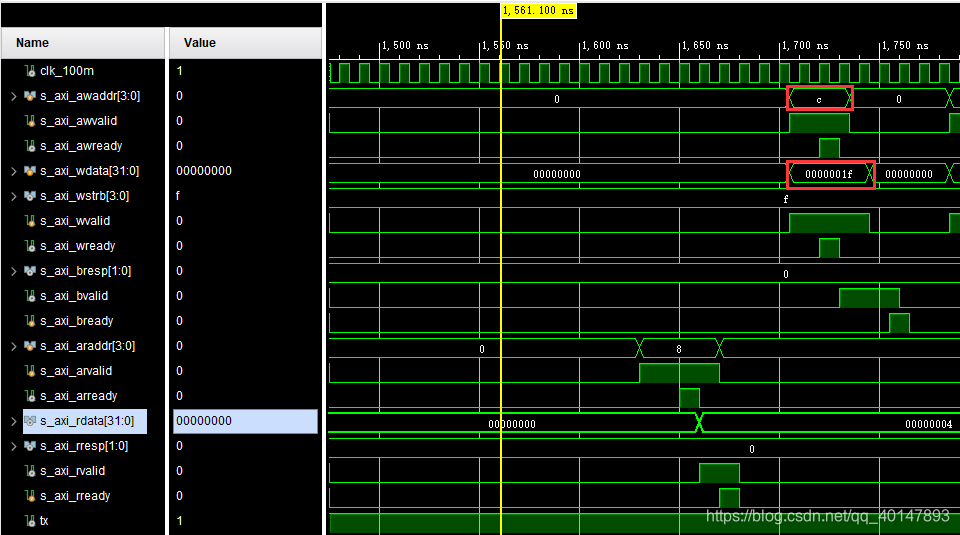

1、先读一下状态寄存器,验证一下AXI协议是否已通:(AXI读)

读取08h寄存器:

读取内容为32’h0000_0004,查看寄存器默认值确实为32’h0000_0004。

2、打开串口中断、清空发送接收FIFO,即向0Ch写入 32’h0000_001F:(AXI写)

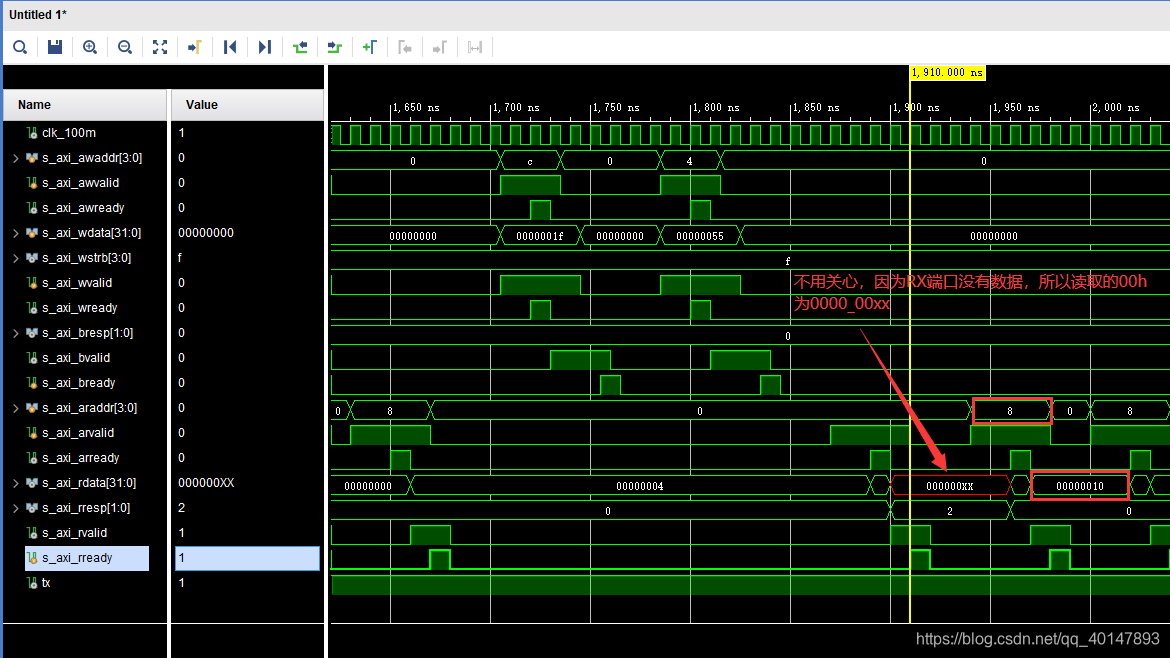

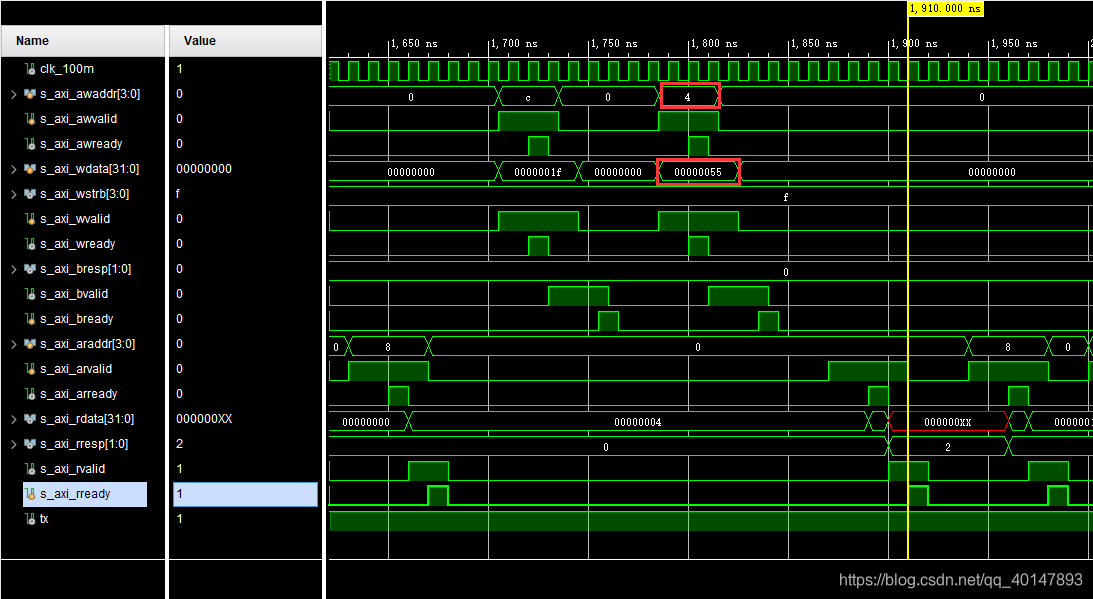

3、判断是否写入,继续读取08h寄存器:

对照08h寄存器表,发现中断已经打开,所以写入读取都正常。

4.3 AXI Uartlite IP 串口通信

发送:

向04h寄存器的低8bit写入将要发送的数据。

将要发送的数据0x55写入驱动代码接口:

assign cfg_mem[ 0] = {

4'h0C,32'h0000_001F };

assign cfg_mem[ 1] = {

4'h04,32'h0000_0055 };

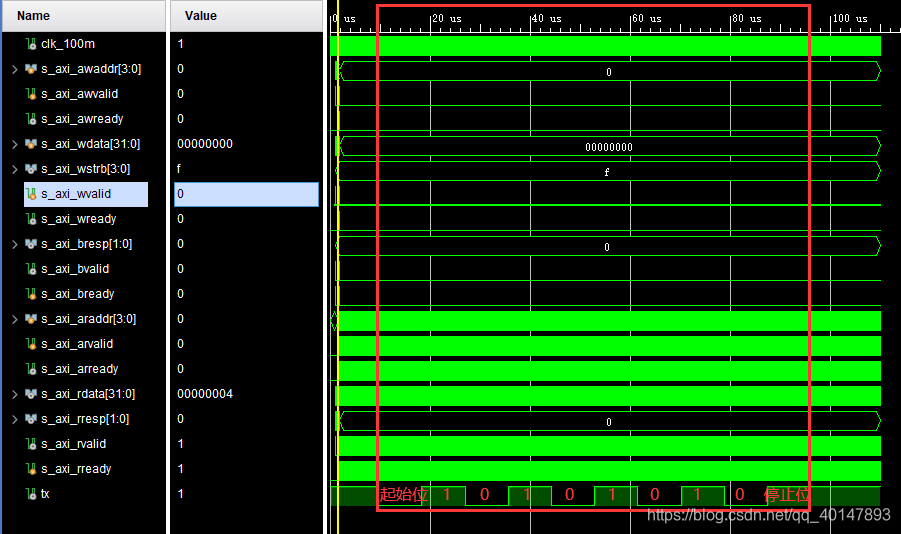

向写入04h写入数据后,将时间轴缩小观察TX波形:

我们可以注意时间轴,传输1bit需要 1/115200s=8.68us,串口传输了10bit即一帧数据为86.8us。吻合~

FPGA发送数据至:(只通过FPGA上电发了一次,综合一次时间太长了,不想改了,凑合看)

接收:

一直读取00h的低8bit数据:

AXI_RD1 :begin

AXI_CMD <= `AXI_R; //状态切换为读取

user_raddr <= 4'h00;

AXI_STATE <= (s_axi_rvalid ==1'b1)?AXI_RD1:AXI_RD1;

end

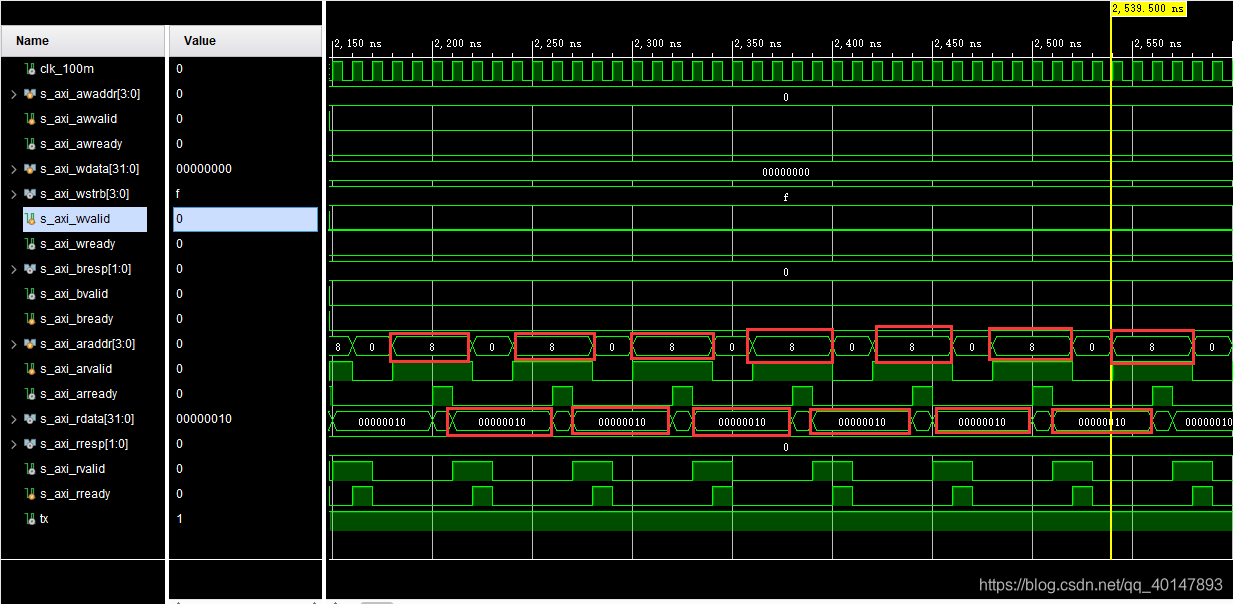

时序:

以下8h当做0h就可以!!!,因为不想改ila了…凑合看,上面一行为地址,下面一行为数据,重点是要看时序。

FPGA端ila设置触发后接收来自PC的数据:

5. AXI Uartlite IP AXI驱动代码

接口做好了,只需要给发送的数据就可以,或者直接提取数据就行。