qpsk调制解调

qpsk调制解调原理

-

qpsk调制主要有两种调制方式,一种是基于0,π/2,π,3π/2四种相位的调制,一种是基于π/4,3π/4,5π/4,7π/4的调制。我采用的是第二种调制方法。

-

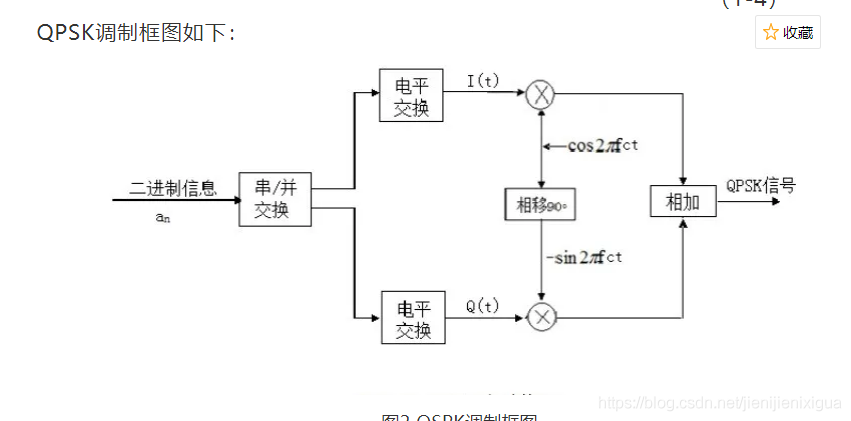

第二种方法我采用如下系统来实现。其实就是两路2psk调制后再相加。

-

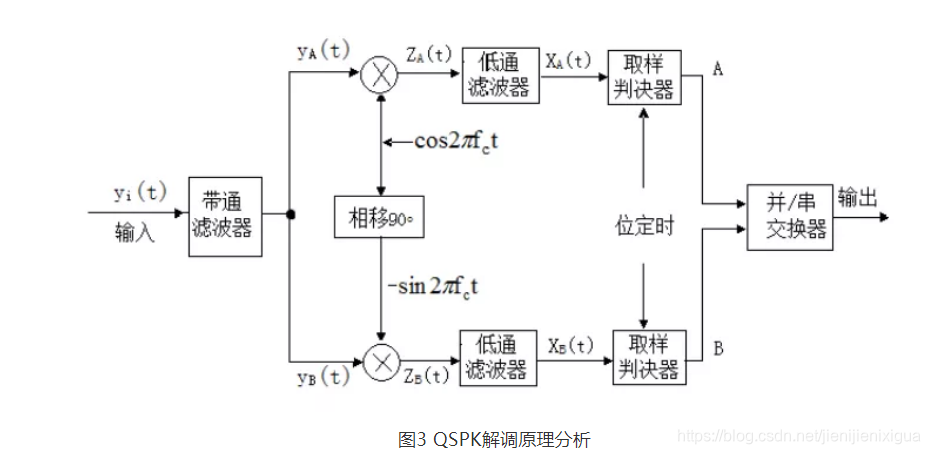

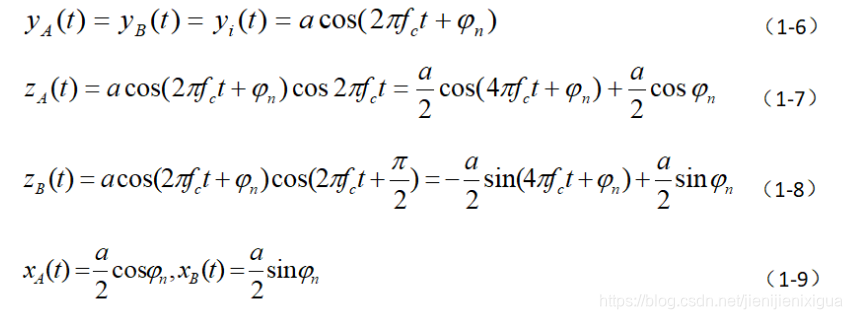

有关解调,在不考虑载波提取和位同步信号提取的前提下,只需要将qpsk信号经过相乘器和两个同相、正交两个正弦信号相乘再低通滤波,即可得出基带波形。最后再抽样判决,恢复出原本的数字基带信号。

-

我的代码主要由以下几个部分组成

- 2位二进制数字基带信号生成部分

- 同相、正交正弦波生成波表

- qpsk调制部分

- qpsk解调部分

-

数字序列生成器

always@(*) begin case(state) 3'd0: code <= 2'b00; 3'd1: code <= 2'b01; 3'd2: code <= 2'b10; 3'd3: code <= 2'b11; 3'd4: code <= 2'b11; 3'd5: code <= 2'b10; 3'd6: code <= 2'b01; 3'd7: code <= 2'b00; default code <= 2'b00; endcase end

生成如上二进制序列

00 代表 45°

01 代表 315°

10 代表 135°

11 代表 225° -

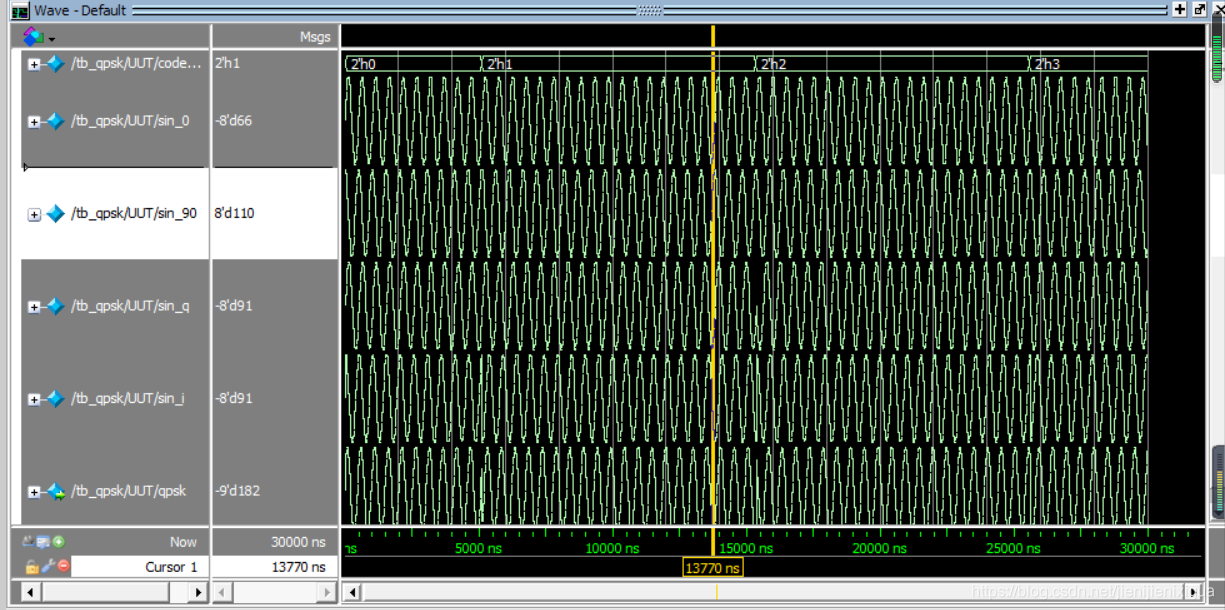

qpsk调制部分

-

先生成一个0相载波和一个90°初相位载波,这里我用二进制序列的高位控制0相载波,低位控制90°载波,可以当成是两个独立的2psk调制进行处理。然后再将这两个信号相加得到qpsk信号。将来解调的时候依然是按此规则,解调得到二进制序列的高低位。

-

always@(posedge clk) begin if(dq == 1) sin_q <= sin_0; else sin_q <= -sin_0; if(di == 1) sin_i <= sin_90; else sin_i <= -sin_90; end assign qpsk = sin_q + sin_i ;

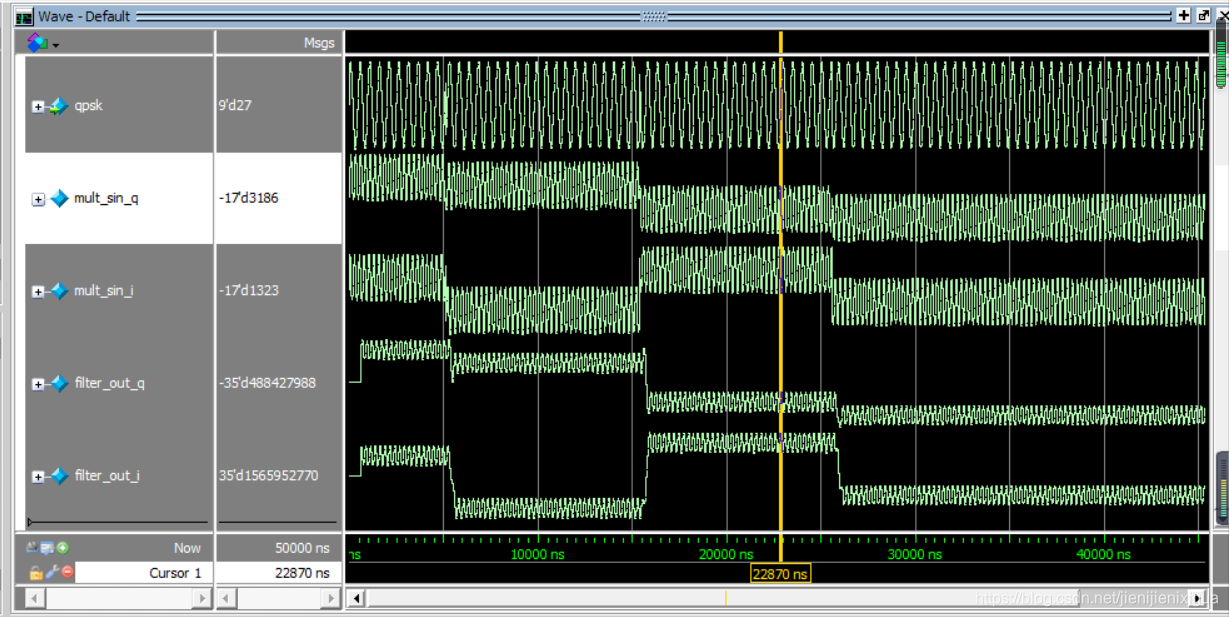

仿真结果如下

-

qpsk解调部分

如上面提到的,这里采用相干解调,暂时先直接用本地生成的0相载波和90°载波来解调(过几天学习如何使用克斯塔斯环来从已调信号中提取)。如调制的顺序,乘以0相载波的对应二进制序列高位,乘以90°载波的对应二进制序列低位。

reg signed [16:0]mult_sin_q; reg signed [16:0]mult_sin_i; always@(*) begin mult_sin_q <= qpsk * sin_0; mult_sin_i <= qpsk * sin_90; end

两路信号分别通过低通滤波器,滤除2倍载波分量(这里载波频率为2Mhz,基带信号的第一零点带宽为100khz),这里取滤波器截止频率为1Mhz,滤波器用matlab软件生成。

filter02 filter02_inst1( .clk(clk), .clk_enable(1), .reset(0), .filter_in(mult_sin_q[16:1]), .filter_out(filter_out_q) );

filter02 filter02_inst2( .clk(clk), .clk_enable(1), .reset(0), .filter_in(mult_sin_i[16:1]), .filter_out(filter_out_i) );

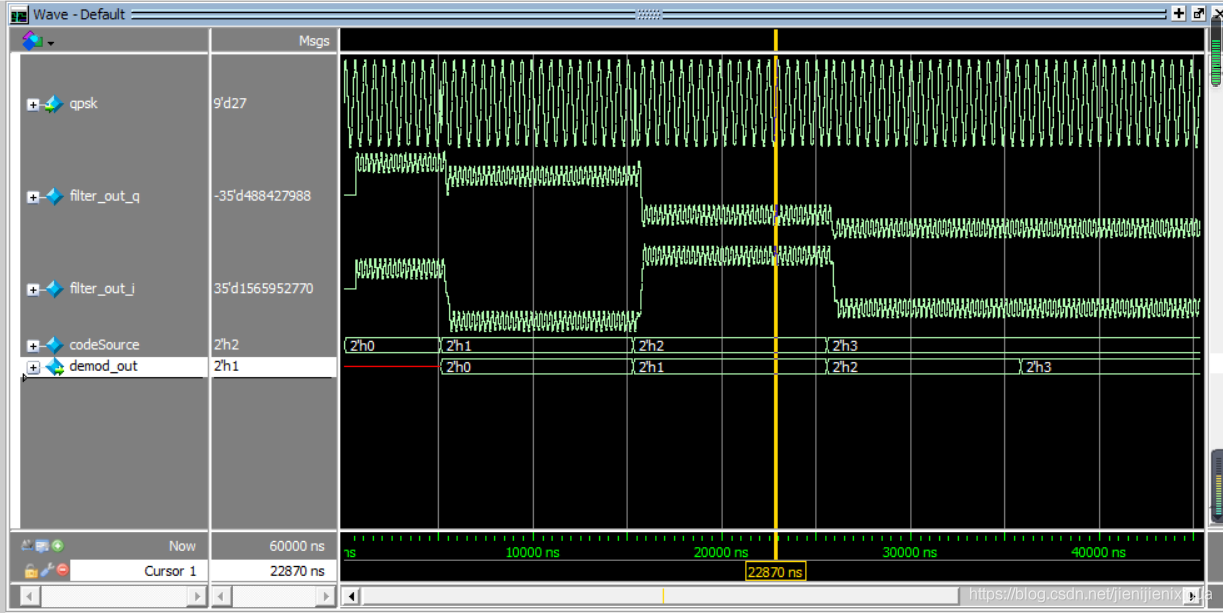

可见滤波后波形基本上关于0对称,因此可以以0为判决门限进行抽样判决。

最后抽样判决得到数字基带信号。

always@(posedge syc_clk) begin if(filter_out_q >= 0) demod_out[1] <= 0; else demod_out[1] <= 1; if(filter_out_i >= 0 ) demod_out[0] <= 0; else demod_out[0] <= 1; end

这里的syc_clk作为位同步信号,我直接用的是本地生成二进制基带信号时的控制时钟,没有进行位同步信号提取。

可见译码基本正确。注意到抽样判决输出的信号比原本的二进制码元滞后一个位同步时钟,根据分析,可能是因为滤波器的输入到输出需要多个系统时钟周期来处理,因此在输入码元跳变的时候它不会立马跳变,因此导致了判决时钟来了的时候滤波器输出的基带波形仍然保持上一个状态的值。导致滞后一个时钟。