本篇内容:

1.cpfsk调制方法。

2.如何调用NCO?

3.如何修改已经生成的NCO参数?

1.cpfsk调制方法:

调制思路如下,频率控制字的计算方法第2部分会有讲解。

具体的程序可以去我上传的资源中看,也可以去华信教育资源网找杜勇老师的书的参考代码。

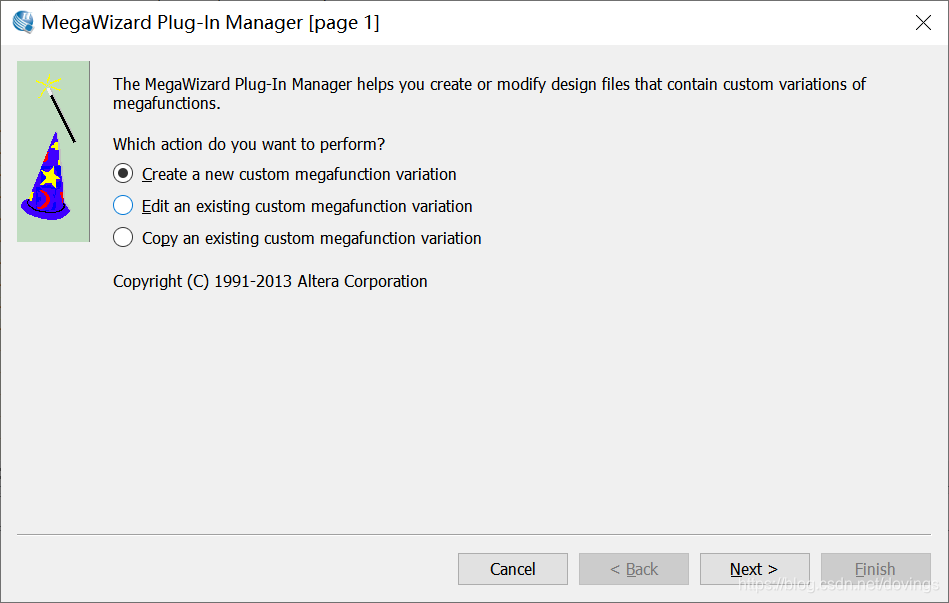

2.点击Tools-megawizard plug in manager ,选择create a new,点击next。

搜索NCO,选中NCO,选择语言,选择保存位置(默认工程文件夹下,应该也可以建立一个子文件夹)输入名字dds0(自己随便起),点击next,稍稍等一会。

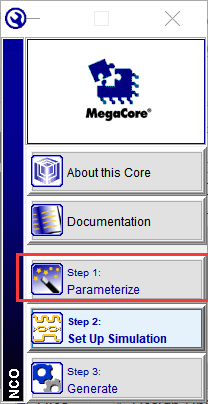

出来了,点击step1.

根据自己的需求设置,我的采样频率是160kHz,载波频率是10kHz,码元频率是1kHz,调制制度是2.5,输出选的10位(幅度最小只能十位),相位累加器精度16位。如果你的频率高就增加位宽,频率分辨率不能太大。

(4096划重点,一会要考!)

点中间的implementation,选中频率调制输入,精度设置为16位(和刚才相位累加器精度相同),选择单输出。

点右边的resource estimate看看资源消耗,估计逻辑单元用了304个,如果感觉多了,可以把前面的位宽什么的调小一点,我的逻辑单元只有6000多,得省着点用。好了点击finish吧。

点击step 2,选中generate simulation model(仿真用的,记得选中啊!),选择语言,点击OK。

点击step 3开始生成,这里有可能会卡住,在网上找了一堆方法都不好使。我的方法是,先打开任务管理器,再点击生成,不行就取消多生成几次。(这算什么方法??我也很迷惑)

在file栏找到dds0.v,双击打开。

把这一段粘贴到你的程序中。

左面dds0_st必须是你刚才起的IP核名字,右边的自己随便取。

phi_inc_i是刚才的4096,freq_mod_i是512/-512.另外一种方法是,phi_inc_i是0,freq_mod_i是4608/3584.

意思就是保证phi_inc_i与freq_mod_i之和是你想要输出的两个频率。

3.如何编辑已经生成的IP核?

点击IP Components,双击dds0.