一、技术指标

完成信号AM调制和解调功能,具体要求如下:

(1)载波信号频率范围:1M-10MHz,分辨率0.01MHz;

(2)调制信号为单频正弦波信号,频率范围:1kHz-10kHz,分辨率0.01kHz;

(3)调制深度0-1.0,步进0.1,精度优于5%;

(4)使用MATLAB对比调制信号和解调信号指标;

(5)载波信号频率、调制信号频率和调制深度可设置;

(6)完成仿真测试验证。

二、AM原理

原理很简单了,具体可以参考相关书目。

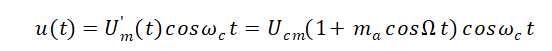

调制原理就是这个公式:

解调原理就是全波整流+低通滤波。

三、方案设计

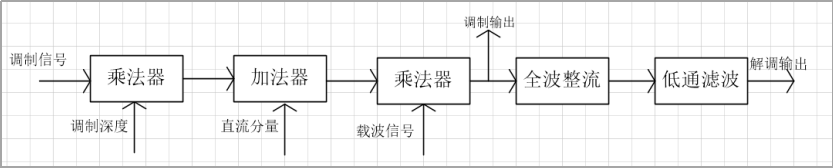

原理框图如下:

第一部分

第一部分为调制信号和载波信号的生成:根据分辨率计算出位宽,调用两次DDS IP核,分别产生调制信号和载波信号。

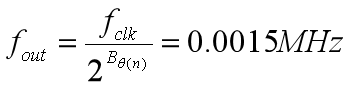

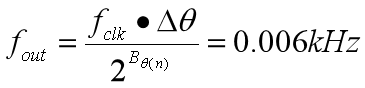

产生调制信号和载波信号需要调用dds核,根据公式

其中,fclk为系统时钟,▲θ为频率控制字,B为相位累加器位宽,fout为输出信号频率。

对于载波信号,当取B = 16时,频率分辨率为

对于调制信号,当取B = 24时,频率分辨率为

相位累加器的位宽大家可以根据频率分辨率指标要求和实际仿真结果确定,不一定非取这两个数。

第二部分

第二部分为调制部分:先乘以调制深度,再叠加直流分量,最后与载波相乘,这些都可以通过调用乘法器、加法器IP核实现。

设置DDS的输出位宽为8位,那么调制信号幅度大小-128到127(实际仿真为-126~126),需要叠加直流分量使调制信号幅度均为正值。假设直流分量A为127,就可以得到标准式

那么关于调制深度,由于不能直接显示小数,我们可以将ma*256取整,与调制信号相乘,再将结果右移8位即可。

第三部分

第三部分为解调部分:采用包络检波解调法,即先进行全波整流,将负值全部取反,再进行低通滤波滤波,最后截位即可得解调信号,这些可以通过编写程序、调用fir滤波器核实现。

在此之前,需要用matlab准备好滤波器系数文件。

在命令行窗口输入filterDesigner,回车。

滤波器选择fir低通滤波器,滤波器阶数设置为100(根据出图效果选的,不一定科学),采样频率为25MHz(只要>2*10MHz就可以),截止频率为25kHz(只要>10kHz就可以)。

点左下角第三个图标进行量化,点击菜单栏Targets,输出为.coe文件,在调用fir IP核时引用。