欢迎乐于分享的工程师加入我的电子设计开发交流QQ群:552564745

闲置引脚配置

在CPLD做辅助功能的系统里,CPLD中那些没有使用到的引脚一定要记得设置为一个固定状态,否则的话可能给主系统引入很大的不确定性。有时候由于设计初期的疏忽,后期调试时,为了排查某个问题可能会出现方向偏差,浪费很多调试时间。甚至有些情况下,CPLD引脚电平混乱会导致主系统启动失败,这时候调试起来更加费力。

所以对于CPLD新手,谨记配置好闲置引脚是一个极好的开发习惯。

下面以Aletera的Quartus II为例说明如何配置闲置引脚功能。

-

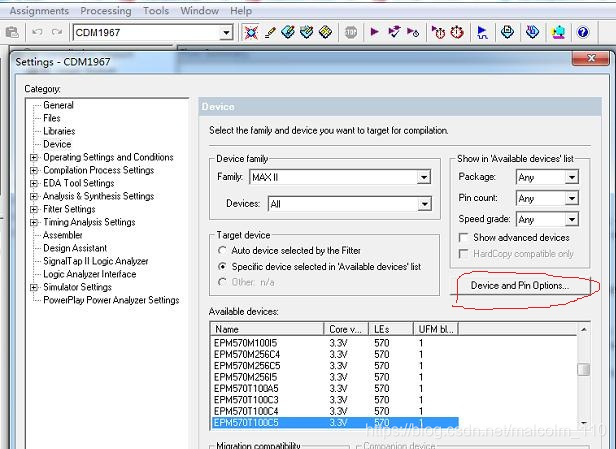

找到工具栏最上面一行的Assignments,选择Device…,然后点击

-

在弹出的对话框中点击Device and Pin Options…

-

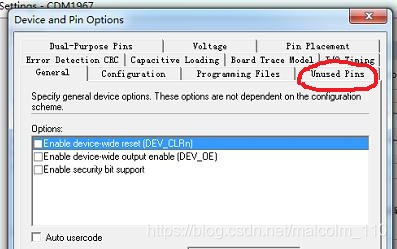

继续在弹出的对话中点击Unused Pins

-

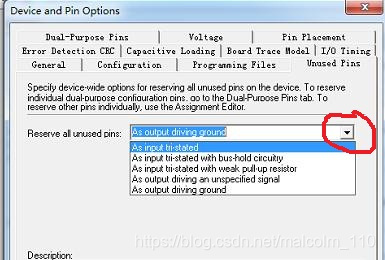

在弹出的对话框中点击下拉菜单。

此时可以看到没有用到的pin有五个备选设置,分别是输入三态、总线保持的三态输入、弱上拉的三态输入、三态输出以及接地输出。如果对三态、总线保持等概念不清楚的请查看我另外一篇博文。

一般情况下选择输入三态即可。

CPLD引脚的第二功能设置

我们在查看CPLD的引脚定义时,会发现有些引脚会有第二功能,比如全局复位、清除寄存器等。如何配置引脚的第二功能,在我刚开始学习电路设计的时候不知道怎么去弄,有时候跑到别人群里去问也没人回应,那时候就想自己一定要把这个问题弄清楚。经过多次的资料查找后,终于发现了设置方法,现在看看居然是这么一个简单的问题,当初居然都不知道!好了,废话少说,上图。

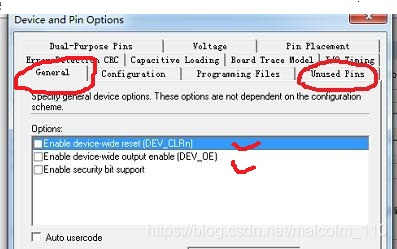

前两步操作请参考闲置引脚配置的前两步,在第三幅图中,有一个General基本设置项,下面可以看到客供选择的第二功能设置,需要使用的时候,在前面打勾即可。