1.应用背景

PC/104总线嵌入式工控机是专门为工控领域设计的具有特定尺寸和接口的计算机。

但是在特定的工控中,对处理器的功耗有严格要求。基于X86架构的PC104工控机发热过大容易造成系统的不稳定。ARM架构的处理器具有低功耗高处理的能力,很好弥补了上述不足。但ARM中不支持PC104总线。因此,可以采用ARM+CPLD的结构,通过CPLD来构造PC104部分的时序。附件中论文有对ARM和X86处理器的介绍和比较。

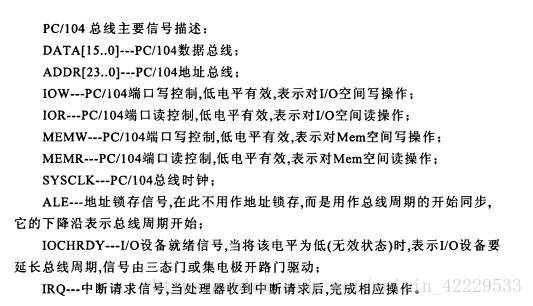

图1:PC104主要信号的描述

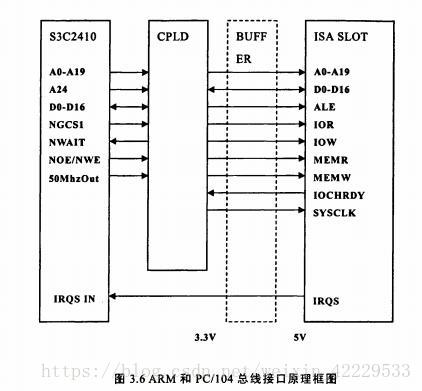

ARM+CPLD的结构来支持PC104总线,CPLD的作用是把本地总线转化为PC104的总线,这也是整个系统的难点。此外,ARM在电平模式制造工艺上和PC104存在差异,所以他们之间还要其他的物理手段处理。值得一提的是,该方案是不支持DMA传输的。具体的系统结构如下图:

图2:系统结构

图3:网上的一个接口实例

2.设计分析:

CPLD需要做的工作,其实有以下三点:

-

PC104设备端BALE,SA/LA<23:17>,SD,数据和ARM端nGCS,ADDR,DATA的时序转换

-

PC104设备端SMEMW/R MEMW/R,IOW/R和ARM端OE,WE时序的转换

-

PC104设备端IOCHDY和ARM端的nWAIT时序的转换

(注意:MEMCS16、IOCS16、SBHE这类判断是16位还是8位的信号线其实也是需要控制的。但是在本案例中MEMCS16、IOCS16在原理图中是给的固定值,所以在此处省略。)

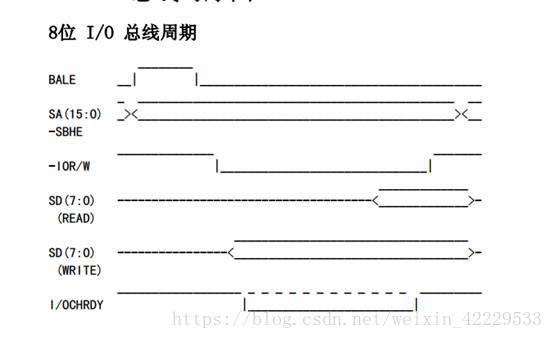

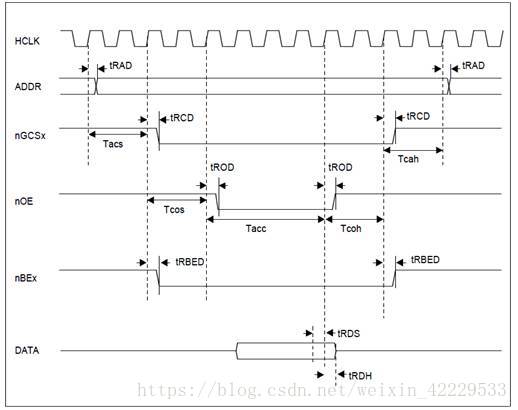

PC104设备端(PC104总线)和 ARM端(ARM读写总线)的时序图如下:

图4. PC104端的IO模式读写时序(8位)

图5. ARM的读写时序

对照标准的PC104协议,读写模式有多种。本案例中,只是基于最简单的IO和内存读写模式, 许多信号暂时用不到。具体如下:

DACK3,DRQ3,DACK1,DRQ1,REFRESH,DACK2,TC,OSC,IOCHCK,MEMCS16,IOCS16,DACK0,DRQ0,DACK5,DRQ5,DACK6,DRQ6,DACK7,DRQ7,MASTER

需要CPLD来协调的PC104设备端信号主要为以下几点:

地址:A0~A19,L17~L23

数据:D0~D7,D8~D15

延迟:IOCHRDY

地址允许锁存:BALE

中断:IRQ

时钟:SYSCLK

IO读写:IOW/R

内存读写:SMEMW/R MEMW/R

复位:RSTDRY

总线高字节允许信号:SBHE (该信号有效时表示数据总线上传送的是高位字节数据,在本例中由于MEMCS16等信号都是在原理图中给的定值,因此SBHE在CPLD里也是给定值)

地址允许信号:AEN(地址允许信号, 输出线, 高电平有效。AEN=1,表明处于 DMA

控制周期; AEN=0,表示非 DMA 周期。此信号用来在 DMA 期间禁止 I/O 端

口的地址译码,本例中直接置0)。

需要CPLD来协调和ARM端信号主要为以下几点:

时钟:HCLK

地址:ADDR

选通:nGCS

读写使能:nOE/WE

数据:DATA

等待:nWait

3.设计实现

CPLD的操作总体思路:

-

检测ARM的nGCS 和复位信号。若复位以及未选通,则所有信号初始状态。 BALE<=0;nWAIT<=1;

-

在非复位以及选通状态(nGCS拉低,从ARM角度讲已经开始读写操作,正常时序里,此刻的地址位已经准备好),将输出给ARM的nWAIT信号置低,让ARM处理器开始处于延迟状态。

-

BALE信号拉高,等待一个周期然后跳入下一个状态

-

BALE信号拉低,与3状态配合实现下降沿,将地址锁存(此步骤是将ARM的地址总线转变为PC104的总线时序)

-

检测PC104设备端返回的IOCHRDY信号。如果拉高,代表PC设备端已经完成读写时序。在此处设置一个定时器,若高电平保持的时间满足了我们的设定值,则将nWAIT信号置高,ARM则不需要维持在延迟的状态。

-

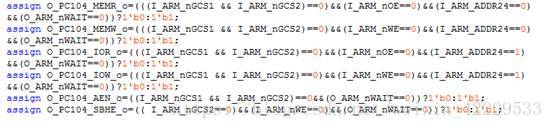

这一步骤不在PROCESS中,单独实时变化。PC104端的MEMR/W,和IOW/R,SBHE,AEN信号是主要是由ARM的nOE(读),nWE(写),ADDR24(IO访问或者内存访问)决定的。具体逻辑关系为:

7. 产生一个ARM和PC104时钟转换模块,将两者时钟匹配

备注:第6步也放在process中应该也可以,具体没研究。

4.附件

一篇有关如何实现PC104总线的论文:https://download.csdn.net/download/weixin_42229533/10647144