FPGA与CPLD最大的差别在于实现逻辑功能的原理不同,FPGA逻辑快是基于LUT为基础的,而CPLD中的逻辑快是以与-或阵列为基础的。

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

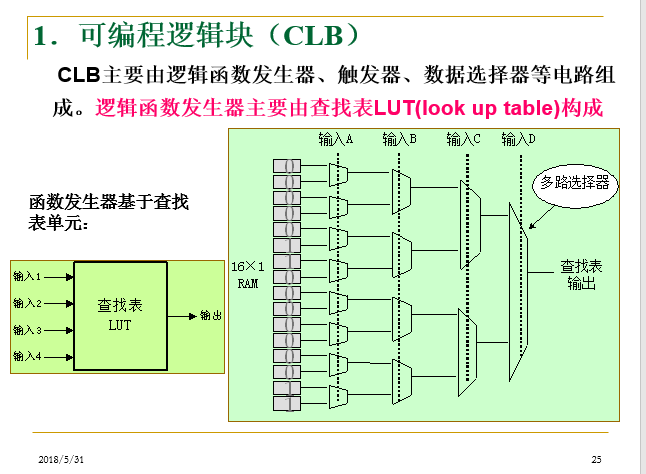

FPGA由可编程逻辑块(CLB)、输入/输出模块(IOB)及可编程互连资源(PIR)等三种可编程电路和一个SRAM结构的配置存储单元组成。CLB是实现逻辑功能的基本单元,它们通常规则地排列成一个阵列,散布于整个芯片中;可编程输入/输出模块(IOB)主要完成芯片上的逻辑与外部引脚的接口,它通常排列在芯片的四周;可编程互连资源(IR)包括各种长度的连线线段和一些可编程连接开关,它们将各个CLB之间或CLB与IOB之间以及IOB之间连接起来,构成特定功能的电路。

由于FPGA需要被反复烧写,它实现组合逻辑的基本结构不能像ASIC那样通过固定的与非门来实现,而只能易于反复配置的结构,查找表可以很好的满足这一要求。目前主流FPGA都采用基于SRAM工艺的查找表结构。通过烧写文件去配置查找表的内容,从而实现在相同电路的情况下实现了不同的逻辑功能,即对FPGA的重复配置。

查找表(Look-Up-Table)简称为LUT,LUT本质上就是一个RAM。目前主流的FPGA中多使用4或6输入的LUT,所以每一个LUT可以看成一个有4(或6)位地址线的16-1(或64-1)的RAM。当用户通过原理图或HDL语言描述了一个逻辑电路以后,PLD/FPGA开发软件会自动计算逻辑电路的所有可能结果,并把真值表(即结果)事先写入RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出对应地址的内容,然后输出即可。LUT具有和逻辑电路相同的功能,实际上,LUT具有更快的执行速度和更大的规模。

目前,FPGA市场占有率最高的两大公司Xilinx和Altera生产的FPGA都是基于SRAM工艺的,需要在使用时外接一个片存储器以保存程序。上电时,FPGA将外部存储器中的数据读入片内RAM,完成配置后进入工作状态;掉电后恢复为白片,内部逻辑消失。

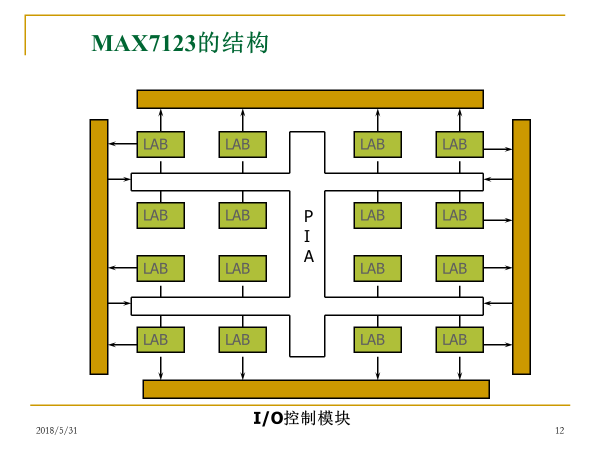

CPLD(ComplexProgrammable Logic Device),复杂可编程逻辑器件。CPLD内部由I/O快,逻辑块(LAB)和内部可编程连线区(PIA)三部分构成。

(1) 可编程逻辑阵列(LAB)

可编程逻辑阵列又若干个可编程逻辑宏单元(Logic Macro Cell,LMC)组成, LMC内部主要包括与阵列、或阵列、可编程触发器和多路选择器等电路,能独立地配置为时序或组合工作方式。

Figure1宏单元结构图

(2)可编程内部连线(PIA)

可编程内部连线的作用是在各逻辑宏单元之间以及逻辑宏单元和I/O单元之间提供互连网络。各逻辑宏单元通过可编程连线阵列接收来自输入端的信号,并将宏单元的信号送目的地。这种互连机制有很大的灵活性,它允许在不影响引脚分配的情况下改变内部的设计。

(3)可编程I/O单元(IOC)

CPLD的I/O单元(Input/OutputCell,IOC),是内部信号到I/O引脚的接口部分。根据器件和功能的不同,各种器件的结构也不相同。由于阵列型器件通常只有少数几个专用输入端,大部分端口均为I/O端,而且系统的输入信号通常需要锁存。因此I/O常作为一个独立单元来处理。