说明

参考资料: 《ispMACH 4000ZE Family》

《Advanced Features of the ispMACH 4000ZE Family》

《Power Estimation in ispMACH 4000ZE Devices》

软件工具: isplever classic 2.1

内部晶振最大输出5MHz时钟;isplever classic 2.1未给出power报告,而是官方提供了评估设计功耗的计算公式;本文档通过一个分频器的例子介绍了在设计中使用内部晶振的方法,并结合生成的设计报告计算设计的功耗;本设计实现将内部晶振时钟分频输出,有一个复位输入信号和一个分频输出信号。

内部晶振的使用

结构图(TIMER_DIV为分频参数,其余为端口)

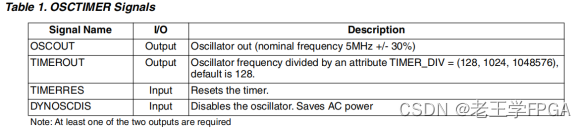

端口描述

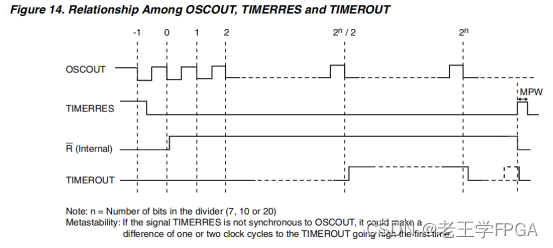

结合此图,推断TIMERRES为高电平时将定时器复位,低电平时定时器工作;结合官方代码资源推断DYNOSCDIS为高时整个晶振禁用,低电平时晶振启动。

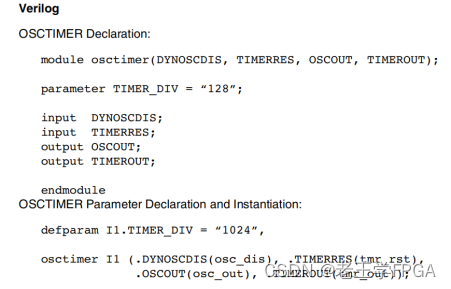

原语

在自己的代码中例化

这里复位了定时器,启用了晶振的5MHz时钟,clk_osw 为5MHz

映射后的报告

功耗计算

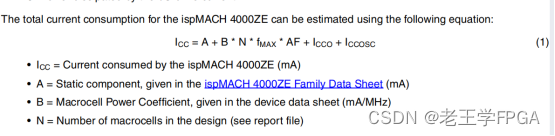

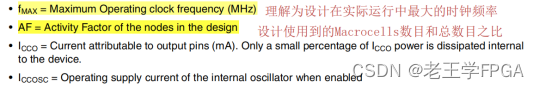

功耗计算利用手册给出的公式计算评估

这样,结合本设计可以给出相关参数:

A:器件固定参数,0.010 (mA)

B:器件固定参数,0.009 (mA/MHz)

N:器件固定参数,32 Macrocells

Fmax:这里只用到了5Mhz的晶振时钟

AF:0.125 (设计占用了4个macrocells,器件总共32个,4/32)

Iccosc:15uA

Fn:输出管脚的频率,这里为1.25MHz

Cn:取0.020

Voh-Vol:查数据手册,取1.6V-0.2V=1.4V

m:这里只有一个输出引脚,取1

结合参数和公式,计算可得

ICC =0.010mA+(0.009*32*5*0.125)mA+(0.020*1.4*1.25)mA+0.015mA

=0.010mA+0.18mA+0.035mA+0.015mA

=0.24mA=240uA