00. 目录

文章目录

01. 协处理器指令概述

ARM 体系结构允许通过增加协处理器来扩展指令集。最常用的协处理器是用于控制片上功能的系统协处理器。例如,控制 Cache 和存储管理单元的 cp15 寄存器。此外,还有用于浮点运算的浮点 ARM 协处理器,各生产商还可以根据需要开发自己的专用协处理器。ARM 协处理器具有自己专用的寄存器组,它们的状态由控制 ARM 状态的指令的镜像指令来控制。程序的控制流指令由 ARM 处理器来处理,所有协处理器指令只能同数据处理和数据传送有关。按照 RISC 的 Load/Store 体系原则,数据的处理和传送指令是被清楚分开的,所以它们有不同的指令格式。ARM 处理器支持 16 个协处理器,在程序执行过程中,每个协处理器忽略 ARM 和其他协处理器指令。当一个协处理器硬件不能执行属于它的协处理器指令时,将产生一个未定义指令异常中断,在该异常中断处理过程中,可以通过软件仿真该硬件操作。如果一个系统中不包含向量浮点运算器,则可以选择浮点运算软件包来支持向量浮点运算。

ARM 协处理器可以部分地执行一条指令,然后产生中断。如除法运算除数为 0 和溢出,这样可以更好地处理运行时产生(run-time-generated)的异常。但是,指令的部分执行是由协处理器完成的,此过程对 ARM 来说是透明的。当 ARM 处理器重新获得执行时,它将从产生异常的指令处开始执行。对某一个协处理器来说,并不一定用到协处理器指令中的所有的域。具体协处理器如何定义和操作完全由协处理器的制造商自己决定,因此,ARM协处理器指令中的协处理器寄存器的标识符及操作助记符也有各种不同的实现定义。程序员可以通过宏定义这些指令的语法格式。

ARM 协处理器指令可分为以下 3 类。

(1)协处理器数据操作。协处理器数据操作完全是协处理器内部操作,它完成协处理器寄存器的状态改变。如浮点加运算,在浮点协处理器中两个寄存器相加,结果放在第 3个寄存器中。这类指令包括 CDP 指令。

(2)协处理器数据传送指令。这类指令从寄存器读取数据装入协处理器寄存器,或将协处理器寄存器的数据装入存储器。因为协处理器可以支持自己的数据类型,所以每个寄存器传送的字数与协处理器有关。ARM 处理器产生存储器地址,但传送的字节由协处理器控制。这类指令包括 LDC 指令和 STC 指令。

(3)协处理器寄存器传送指令。在某些情况下,需要 ARM 处理器和协处理器之间传送数据。如一个浮点运算协处理器,FIX 指令从协处理器寄存器取得浮点数据,将它转换为整数,并将整数传送到 ARM 寄存器中。经常需要用浮点比较产生的结果来影响控制流,因此,比较结果必须传送到 ARM 的 CPSR 中。这类协处理器寄存器传送指令包括 MCR 和MRC。

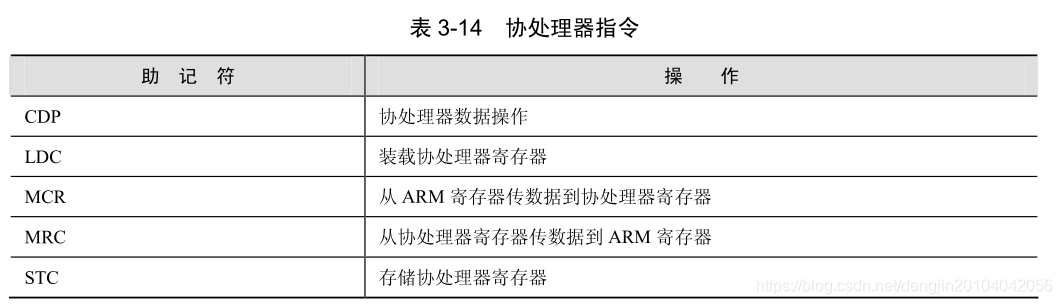

如下表所示列出了所有协处理器处理指令。

02. ARM寄存器到协处理器寄存器的数据传送指令MCR

2.1 指令编码格式

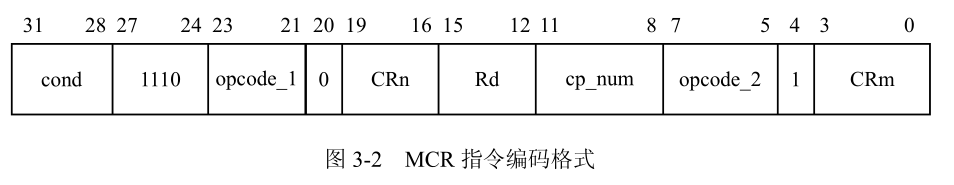

ARM 寄存器到协处理器寄存器的数据传送指令 MCR(Move to Coprocessor from ARMRegister)将 ARM 寄存器 的值传送到协处理器寄存器 cp_num 中。如果没有协处理器执行指定操作,将产生未定义指令异常。指令的编码格式如图 3-2 所示。

2.2 指令的语法格式

MCR{<cond>} <coproc>,<opcode_1>,<Rd>,<CRn>,<CRm> {<opcode_2>}

① <cond>

为指令编码中的条件域。它指示指令在什么条件下执行。当忽略时,指令为无条件执行(cond=AL(Alway ))。

② <coproc>

指定协处理器的编号,标准的协处理器的名字为 p0、p1、…、p15。

③ <opcode_1>

指定协处理器执行的操作码,确定哪一个协处理器指令将被执行。

④ <Rd>

确定哪一个 ARM 寄存器的数值将被传送。如果程序计数器(PC)的值被传送,指令的执行结果不可预知。

⑤ <CRn>

确定包含第一个操作数的协处理器寄存器。

⑥ <CRm>

确定包含第二个操作数的协处理器寄存器。

⑦ <opcode_2>

指定协处理器执行的操作码,确定哪一个协处理器指令将被执行。通常与<opcode_1>配合使用。

2.3 指令举例

将ARM寄存器r7中的值传送到协处理器p14的寄存器c7中,第一操作数opcode_1=1,第二操作数 opcode_2=6。

MCR p14,1,r7,c7,c12,6

2.4 指令的使用

指令的编码格式中,bits[31∶24]、bit[20]、bits[15∶8]和 bit[4]为 ARM 体系结构定义。其他域由各生产商定义。硬件协处理器支持与否完全由生产商定义,某款 ARM 芯片中,是否支持协处理器或支持哪个协处理器与 ARM 版本无关。生产商可以选择实现部分协处理器指令或者完全不支持协处理器。

03. 协处理器寄存器到ARM寄存器的数据传送指令MRC

3.1 指令编码格式

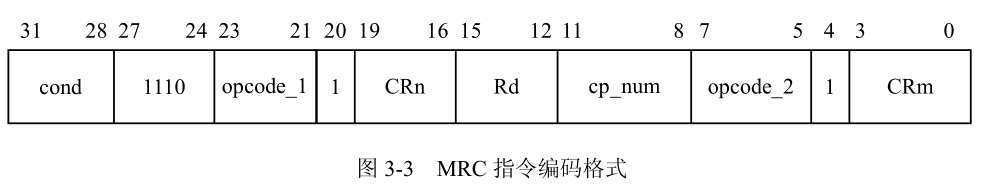

协处理器寄存器到 ARM 寄存器的数据传送指令 MRC(Move to ARM register fromCoprocessor)将协处理器 cp_num 的寄存器的值传送到 ARM 寄存器中。如果没有协处理器执行指定操作,将产生未定义指令异常。指令的编码格式如下图所示。

3.2 指令的语法格式

MRC{<cond>} <coproc>,<opcode_1>,<Rd>,<CRn>,<CRm>{,<opcode_2>}

为指令编码中的条件域。它指示指令在什么条件下执行。当忽略时,指令为无条件执行(cond=AL(Alway ))。

① <coproc>

指定协处理器的编号,标准的协处理器的名字为 p0、p1、…、p15。

② <opcode_1>

指定协处理器执行的操作码,确定哪一个协处理器指令将被执行。

③<Rd>

确定哪一个 ARM 寄存器接受协处理器传送的数值。如果程序计数器 PC 被用作目的寄存器,指令的执行结果不可预知。

④ <CRn>

确定包含第一个操作数的协处理器寄存器。

⑤ <CRm>

确定包含第二个操作数的协处理器寄存器。

⑥ <opcode_2>

指定协处理器执行的操作码,确定哪一个协处理器指令将被执行。通常与<opcode_1>配合使用。

3.3 指令举例

协处理器源寄存器为 c0 和 c2,目的寄存器为 ARM 寄存器 r4,第一操作数 opcode_1=5,第二操作数 opcode_2=3。

MRC p15,5,r4,c0,c2,3

3.4 指令的使用

如果目的寄存器为程序计数器 r15,则程序状态字条件标准位根据传送数据的前 4bit确定,后 28bit 被忽略。指令的编码格式中,bits[31:24]、bit[20]、bits[15:8]和 bit[4]为 ARM体系结构定义。其他域由各生产商定义。

硬件协处理器支持与否完全由生产商定义,某款 ARM 芯片中,是否支持协处理器或支持哪个协处理器与 ARM 版本无关。生产商可以选择实现部分协处理器指令或者完全不支持协处理器。

如果协处理器必须完成一些内部工作来准备一个 32 位数据向 ARM 传送(例如,浮点FIX 操作必须将浮点值转换为等效的定点值),那么这些工作必须在协处理器提交传送前进行。因此,在准备数据时经常需要协处理器握手信号处于“忙-等待”状态。ARM 可以在忙-等待时间内产生中断。如果它确实得以中断,那么它将暂停握手以服务中断。当它从中断服务程序返回时,将可能重试协处理器指令,但也可能不重试。例如,中断可能导致任务切换,无论哪种情况,协处理器必须给出一致结果,因此,在握手提交阶段之前的准备工作不允许改变处理器的可见状态。

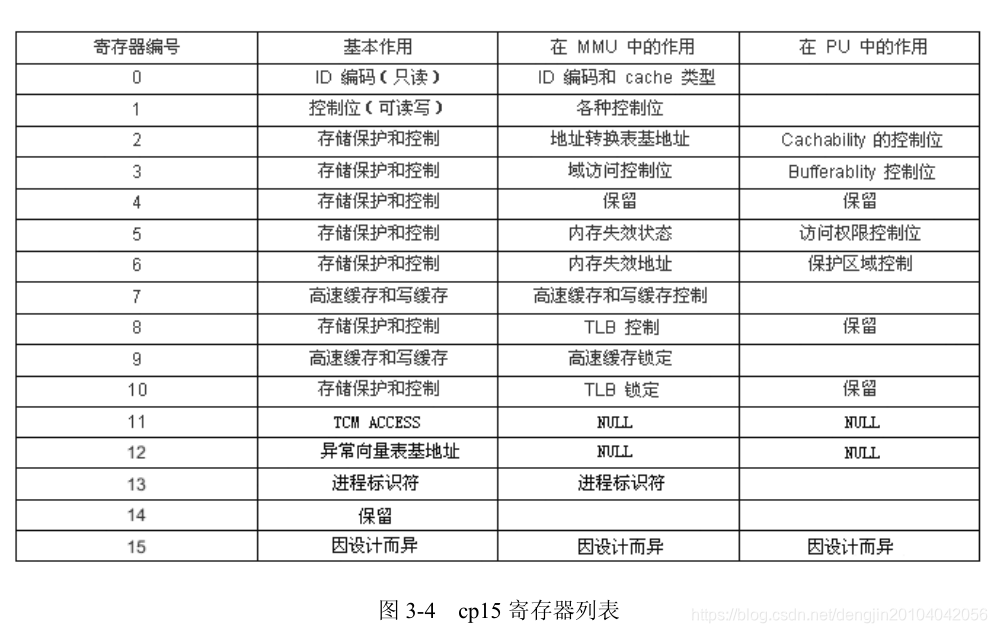

下图所示列出了 cp15 的各个寄存器的目的。

04. 附录

11.1 ARM Architecture Reference Manual