https://blog.csdn.net/silent123go/article/details/53169783

什么是协处理器

协处理器是一种芯片,用于减轻系统微处理器的特定处理任务。例如,数学协处理器可以控制数字处理;图形协处理器可以处理视频绘制。例如,intel pentium微处理器就包括内置的数学协处理器。

协处理器可以附属于ARM处理器。一个协处理器通过扩展指令集或提供配置寄存器来扩展内核处理功能。一个或多个协处理器可以通过协处理器接口与ARM内核相连。

协处理器可以通过一组专门的、提供load-store类型接口的ARM指令来访问。例如协处理器15(CP15),ARM处理器使用协处理器15的寄存器来控制cache、TCM和存储器管理。

协处理器也能通过提供一组专门的新指令来扩展指令集。例如,有一组专门的指令可以添加到标准ARM指令集中,以处理向量浮点(VFP)运算。

这些新指令是在ARM流水线的译码阶段被处理的。如果在译码阶段发现是一条协处理器指令,则把它送给相应的协处理器。如果该协处理器不存在,或不认识这条指令,则ARM认为发生了未定义指令异常。这也使得编程者可以用软件来仿真协处理器的行为(使用未定义指令异常服务子程序)。

80486CPU之前有协处理器,提高浮点运算能力,那时cpu较弱才有的协处理器,现在速度是原来数百倍不止,pc机一般不存在协处理器了。

ARM 微处理器可支持多达 16 个协处理器,用于各种协处理操作,在程序执行的过程中,每个协处理器只执行针对自身的协处理指令,忽略 ARM 处理器和其他协处理器的指令。ARM 的协处理器指令主要用于:ARM 处理器初始化,ARM 协处理器的数据处理操作,以及在ARM 处理器的寄存器和协处理器的寄存器之间传送数据,和在 ARM 协处理器的寄存器和存储器之间传送数据。ARM 协处理器指令包括以下 5 条:

— CDP 协处理器数操作指令

— LDC 协处理器数据加载指令

— STC 协处理器数据存储指令

— MCR ARM处理器寄存器到协处理器寄存器的数据传送指令

— MRC 协处理器寄存器到ARM处理器寄存器的数据传送指令

协处理器指令介绍

1、CDP 指令

CDP 指令的格式为:

CDP 指令的格式为:

CDP{条件} 协处理器编码,协处理器操作码1,目的寄存器,源寄存器1,源寄存器2,协处理器操作码2。

CDP 指令用于ARM 处理器通知ARM 协处理器执行特定的操作,若协处理器不能成功完成特定的操作,则产生未定义指令异常。其中协处理器操作码1 和协处理器操作码2 为协处理器将要执行的操作,目的寄存器和源寄存器均为协处理器的寄存器,指令不涉及ARM 处理器的寄存器和存储器。

指令示例:

CDP P3 , 2 , C12 , C10 , C3 , 4 ;该指令完成协处理器 P3 的初始化

2、LDC 指令

LDC 指令的格式为:

LDC{条件}{L} 协处理器编码,目的寄存器,[源寄存器]

LDC 指令用于将源寄存器所指向的存储器中的字数据传送到目的寄存器中,若协处理器不能成功完成传送操作,则产生未定义指令异常。其中,{L}选项表示指令为长读取操作,如用于双精度数据的传输。

指令示例:

LDC P3 , C4 , [R0] ;将 ARM 处理器的寄存器 R0 所指向的存储器中的字数据传送到协处理器 P3 的寄存器 C4 中。3、STC 指令

STC 指令的格式为:

STC{条件}{L} 协处理器编码,源寄存器,[目的寄存器]

STC 指令用于将源寄存器中的字数据传送到目的寄存器所指向的存储器中,若协处理器不能成功完成传送操作,则产生未定义指令异常。其中,{L}选项表示指令为长读取操作,如用于双精度数据的传输。

指令示例:

STC P3 , C4 , [R0] ;将协处理器 P3 的寄存器 C4 中的字数据传送到 ARM 处理器的寄存器R0 所指向的存储器中。4、MCR 指令

MCR 指令的格式为:

MCR{条件} 协处理器编码,协处理器操作码1,源寄存器,目的寄存器1,目的寄存器2,协处理器操作码2。

MCR 指令用于将ARM 处理器寄存器中的数据传送到协处理器寄存器中,若协处理器不能成功完成操作,则产生未定义指令异常。其中协处理器操作码1 和协处理器操作码2 为协处理器将要执行的操作,源寄存器为ARM 处理器的寄存器,目的寄存器1 和目的寄存器2 均为协处理器的寄存器。

指令示例:

MCR P3,3,R0,C4,C5,6;该指令将 ARM 处理器寄存器 R0 中的数据传送到协处理器 P3 的寄存器 C4 和 C5 中。5、MRC 指令

MRC 指令的格式为:

MRC{条件} 协处理器编码,协处理器操作码1,目的寄存器,源寄存器1,源寄存器2,协处理器操作码2。

MRC 指令用于将协处理器寄存器中的数据传送到ARM 处理器寄存器中,若协处理器不能成功完成操作,则产生未定义指令异常。其中协处理器操作码1 和协处理器操作码2 为协处理器将要执行的操作,目的寄存器为ARM 处理器的寄存器,源寄存器1 和源寄存器2 均为协处理器的寄存器。

指令示例:

MRC P3,3,R0,C4,C5,6;该指令将协处理器 P3 的寄存器中的数据传送到 ARM 处理器寄存器中.

再举个例子:

mrc p15,0,r0,c1,c0,0;将协处理器p15的寄存器中的数据传送到ARM处理器的寄存器r0中,其中1是协处理器操作码1,0是协处理器操作码2,c1存放第一个操作数的协处理器寄存器,c0存放第二个操作数的协处理器寄存器CP15协处理器详解

1、CP15的作用及指令

CP15-系统控制协处理器 (the system control coprocessor)他通过协处理器指令MCR和MRC提供具体的寄存器来配置和控制caches、MMU、保护系统、配置时钟模式(在bootloader时钟初始化用到)。CP15的寄存器只能被MRC和MCR(Move to Coprocessor from ARM Register )指令访问,其格式如下:

MCR{cond} p15,<Opcode_1>,<Rd>,<CRn>,<CRm>,<Opcode_2>

MRC{cond} p15,<Opcode_1>,<Rd>,<CRn>,<CRm>,<Opcode_2>

cond:为指令执行的条件码。当cond忽略时指令为无条件执行。

Opcode_1:协处理器的特定操作码. 对于CP15寄存器来说,opcode1永远为0,不为0时,操作结果不可预知

Rd:作为源寄存器的ARM寄存器,其值将被传送到协处理器寄存器中,或者将协处理器寄存器的值传送到该寄存器里面

CRn:作为目标寄存器的协处理器寄存器,其编号可能是C0,C1,…,C15。

CRm:协处理器中附加的目标寄存器或源操作数寄存器。如果不需要设置附加信息,将CRm设置为c0,否则结果未知

Opcode_2:可选的协处理器特定操作码。(用来区分同一个编号的不同物理寄存器,当不需要提供附加信息时,指定为0)

在基于ARM的嵌入式系统中,存储系统通常是通过系统控制协处理器CP15完成的。CP15可以包含16个32位的寄存器,其编号为0-15。实际上对于某些编号的寄存器可能对应有多个物理寄存器。在指令中指定特定的标志位(CRm和Opcode_2)来区分这些物理寄存器。有些类似于ARM寄存器中,处于不同的处理器模时,ARM某些寄存器可能不同。

2、CP15的寄存器介绍

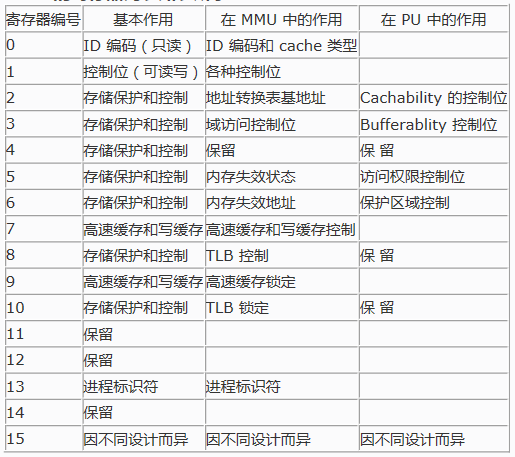

CP15 的寄存器列表如下表所示:

2.1 CP15 的寄存器 C0

CP15 中寄存器 C0 对应两个标识符寄存器,由访问 CP15 的寄存器指令指定要访问哪个具体物理寄存器,与两个标识符寄存器的对应关系如下所示:

1、主标识符寄存器

指令格式:MRC P15,0,R0,C0,C0,0 #将主标示符寄存器的内容读到AMR寄存器R0中

主标示符的编码格式对于不同的ARM处理器版本有所不同。对于AMR7之后的处理器,其主标示符编码格式如下 :

各部分的编码详细含义如下表所示:

2、cache类型标识符寄存器

指令格式:MRC P15,0,R0,C0,C0,1 #将cache类型标识符寄存器的内容读到AMR寄存器R0中

ARM 处理器中 cache 类型标识符寄存器的编码格式如下所示:

各部分的编码详细含义如下表所示:

控制字段位 [28 : 25] 的含义

主要用于定义对于写回类型的cache的一些属性,cache 类型标识符寄存器的控制字段位 [28 : 25]:

控制字段位 [23 : 12] 及控制字段位 [11 : 0] 含义

[23:12]用于定义数据cache的属性,[11: 0]用于定义指令cache的属性。编码格式如下:

其中bits[1:0]含义如下:

其中bits[5:3]含义如下:

其中bits[8:6]含义如下:

2.2 CP15 的寄存器 C1

CP15中的寄存器C1是一个控制寄存器,它包括以下控制功能:

指令如下:

mrc p15, 0, r0, c1, c0{, 0} ;将 CP15 的寄存器 C1 的值读到 r0 中

mcr p15, 0, r0, c1, c0{, 0} ;将 r0 的值写到 CP15 的寄存器 C1 中

CP15 中的寄存器 C1 的编码格式及含义说明如下:

2.3 CP15 的寄存器 C2

C2寄存器的别名:Translation table base (TTB) register

C2寄存器用来保存页表的基地址,即一级映射描述符表的基地址。其编码格如下所示:

2.4 CP15 的寄存器 C3

CP15 中的寄存器 C3 定义了 ARM 处理器的 16 个域的访问权限。

在 CP15的C3寄存器中,划分了 16个域,每个区域由两位构成,这两位说明了当前内存的检查权限:

00:当前级别下,该内存区域不允许被访问,任何的访问都会引起一个domain fault,这时 AP位无效

01:当前级别下,该内存区域的访问必须配合该内存区域的段描述符中AP位进行权检查

10:保留状态(我们最好不要填写该值,以免引起不能确定的问题)

11:当前级别下,对该内存区域的访问都不进行权限检查。 这时 AP位无效

所以只有当相应域的编码为 01 时,才会根据 AP位 和协处理器CP15中的C1寄存器的R,S位进行权限检查

2.4 CP15 的寄存器 C5

CP15 中的寄存器 C5 是失效状态寄存器,分为指令状态失效和数据状态失效。

MRC p15, 0, , c5, c0, 0 访问数据失效状态寄存器

MRC p15, 0, , c5, c0, 1 访问指令状态失效寄存器

编码格式如下所示:

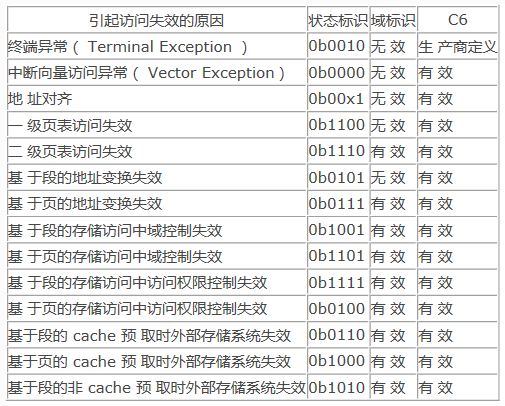

其中,域标识bit[7:4]表示存放引起存储访问失效的存储访问所属的域。状态标识 bit[3:0] 表示放引起存储访问失效的存储访问类型,该字段含义如下表所示(优先级由上到下递减)。

2.5 CP15的寄存器C6

CP15 中的寄存器 C6 是失效地址寄存器,其中保存了引起存储访问失效的地址,分为数据失效地址寄存器和指令失效地址寄存器。

MRC p15, 0, , c6, c0, 0 访问数据失效地址寄存器

MRC p15, 0, , c6, c0, 2 访问指令失效地址寄存器

编码格式如下所示:

2.6 CP15的寄存器C7

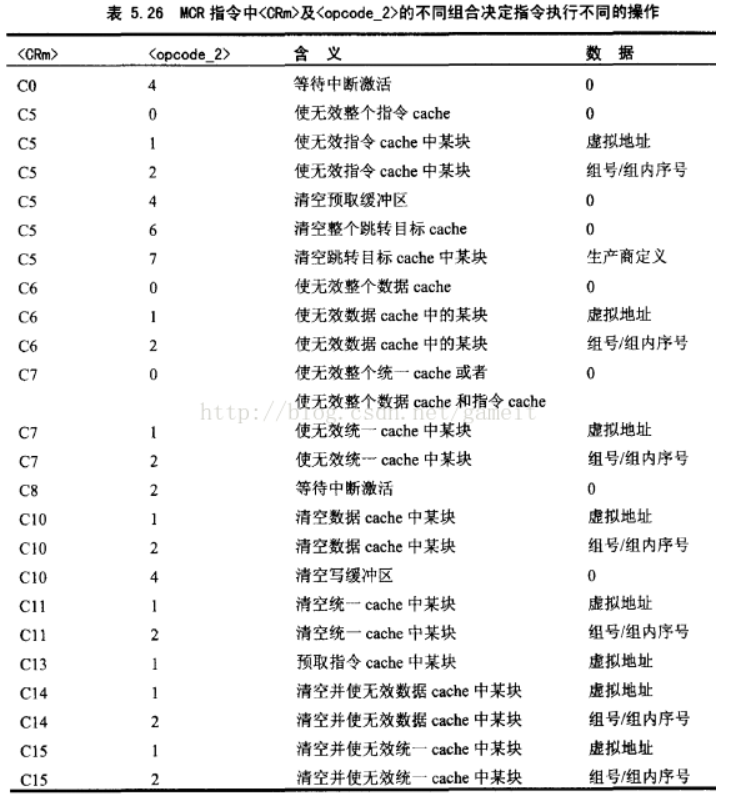

CP15 的 C7 寄存器用来控制 cache 和写缓存,它是一个只写寄存器,读操作将产生不可预知的后果。访问 CP15 的 C7 寄存器的指令格式为:mcr p15, 0, Rd, CRn, CRm, opcode_2 。具体含义如下表所示(表中的数据是指Rd中的数据)

2.7 CP15的寄存器C8

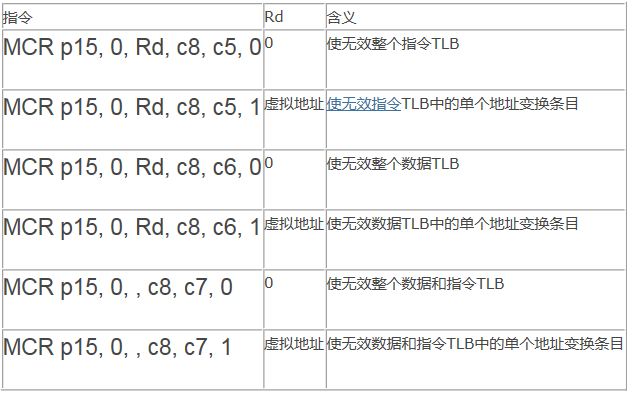

系统协处理器CP15的寄存器C8就是清除TLB内容的相关操作。它是一个只写的寄存器。

MCR p15,0,Rd,c8,CRm,opcode_2

Rd中为要写入C8寄存器的内容,CRm和opcode_2的不同组合决定指令执行的不同操作。

2.8 CP15的寄存器C12

CP15寄存器C12用来设置异常向量基地址,其编码格式如下所示:

MCR p15, 0, , c12, c0, 0 ;Rd中存放要修改的异常向量基地址

注:只有ARM11和cortex-a 可以任意修改异常向量基地址。arm7,ARM9,ARM10只可以在0地址或0xffff0000中

2.9 CP15的寄存器C13

CP15中的寄存器C13用于快速上下文切换。其编码格式如下所示

其中, 在读操作时,结果中位[31::25]返回PID,其他位 的数值是不可以预知的。写操作将设置PID的值。当PID的值为0时,MVA = VA | (0(PID)<<25),MVA=VA,相当于禁止了FCSE。系统复位后PID即为0。当PID的值不为0时,相当于使能了FCSE。