第一关:MIPS指令译码器设计

要求我们设计译码器,那么首先要知道要指令的具体格式,通过查阅MIPS指令手册可以知道

| OP | Func | |

|---|---|---|

| SLT | 000000 | 101010 |

| BEQ | 000100 | / |

| ADDI | 001000 | / |

| LW | 100011 | / |

| SW | 101011 | / |

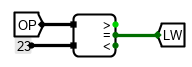

于是将获得的OP、Func和常数对比就行,相同输出1

以下给出例子:

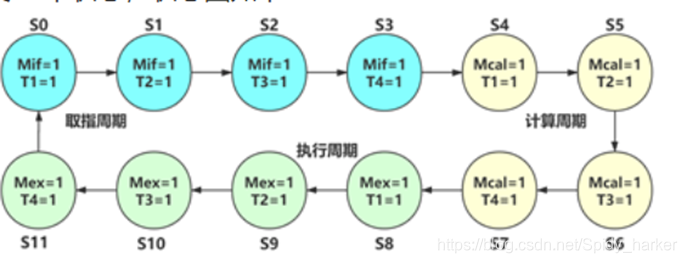

第2关:定长指令周期—时序发生器FSM设计

根据下图,知道次态和原态之间的关系。

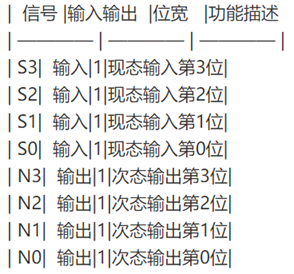

输入输出:

法1:

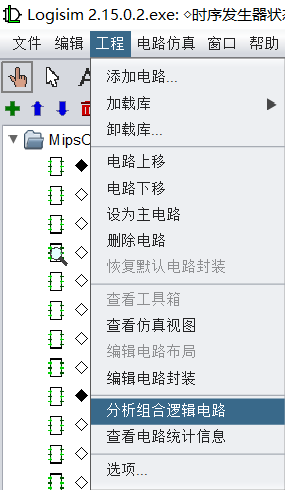

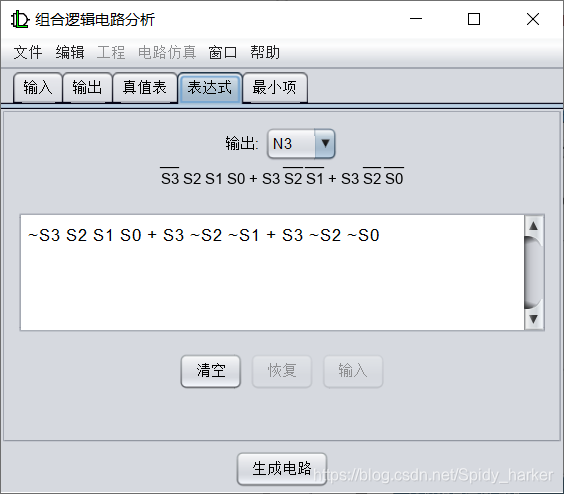

填写表格,生成表达式:

输入表达式:

法2:

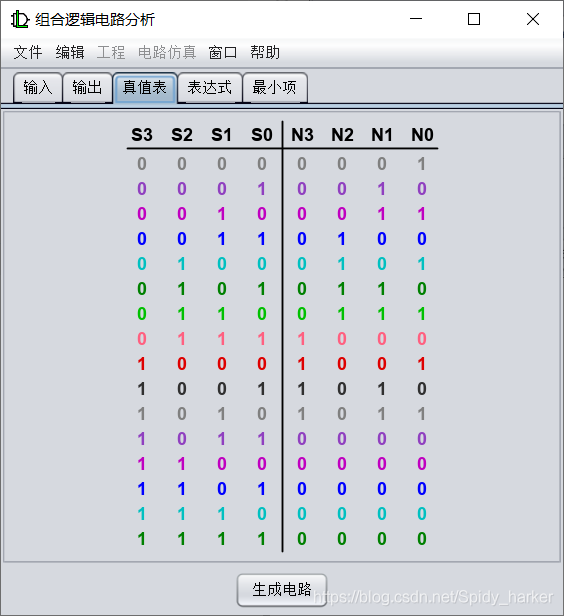

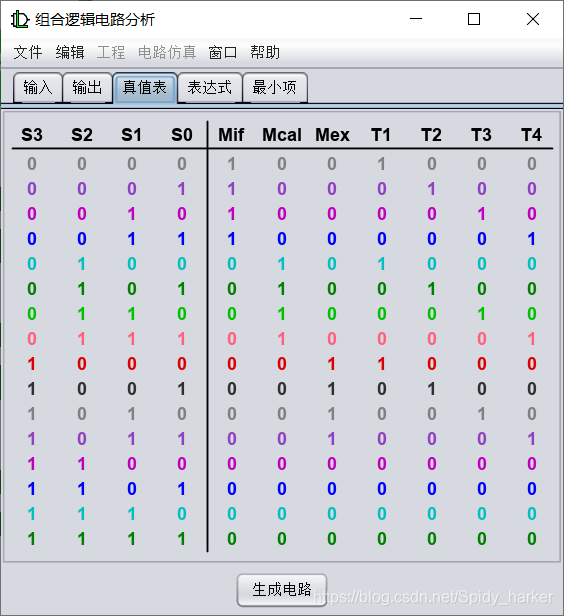

直接填真值表:

第3关:定长指令周期—时序发生器输出函数设计

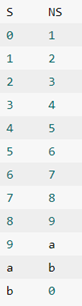

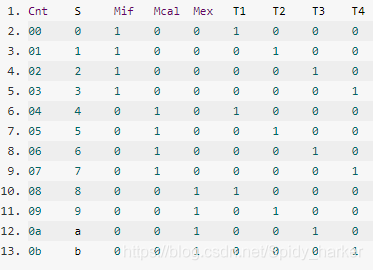

解法:同样根据测试用例,填写表格

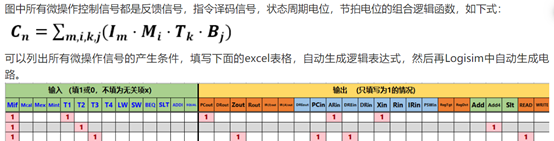

第4关:硬布线控制器组合逻辑单元

解法:

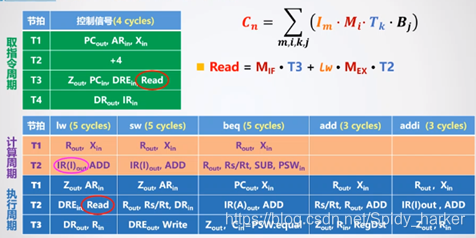

根据下表,填写题目给的excel表格。

注意:slt指令的执行周期输出信号如下

T1:rout xin

T2:rout rs/rt slt

T3:zout rin regdst

rs/rt是regtgt信号,Cin是PCin(当输入equal=1,T3=1,beq时,输出PCin=1)

将excel生成的表达式输入到logisim中。

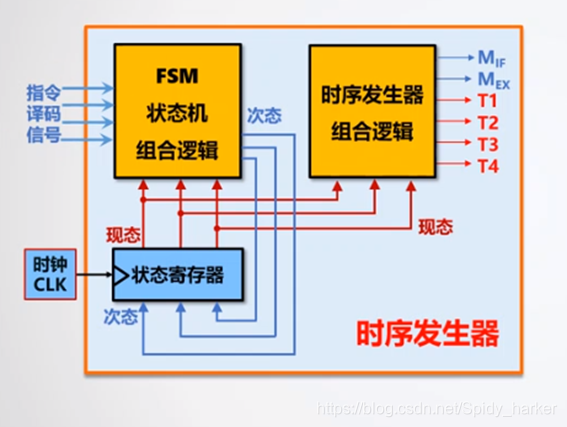

第5关:定长指令周期—硬布线控制器设计

解法:根据下图连线

提醒:指令信号没用到,CLK接的位置如下;

第六关:

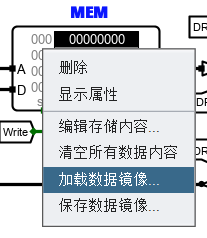

根据题目,加载数据

运行就行,提交。