文章目录

计组真的太难了!

这一章节安排的目的其实是有种亡羊补牢的安排意思,计组这门学科还真的是又臭又长,为何是亡羊补牢?因为我们在学习了CPU这一章节后,我们只知道CPU通过发出控制信号控制各个数据之间的传输等等,然而这个控制信号我们也知道是传到控制总线上的,然后通过控制总线找到要控制的寄存器或者其他部件,但是有一个问题没有解决,就是我们的CPU控制信号发出后,我们要control的对象没有考虑到,也就是我学习CPU的时候一直在说传数据传数据,但是传的数据是到哪里的,是外部存储器还是我们的内存甚至说我们的打印机等等。转念一想现在这么多外部设备都能同时连接和被CPU发出控制信号控制,那就一定是实现了,假设说我们实现了对专门的部件控制后,难道我CPU只能对一个设备运作吗,假如我对接的是一个打印机,打印机速度这么慢,那我接入的USB,我希望在USB里面打开某某学习资源的话那岂不是要等到打印机打印完CPU才能轮到我的学习资源打开,这谁忍得了?这里的总线学习其实主要学习的就是总线的控制,总线的控制权怎么分配,基本是围绕外部设备进行学习的。

学习中有一个注意的坑,就是我总是会掉进操作系统的坑,我们现在学习的是计算机组成原理,我们只需要按照上面交付下来的指令就行了,操作系统会实现并发技术,会实现这么多应用到底如何同时运行,而计组中只需要执行一条条指令就行,我们不用管,我们只需要根据特定的规则正确的执行好指令就行,计组中最像操作系统的一个就是微程序控制器设计部分,其他都是指令、信号、01数据,总的来说计组恶心的一批。(个人观念,不喜勿喷)

总线概述

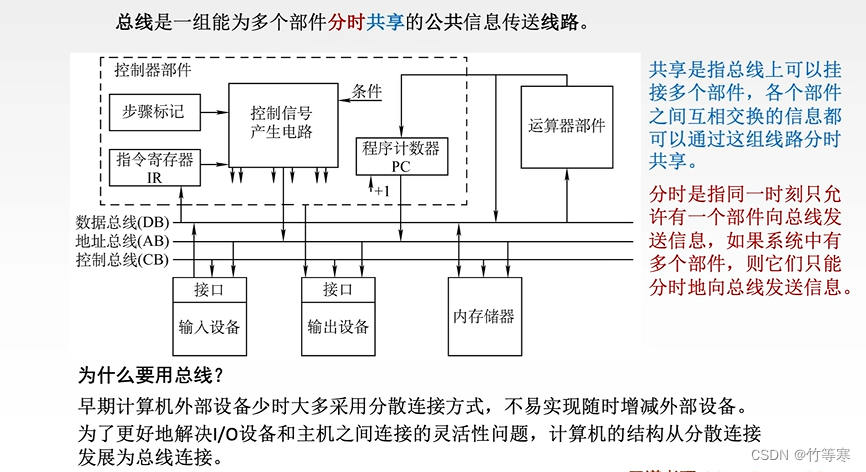

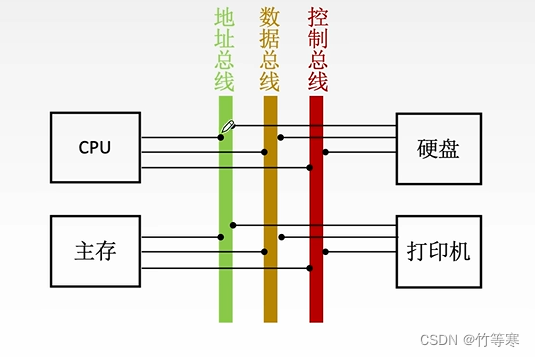

流程:CPU发出一条控制信号发到控制总线,然后互控制总线找到对应的设备,然后设备对控制总线就有了控制权,拿到控制权后就可以发出控制信号发到控制总线中,然后设备对应的指令就可以给到CPU执行,然后CPU就会继续发出控制信号这时候就会将数据传到那个设备上,或者你用的是U盘的话就是将U盘数据拷贝到计算机中等等操作,总之一切的操作都是因为信号的发出而执行,计组中万变不离其宗的就是这个。

总线的作用

- 数据总线

传输数据 - 地址总线

传输地址 - 控制总线

收到CU控制单元发过来的信号后在控制总线中完成控制操作,即完成指令操作,因为指令的执行就是一系列的信号,将两根线导通,通过数据总线进行数据传输就行 - 细节:我们有时候可以只设计一个总线既可以传输数据也可以传输地址,因为地址也是数据。(优点:减少了电路复杂,缺点:慢)

上面的理论知识应该一看就知道了,没啥好解释。

用我自己的观点总结一下下面这个图:首先我们现代计算机使用总线是因为总线是一个共享的总线,意思是每一个微操作都是在总线中传输数据或者接受数据,又因为共享的原因,必然会出现冲突,正所谓免费的东西谁不想拿,所以总线中接入的设备也是,每一个设备都希望自己能够抢到总线的控制权,但是我们的每一根总线在出传输的过程中只允许两个设备之间传输,即只允许一份数据在运输(tips:一根总线不代表只能有一条电路线,这个一条总线的意思是一份数据传过去需要这一条总线,总线里面多少条线是看传输多少位比特的,当然也有可能真的只有一条线每次传输一个bit),我们关注点关注在控制总线中,我们这时候有三位设备都需要用得到控制总线的控制权,这时候怎么办?这是我们这章节主要解决的事情,这个解决策略在整个计算机体系中好像都见到过他的身影,就是解决办法的思想我觉得确实很优雅!

简单过一下流程:CPU内部的控制单元CU发出控制信号到控制总线,然后控制总线就会知道导通哪两个寄存器进行数据传输,假设这时候控制权给到外部设备,外部设备同样可以发出控制信号数据出口和数据入口进行数据传输。

:::

外部设备居然可以发出控制信号!OK,就单单这个操作,我们自己都可以设计一个外部设备接到计算机上完成自己设计好的功能了,比如可以自己设计一个U盘。由于谁都可以设计,那接口规范问题就出现了,我们必须要有一个规范,所以现代就出现了统一的USB接口等等(题外话了)总结一下:这里其实主要是为了引出我们控制信号需要有策略的对多个设备雨露均沾一下,就是不能一直只将控制权给到同一个设备,这样的话其他设备就会发生饥饿现象,一直拿不到控制权,就会一直处于等待状态。

串行总线与并向总线

不要忘记了,一根总线不代表传输的电路线只有一条,就好比充电线,你说一条充电线,但是你拆看里面肯定不止一根电线。我这个例子举得是真的好啊。

- 串行总线

串串相信都知道了,串行总线意思是一根总线里面只有一根传输的电路线,所以我们在串行总线传输中,每次只能够传输一个bit。 - 并行总线

最常见的,一根总线内有多条电线一起传输数据,有多少条就可以传输多少位

不要觉得串行就一定比并行慢,现代的USB使用的基本都是串行了,因为我们的并行的电路线会产生磁场会产生影响,这会导致并行传输变慢,但是我们串行就不会有这个影响,因为只有一条,没有其他线的影响,有可能串行在高频率的情况下是会快过并行的。(再说了现代的USB基本都是串行了)

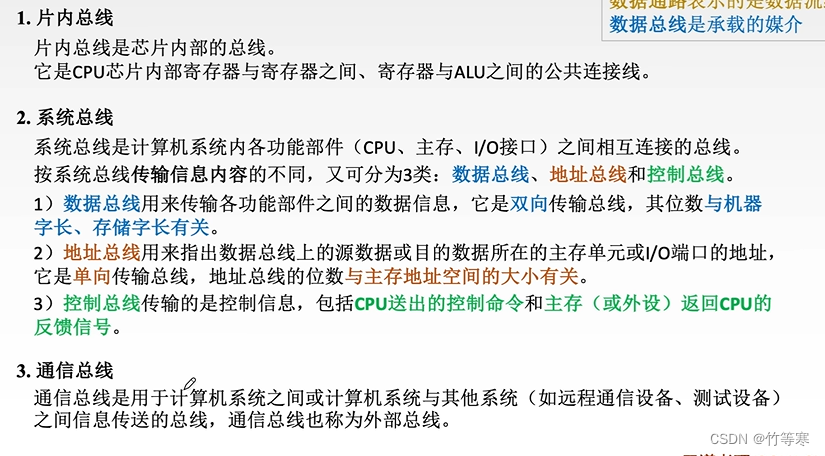

总线分类

片内就是学习CPU的时候讲的内部总线

通信总线就是可以理解为网线

总线结构

- 单总线结构:仅仅使用一条总线来传输

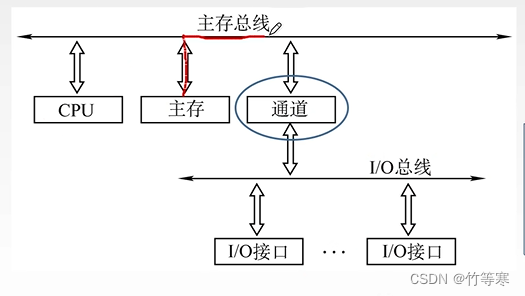

- 双总线结构

这里不是片面意思,他要用两条的原因是我们有设备传输数据很慢,但是他又拿到了控制权,所以必须要等待他传输完成,这时候我们就想到要把这个这么慢的,比如访问外存或者IO设备的单独开一天总线,可以叫他为IO总线,那靠近CPU的叫做主存总线,开辟了IO总线后,我们主存总线与IO总线进行通信数据传输需要一个中介,所以就设计了一个通道专门用来两条总线之间数据的传输的。在这个总线结构中还支持在主存中突发传送,就是一个地址传过去可以收到多个地址连续的数据,这里我猜是局部性原理

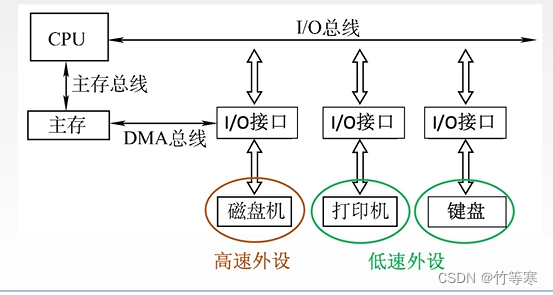

- 三总线结构

增加了一个DMA总线,学过操作系统的应该知道我们的磁盘存取数据单位是一块一块的进出的,但是总线办不到一次性传一块,所以我们就旁路了一条DMA总线对磁盘块数据传输。

总线性能指标

- 总线的传输周期

申请控制权阶段开始到数据传输结束的时间

申请阶段:后面会学到的仲裁技术,意思就是多个设备之间如何分配控制权,设备在希望使用的时候都需要申请控制权,但是是否能拿到就需要有仲裁机构。这里的机构可以是一个部件专门来分配控制权给设备的。

-

总线的时钟周期

时钟周期就是节拍,CPU的主频的倒数就是时钟周期

比如:一份CPU主频为3.0GHZ,那么时钟周期=1/3.0G -

时钟频率 = 1/时钟周期

-

工作频率

时钟频率/传输周期所占的时钟周期个数 -

总线宽度

一次传输的bit数(即数据总线的根数) -

总线带宽

带宽一股计网味道,所以肯定是算流水量的,因此它是计算数据传输率

总线带宽=工作频率 * 总线宽度

总线仲裁

集中仲裁

最喜欢的一部分,很人性化的一个东西

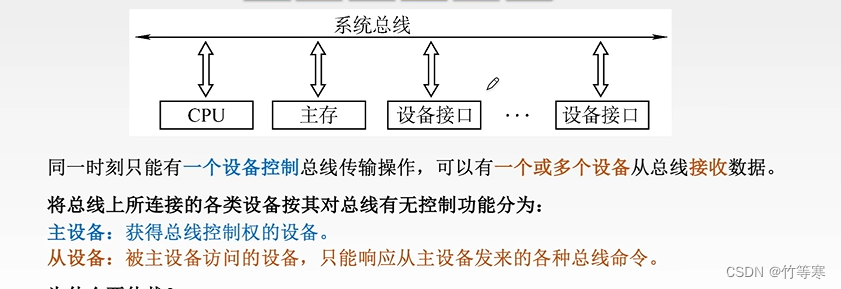

重点是记住拿到总线控制权的就是主设备,其他未拿到的就是从设备,而我们接下来要做的事情就是做策略,到底要怎么给控制权,因为控制权只有一个,必定会引起竞争。

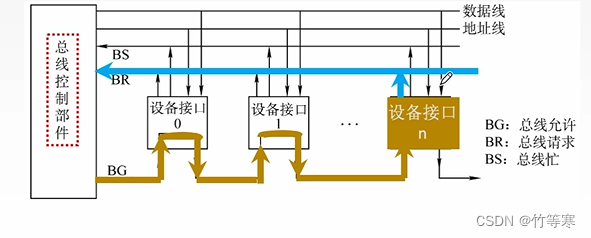

学一点装b术语

- 总线控制部件:可以理解为他就是我们的仲裁机构(膜拜就行,不要去理解他)

- BG:总线允许信号

- BR:总线请求信号

- BS:总线忙信号

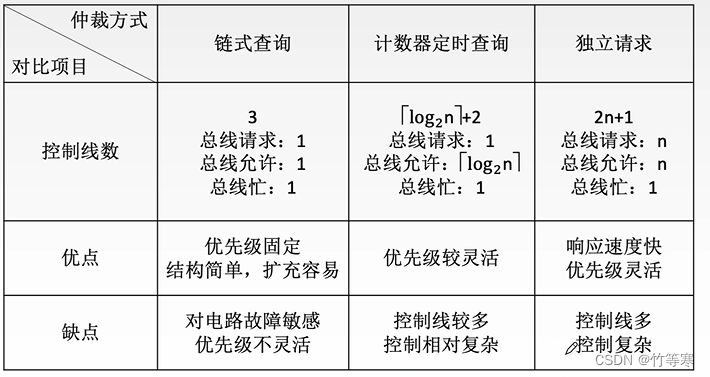

链式查询

这个方式就是纯纯的先到先得的动态上下级关系,在所有发起了BR请求中,按照链式存储的方式优先会找到设备序号最小的后,仲裁机构就会将总线控制权交给他,因为他先到的,所以先得到,后面的只有等他用完了之后控制权回到仲裁机构了,然后仲裁机构就会重复刚刚的操作,他会重新审视所有发起请求的设备,(这里是一个小细节,他不是在用完控制权的那个设备往后找),然后找序号最小那个设备交控制权。

缺点:很容易造成这条链中靠后的设备饿死状态

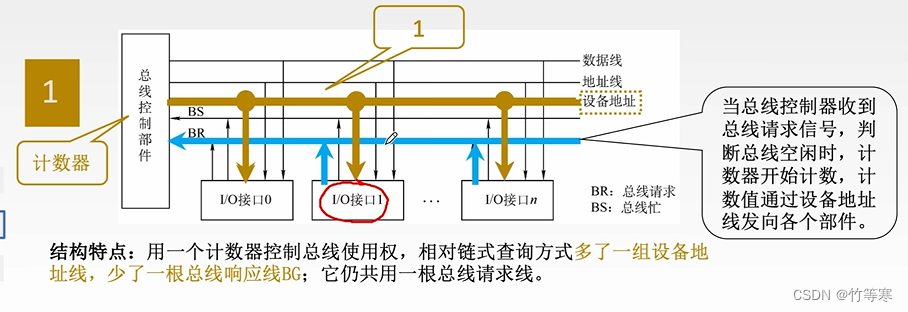

计数器查询

到这里后,将BG删掉了,但是多了一个设备地址,在这个计数器查询方式相对比较智能化一点,先说一下工作原理

第一种:计数器给完控制权后计数器不清空为0,继续加一往后

设备地址线是都连着设备的,然后他们设备照样可以发起BR请求,这时候总裁控制部件就会根据计数器从0开始顺着地址线找,计数器为0就拿着0找到0设备,找到后就看他有没有请求,有就直接将控制权给他然后计数器加一,没有就也直接将计数器加一往后找,(就像送外卖一样,对应哪个房间,但是要注意的是,我们在外面能敲门,但能不能开门就要看里面的人是否开,否则外卖也送不到),这一个确实相对公平了,因为雨露均沾,拿着令牌计数器去找,找到最后一个n,无论是否有请求,计数器会回到0。这样就完成了一轮控制权的交付。

第二种:每次交完控制权计数器清0,那这样就变回了链式查询了

::

缺点:这种方式在总线控制部件设计可能会难一点

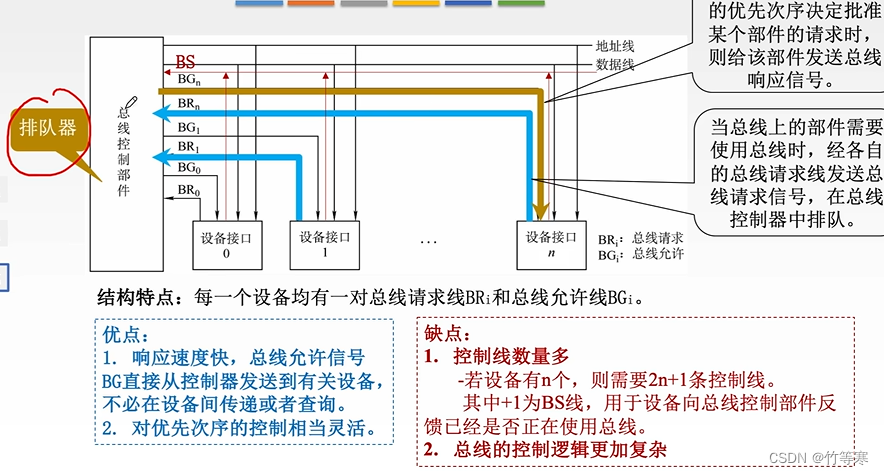

独立请求

这种方式就很粗暴了,每一个设备都有一个BG和BR,这种方式按照顺序来给控制权的但是顺序怎样是排队器调整的(咸鱼学长不深究,我也不想深究了),灵活性一下子就上来了,当然设计控制逻辑会更加复杂。

三种方式的对比

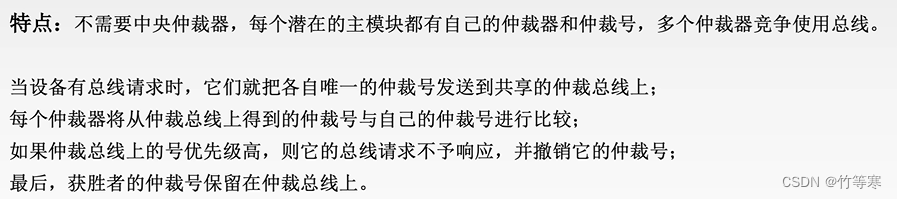

分布式仲裁

这种方式就是谁的优先级高就有权利在总线上执行,提醒一点:我们比较的是一个时刻,然后这个时刻的所有仲裁号进行比较,大者留下。

总线操作和计时

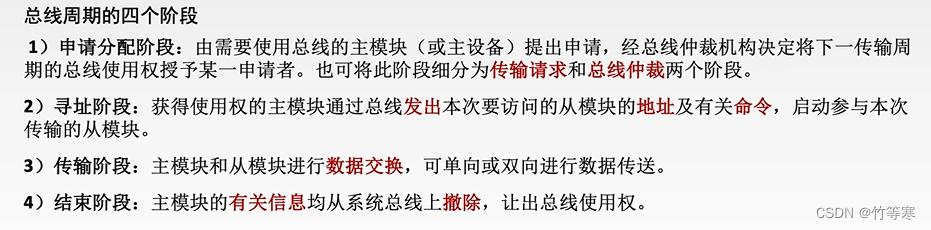

- 四个阶段

同步定时方式

下面全部以读命令作为例子执行操作

- 同步通信

这种方式就是每一个总线周期开始前都要进行仲裁控制权的申请。

每一个总线周期内的时钟周期个数都是一样的。

只能够在一个总线周期内进行一次数据的传输。

由于固定了上一个节拍完成后才能进行下一个节拍操作,或者说强制进入下一个节拍(这可能都会造成问题)

每一个节拍做完就会直接进入下一个节拍,这个同步特性最明显。

由于这个特性,在取数据阶段会导致我们内存还没出完,节拍就结束了,这时候CPU可能不知道会发生什么了。

这种设计就适用于总线长度短的,访存阶段可能需要快一点,或者说你设计阶段时间久一点。

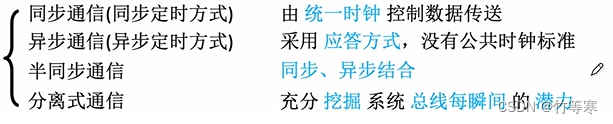

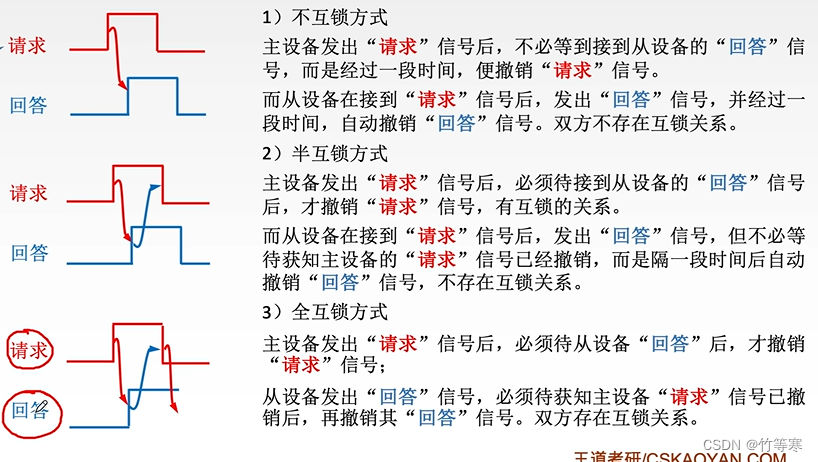

异步通信

- 异步通信

这里没有提供时钟信号,相连的时钟周期之间是通过互相通知的,或者互等待对方一段时间。

这里的请求为何有撤回的说法?

这里就是上锁解锁的思想,撤回就是解锁,如果设计的时候设计了需要等待回答或者等待请求,就需要撤销来让指令执行下去。

这里的思想其实和计网思想能够互通。

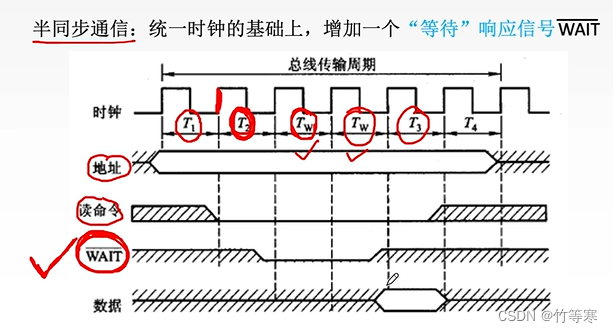

半同步通信

说白了就是加一个等待节拍,比如访存阶段未完成就用等待节拍等访存完成后就继续执行下去。

这里有一个我认为没做好的点事其实我们等待时间可以不用,我先让总线的控制权给其他人用用先不行吗,等对方也用完了等我也准备好了就再给回我控制权不行咩?(不得不佩服我,下面学的分离式通信就是使用这种方法)

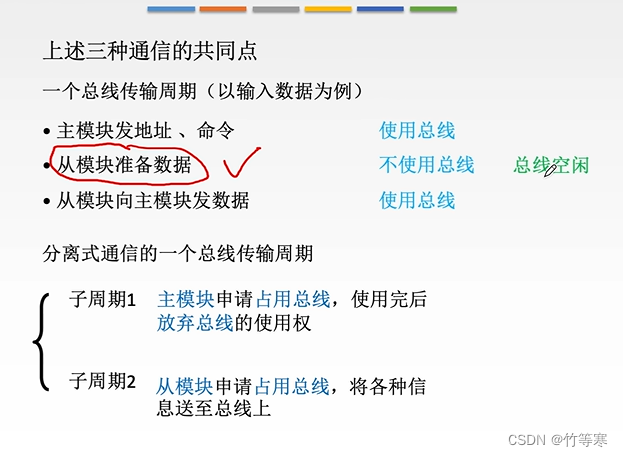

分离式通信

只要处于准备数据阶段,就主动放弃总线控制权,先放弃给其他人用着,我先准备访存数据。这样就完成了对总线空闲时间的利用。

这里亡羊补牢的章节学起来很快,因为轻舟已过CPU,CPU是计组最恶心的一部分。这章节学到的其实就是更加了解了总线信号如何实现更高的效率,并发设计和防信号冲策略。