实验要求:

- 根据实验指导书配置IP核。

- 生成一个RAM_B存储器模块,在关联文件中输入64个32位数据,用十六进制表示。

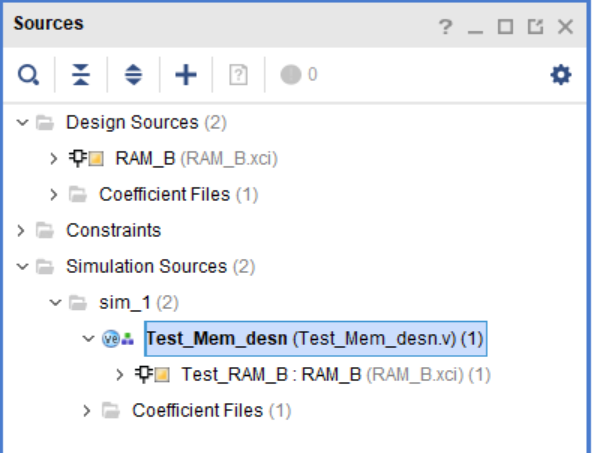

- 编写一个实验验证的顶层模块,调用2生成的存储器模块;用仿真方法设计实验验证

生成.coe文件:

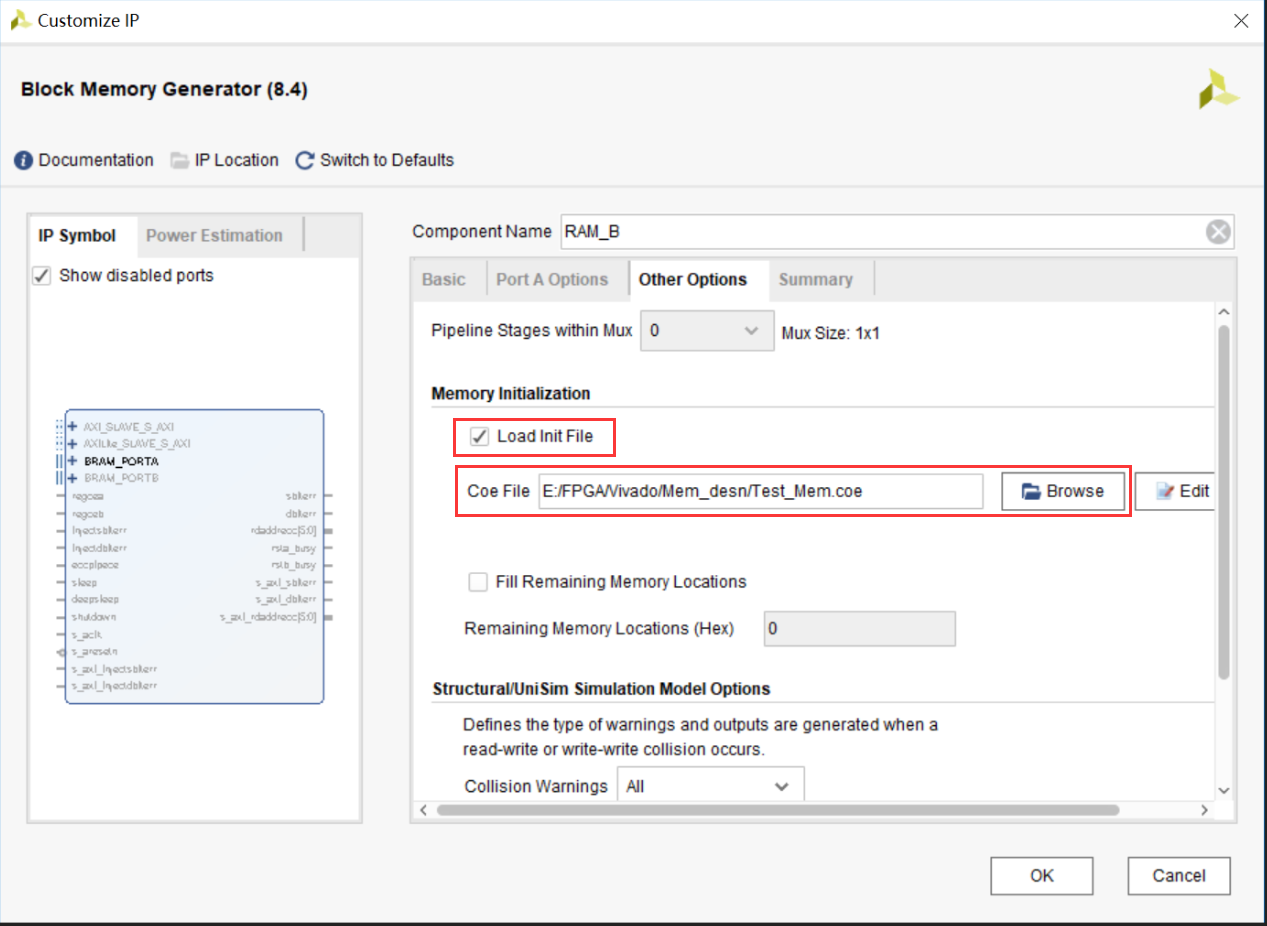

创建记事本,记事本内容为如下代码,命名为Test_Mem.coe,保存的路径最好不要有中文,不然IP核关联的时候会出现迷之报错。

memory_initialization_radix=16;//16进制

//存储器内容初始化为下面10条操作码

memory_initialization_vector=00000820 00632020 00010fff 20006789 FFFF0000 0000FFFF 88888888 99999999 aaaaaaaa bbbbbbbb;

配置IP核:

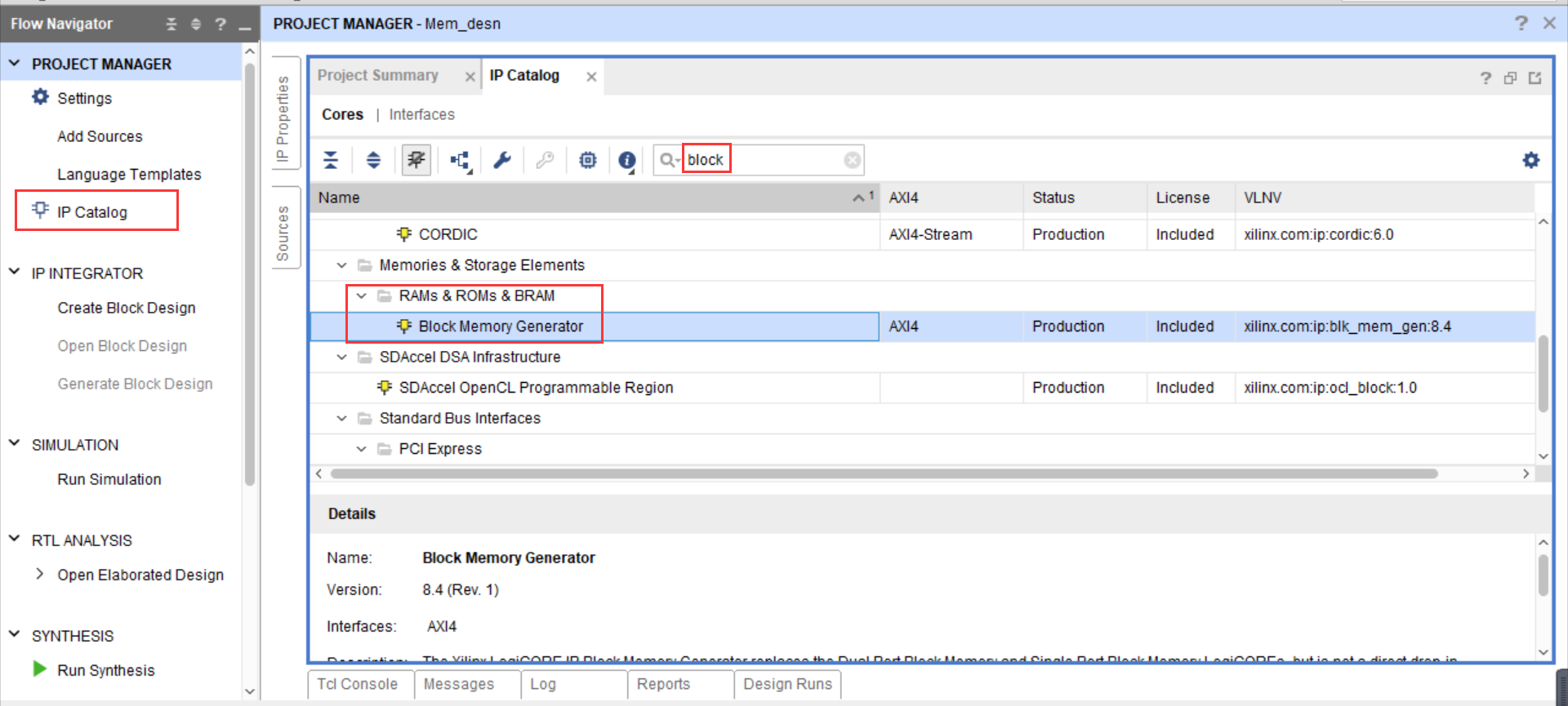

在搜索栏输入block,能快速找到实验要求的IP核型号

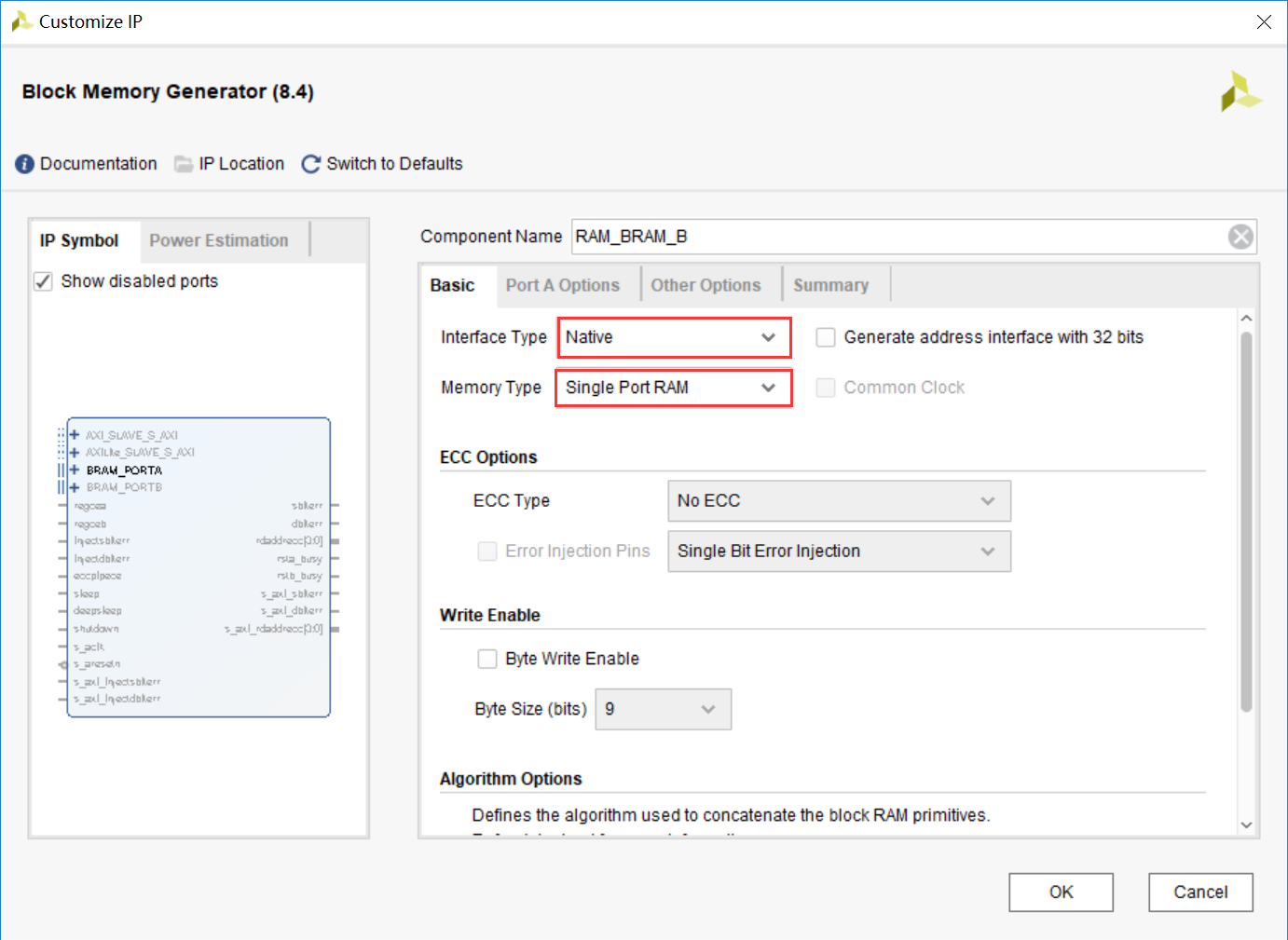

本地单端口读写存储器

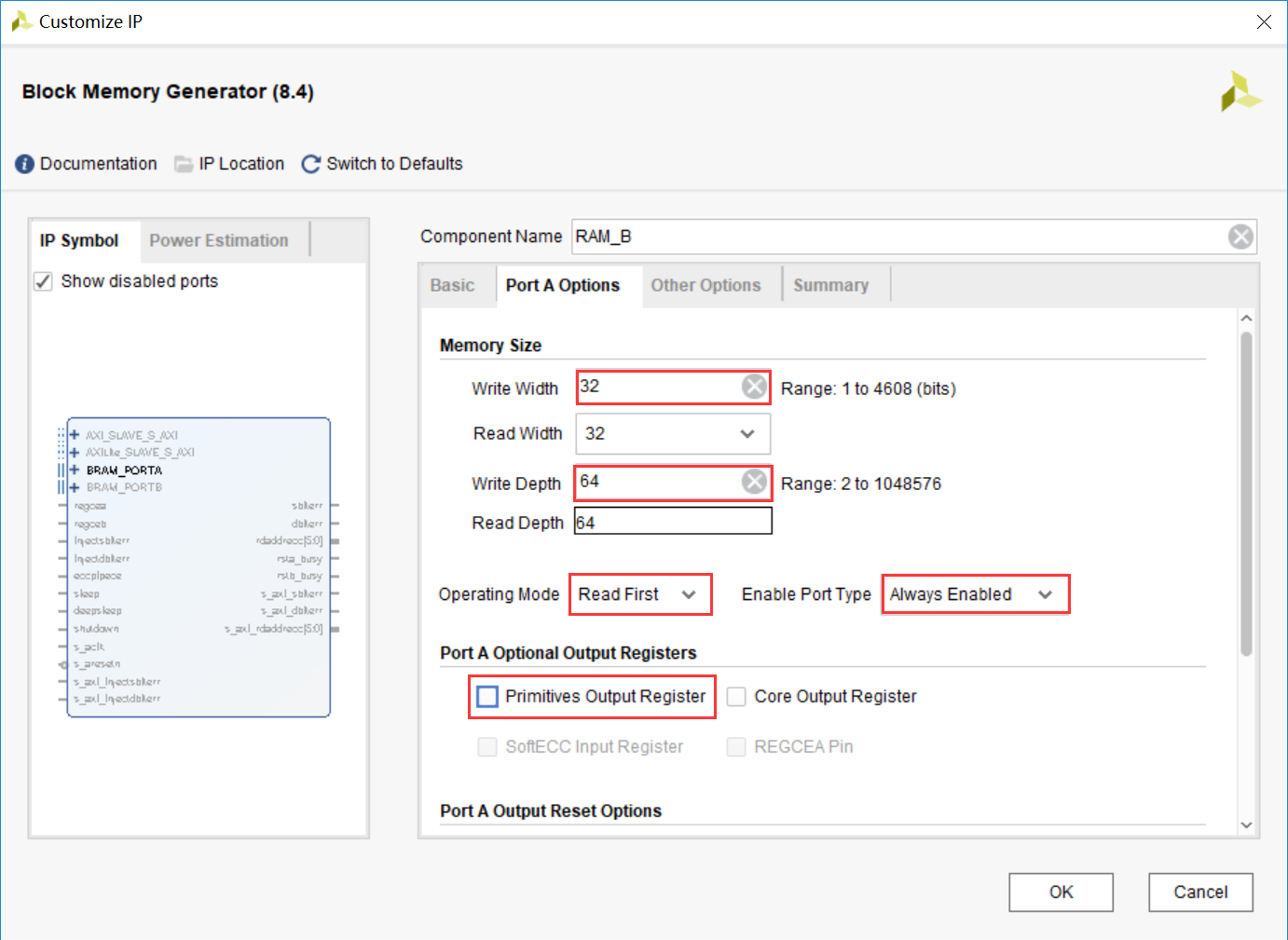

32位和64位,总是读优先,输出不需要放在寄存器里面(勾了的话,会多出一个机器周期,去寄存器里面取,才能输出)

装载初始化文件,关联上一步的Test_Mem.coe文件

编写测试模块:

程序模块结构图

测试模块代码:

`timescale 1ns / 1ps

//测试模块

module Test_Mem();

reg [7:0]Mem_Addr;//读出和写入的地址

reg [31:0]M_W_Data;//写入的数据

reg clk_m, Mem_Write;//时钟和,写控制信号(高电平有效),在时钟上升沿时写入,读也是上升沿

wire [31:0]M_R_Data;//读出的数据,输出

initial clk_m=0;

always #25 clk_m=~clk_m; //每25ns,时钟翻转一次

initial//数据初始化

begin

Mem_Addr=8'h00;Mem_Write=1'b0;

Mem_Addr=8'h01;#50;

Mem_Addr=8'h02;#50;

Mem_Addr=8'h03;#50;

Mem_Addr=8'h04;#50;

Mem_Addr=8'h05;#50;

Mem_Addr=8'h06;#50;

Mem_Addr=8'h07;#50;

Mem_Addr=8'h08;#50;

Mem_Addr=8'h09;#50;

Mem_Write=1'b1;M_W_Data=32'h66666666;#50;

end

RAM_B Test_RAM_B(

.clka(clk_m),//时钟信号端口

.wea(Mem_Write),//写控制信号端口

.addra(Mem_Addr),//读写地址端口

.dina(M_W_Data),//写的数据端口

.douta(M_R_Data)//读的数据端口

);

endmodule

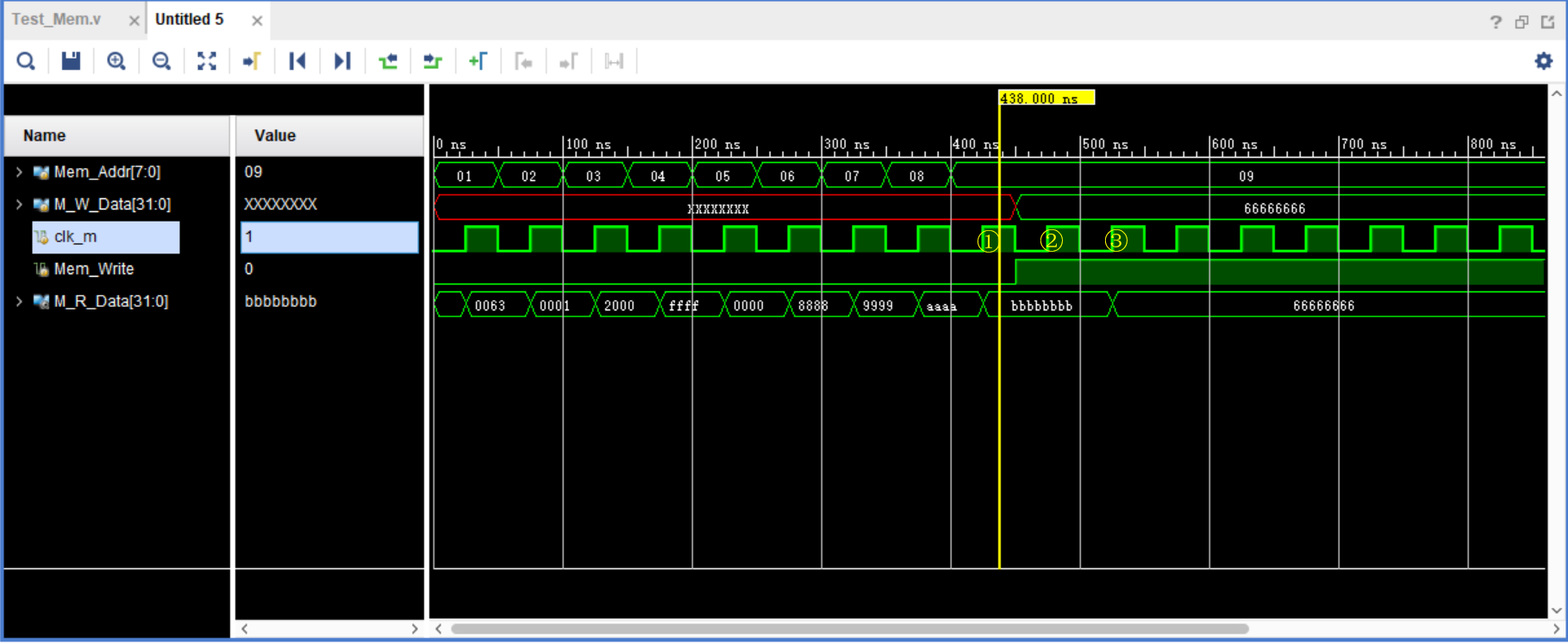

仿真波形图:

在①这个位置读出存储器地址为09的数据;②写控制信号打开,同时读和写,因为配置的时候设置的是读优先,所以读出的是旧数据;③的时候读出了刚刚我们输入的数据。