总线与微命令实验

实验环境

实验目的

- 理解总线的概念和作用。

- 连接运算器与存储器,熟悉计算机的数据通路。

- 理解微命令与微操作的概念。

实验要求

- 做好实验预习,读懂实验电路图,熟悉实验元器件的功能特性和使用方法。

- 按照实验内容与步骤的要求进行实验,对预习时填写好的微命令进行验证与调试,遇到问题请冷静、独立思考,认真仔细地完成实验。

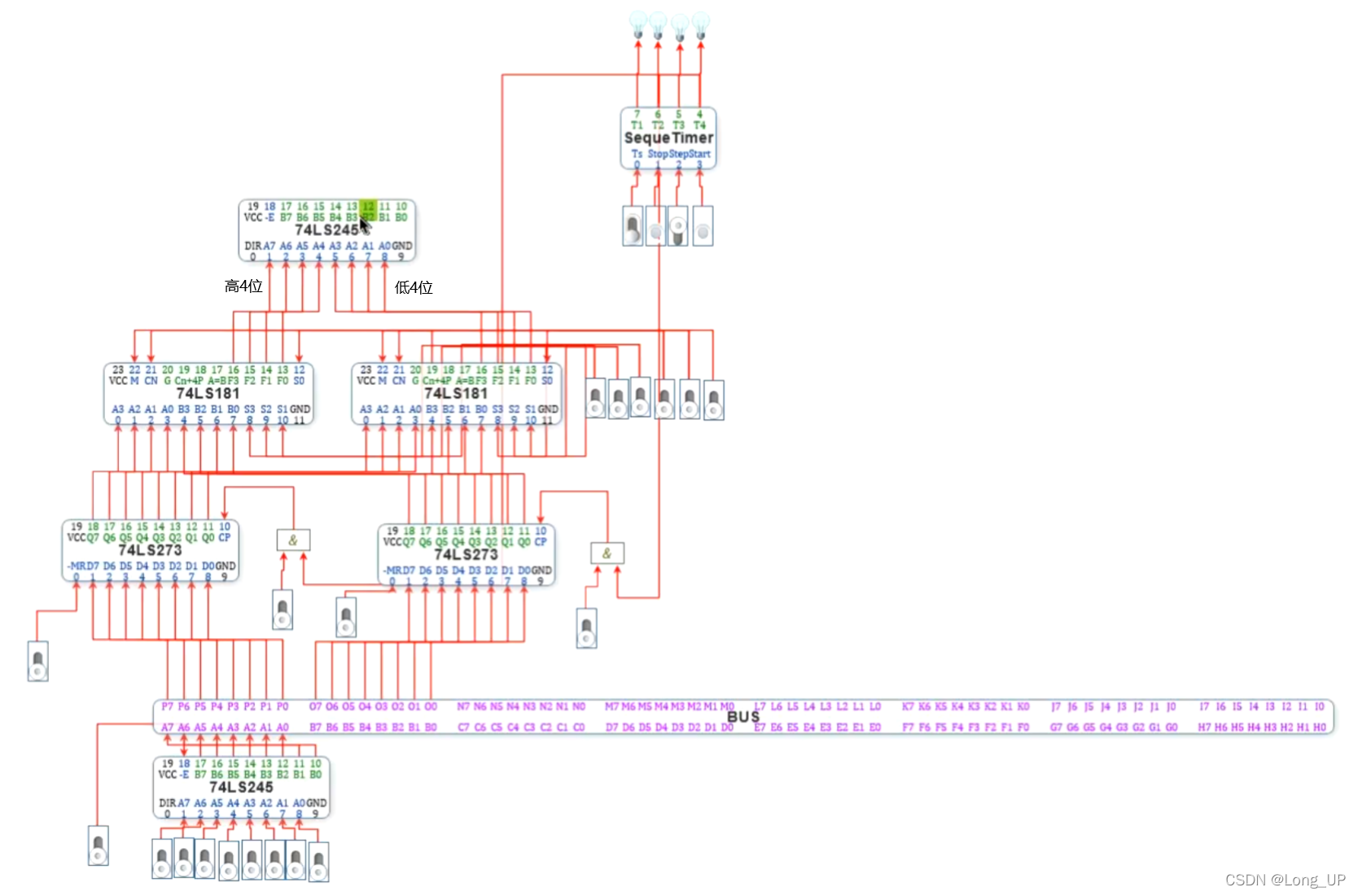

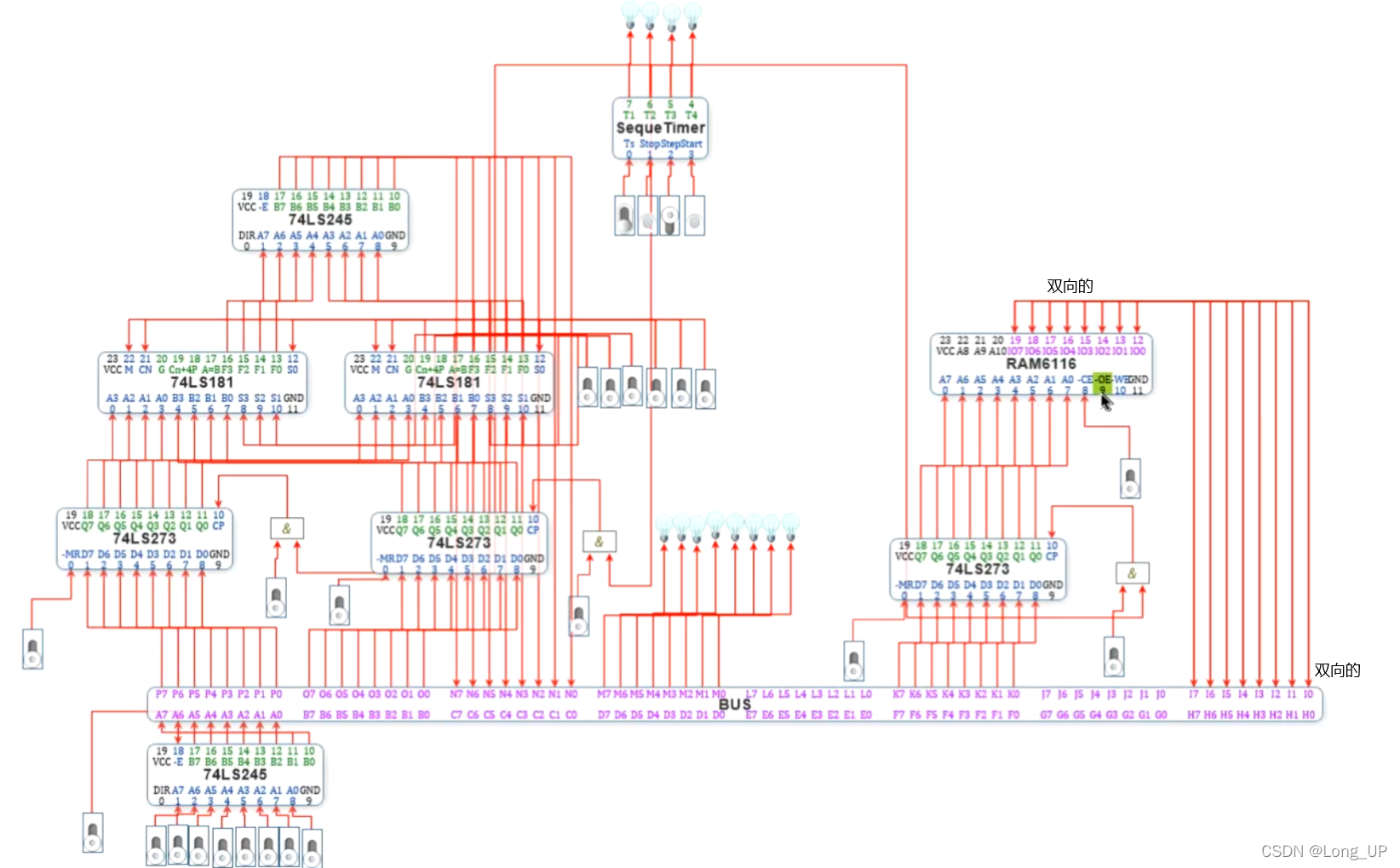

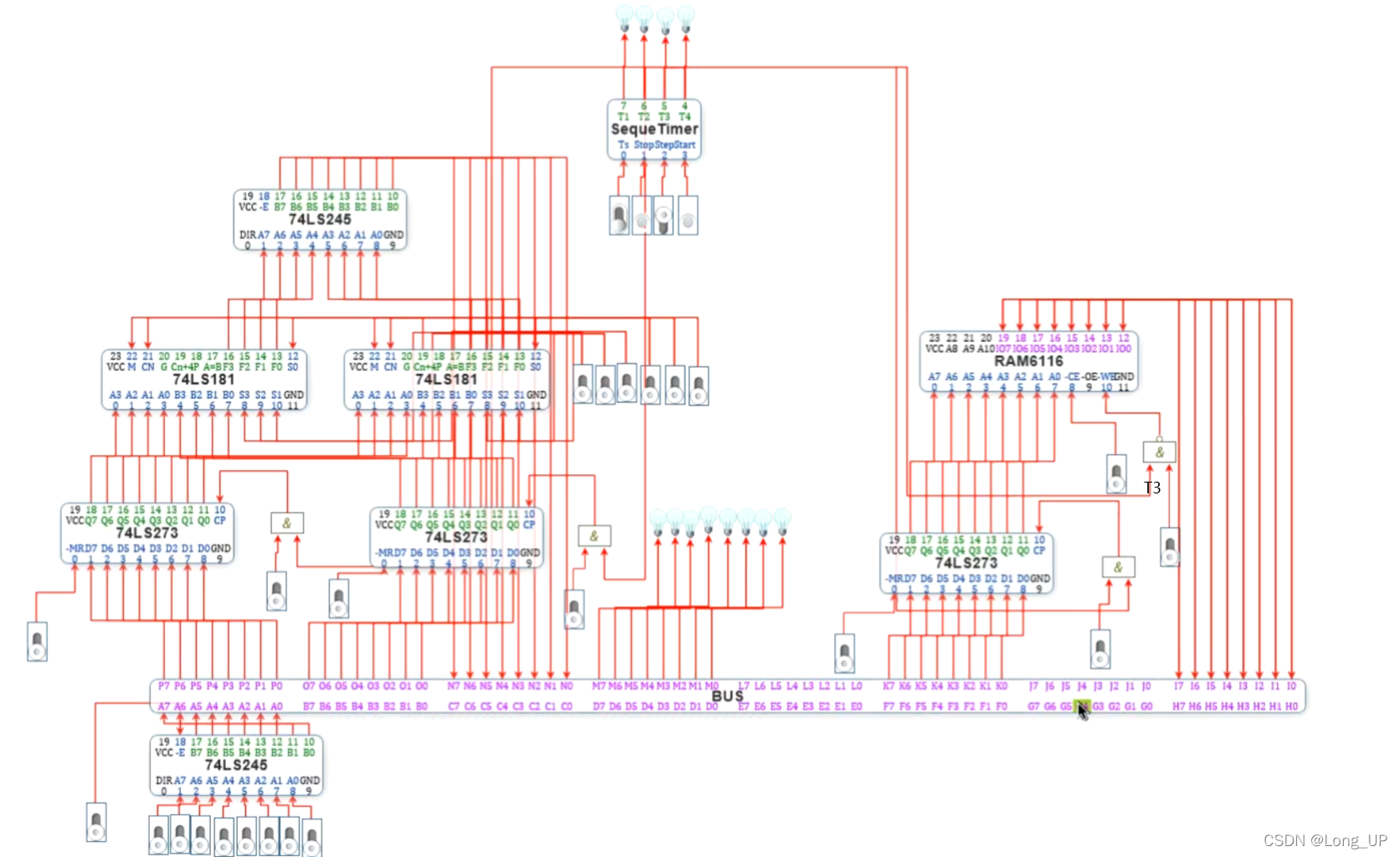

实验电路

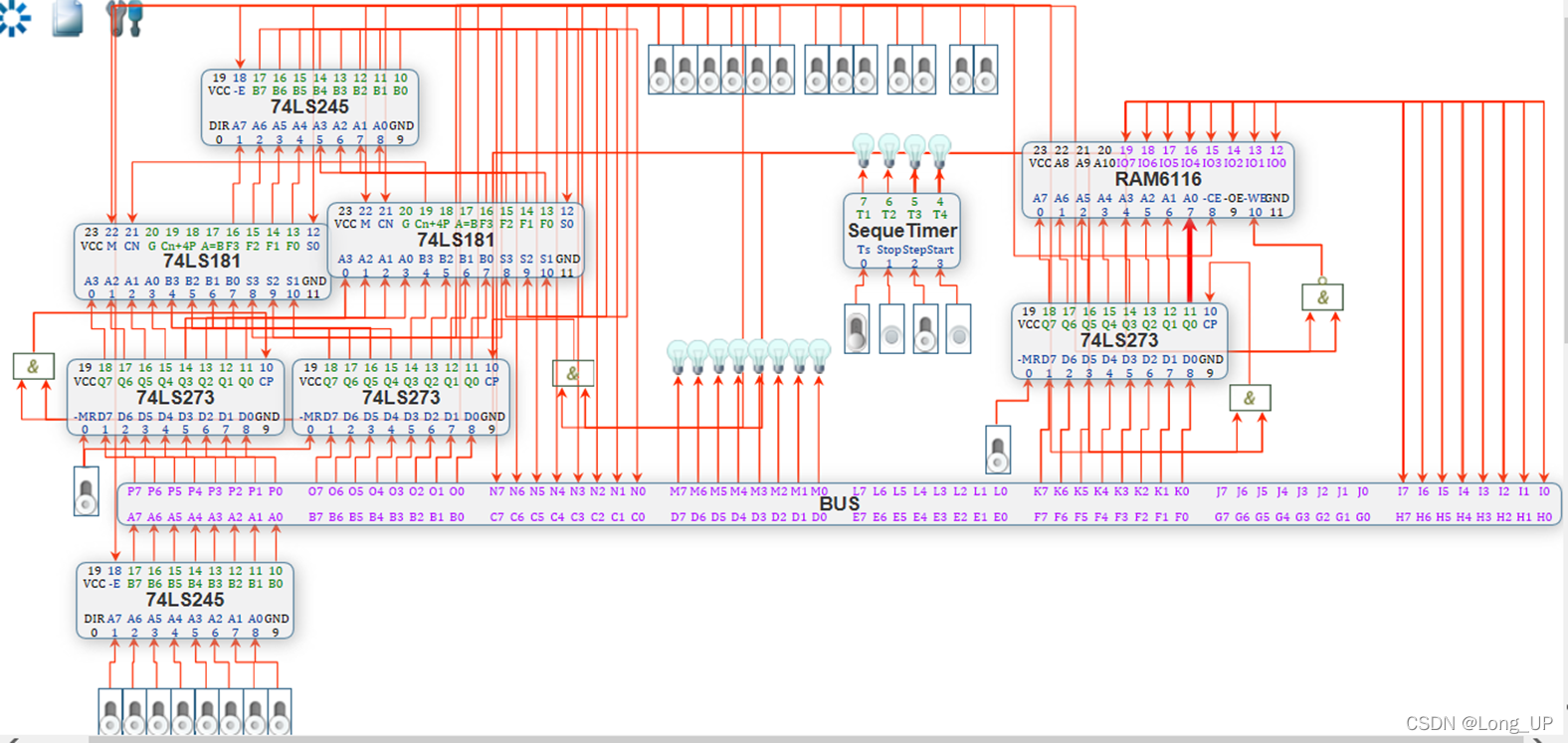

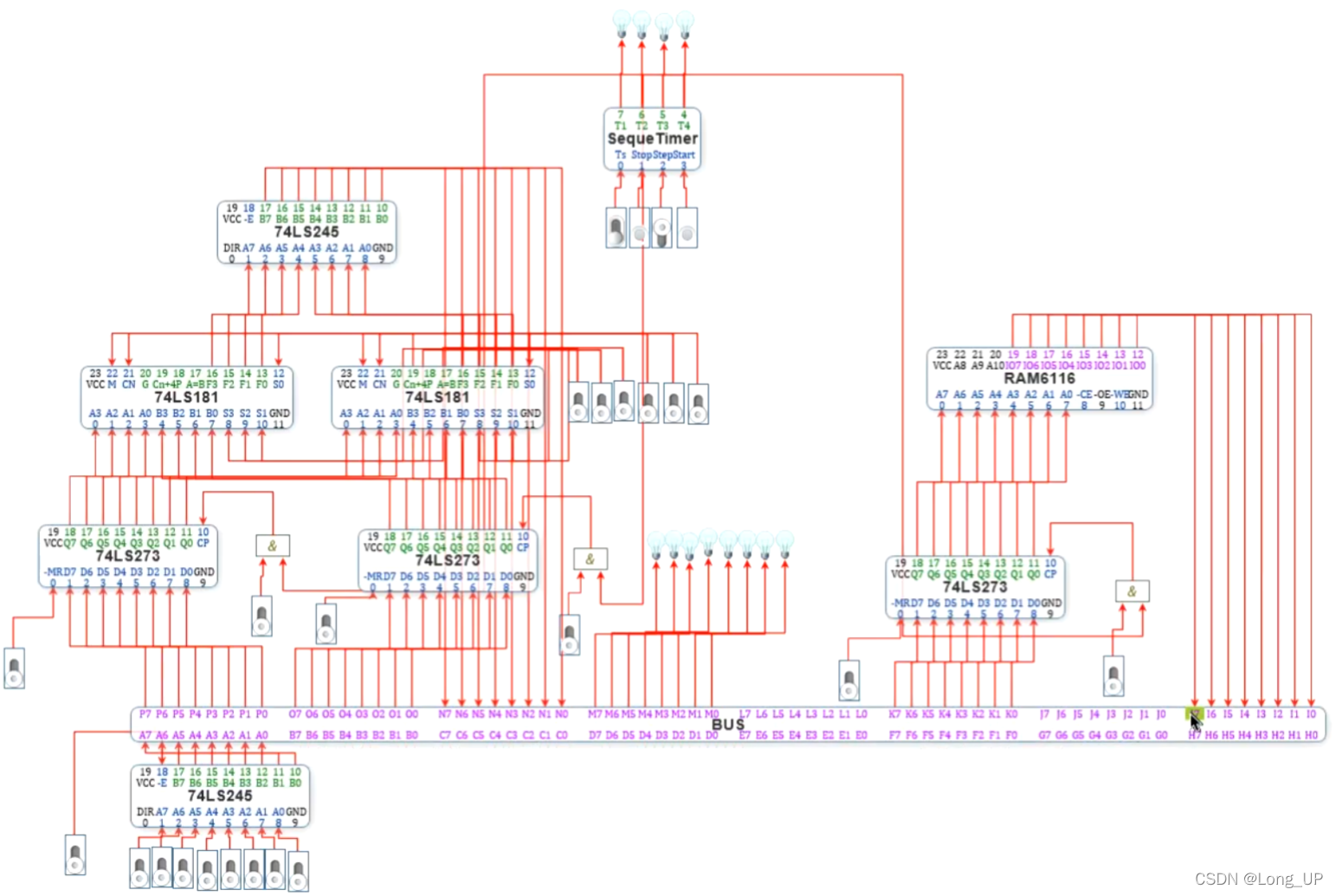

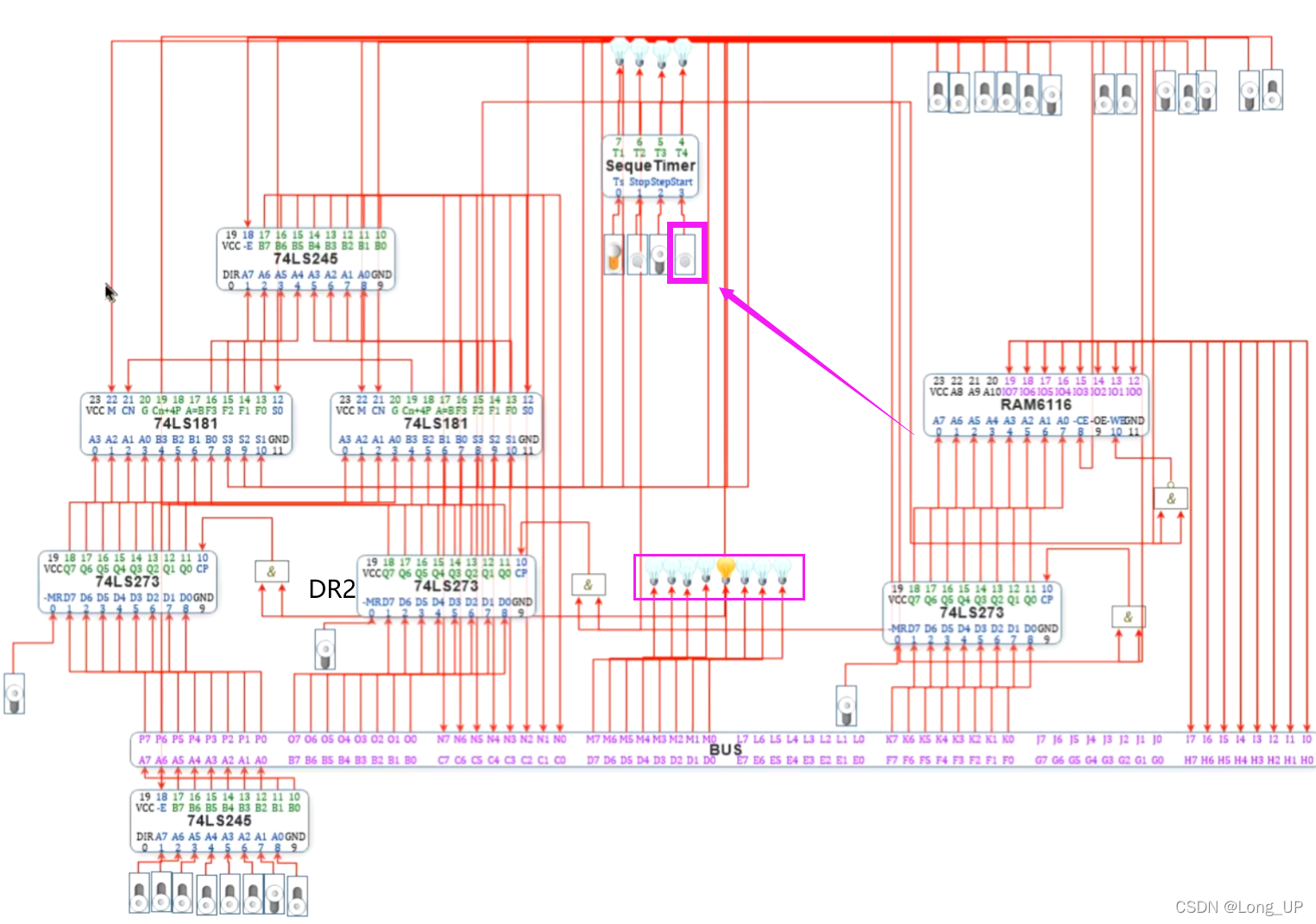

本实验使用的主要元器件有:4 位算术逻辑运算单元 74LS181 , 8 位数据锁存器 74LS273 ,三态输出的总线收发器 74LS245,2K x 8 静态随机存储器 6116 ,时序发生器,与非门、 与门、开关、指示灯等。芯片详细说明请见附录。

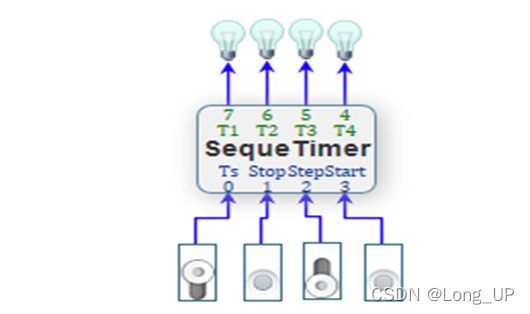

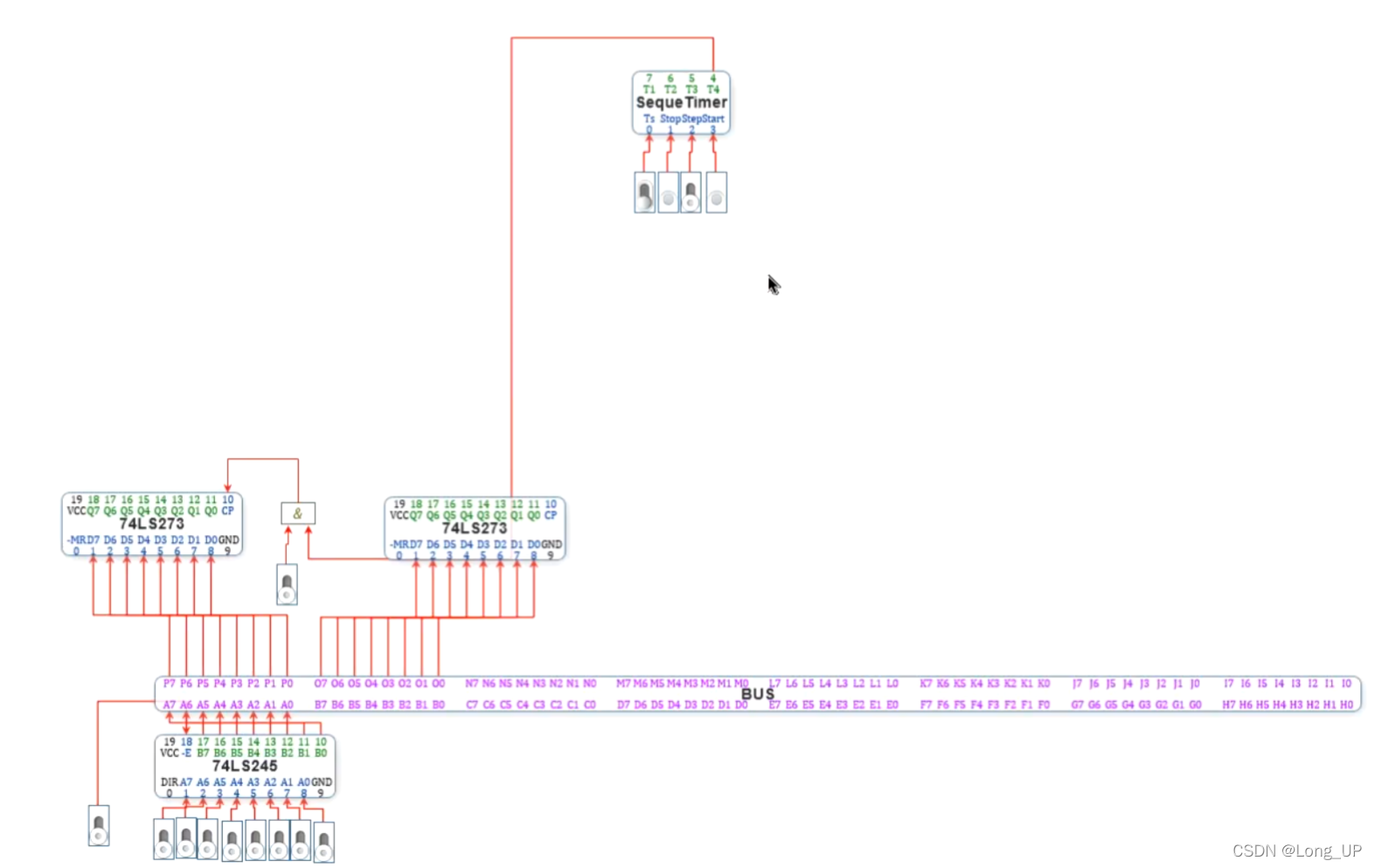

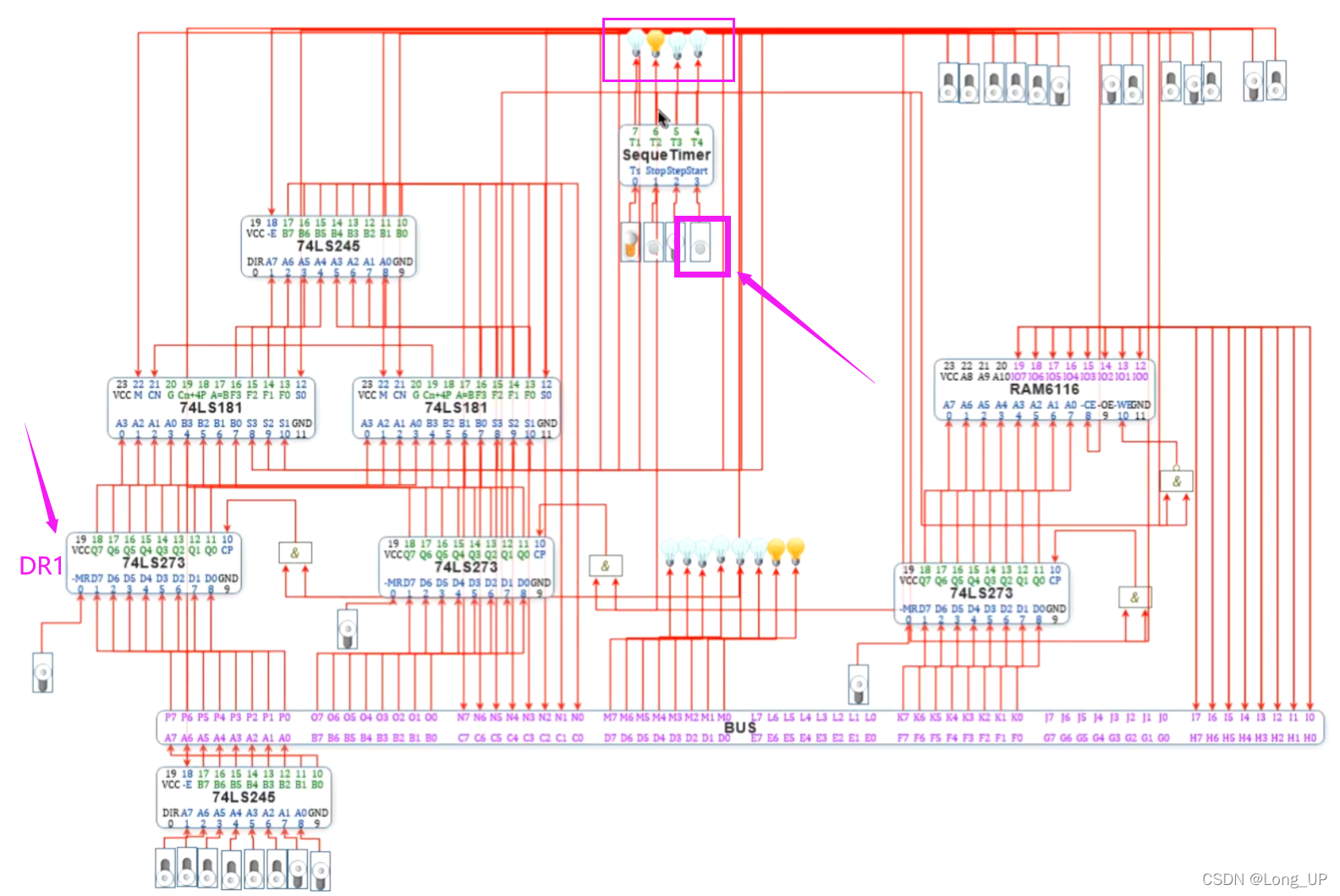

时序发生器用于产生四个等间隔时序信号 T1 、T2 、T3 和 T4 。在本虚拟实验系统中,连续发出的一轮 T1 ~ T4 时序信号对应一个 CPU 周期。图 1 为时序发生器的简单电路连接图,其中,Ts 为时钟源输入信号,Stop 为停止信号,Start 为开始信号,Step 为单步运行信号。在 Step=0 时,单击 Start 连接的单脉冲按钮,时序信号 T1~T4 会周而复始地发送出去,时序发生器处于连续运行状态,若此时单击 Stop 按钮,发送完此周期时序信号后就会停机。在 Step=1 时,处于单步运行状态,即每发送完一个CPU周期时序信号就自动停机。本实验使用单步运行方式。

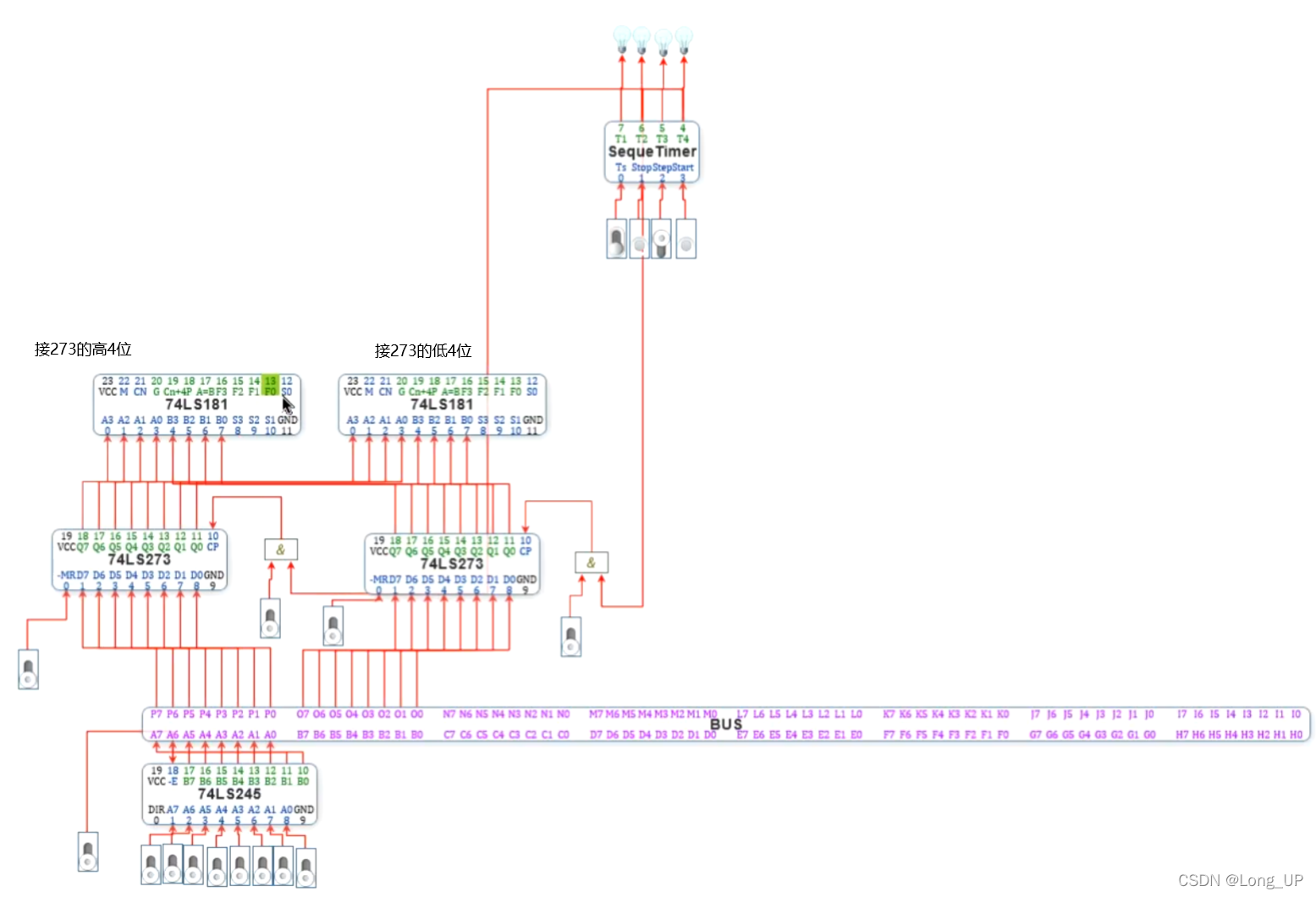

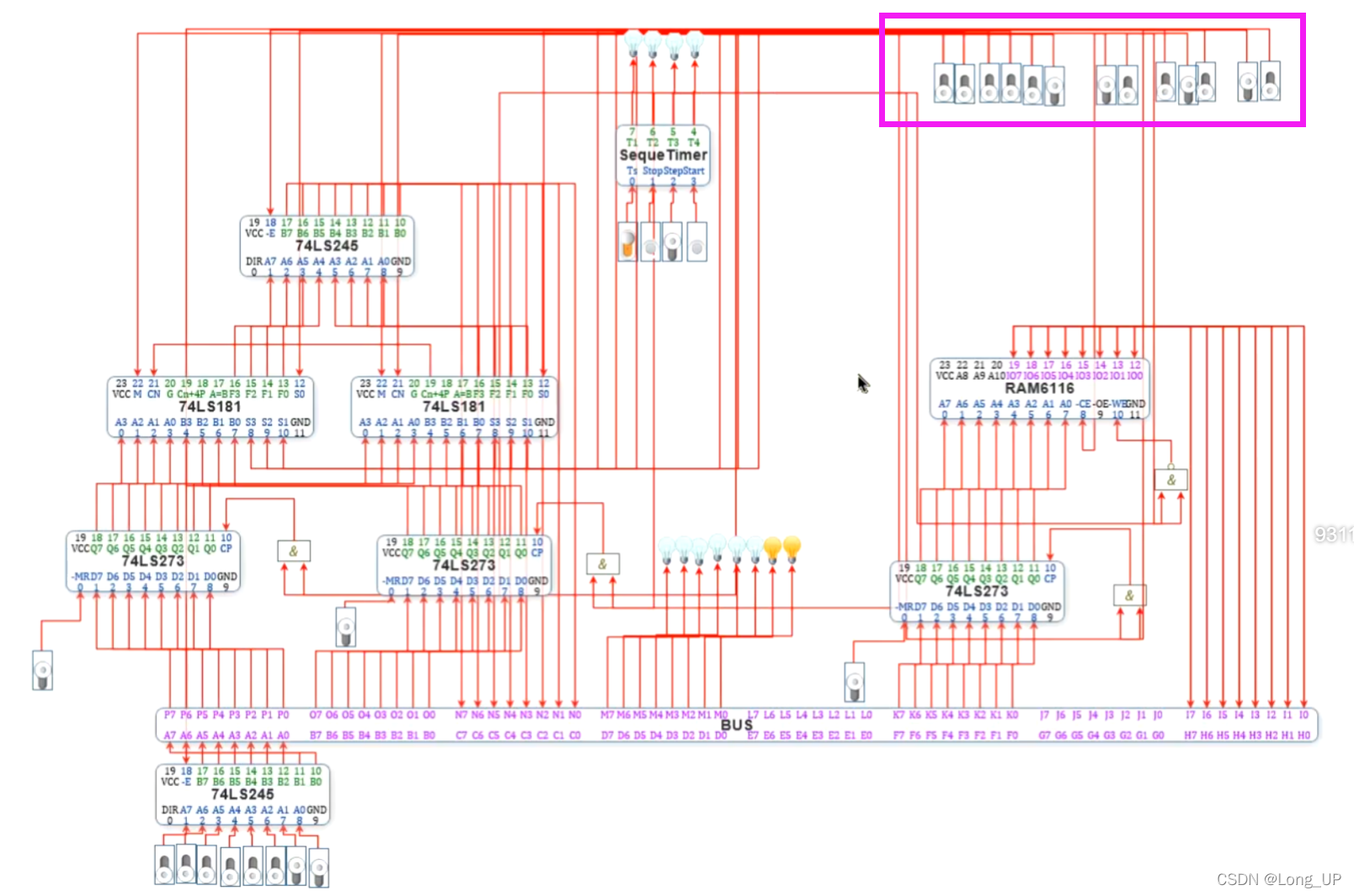

图 2 为本实验数据通路总框图,其中 ALU 由 2 片 74LS181 构成,DRI 、DR2 和 AR 均为一片 74LS273 , RAM 为一片 6116 芯片,△ 表示三态门 74LS245 。时序发生器为虚拟实验系统提供的虚拟组件。

实验电路中涉及的其他控制信号如下:

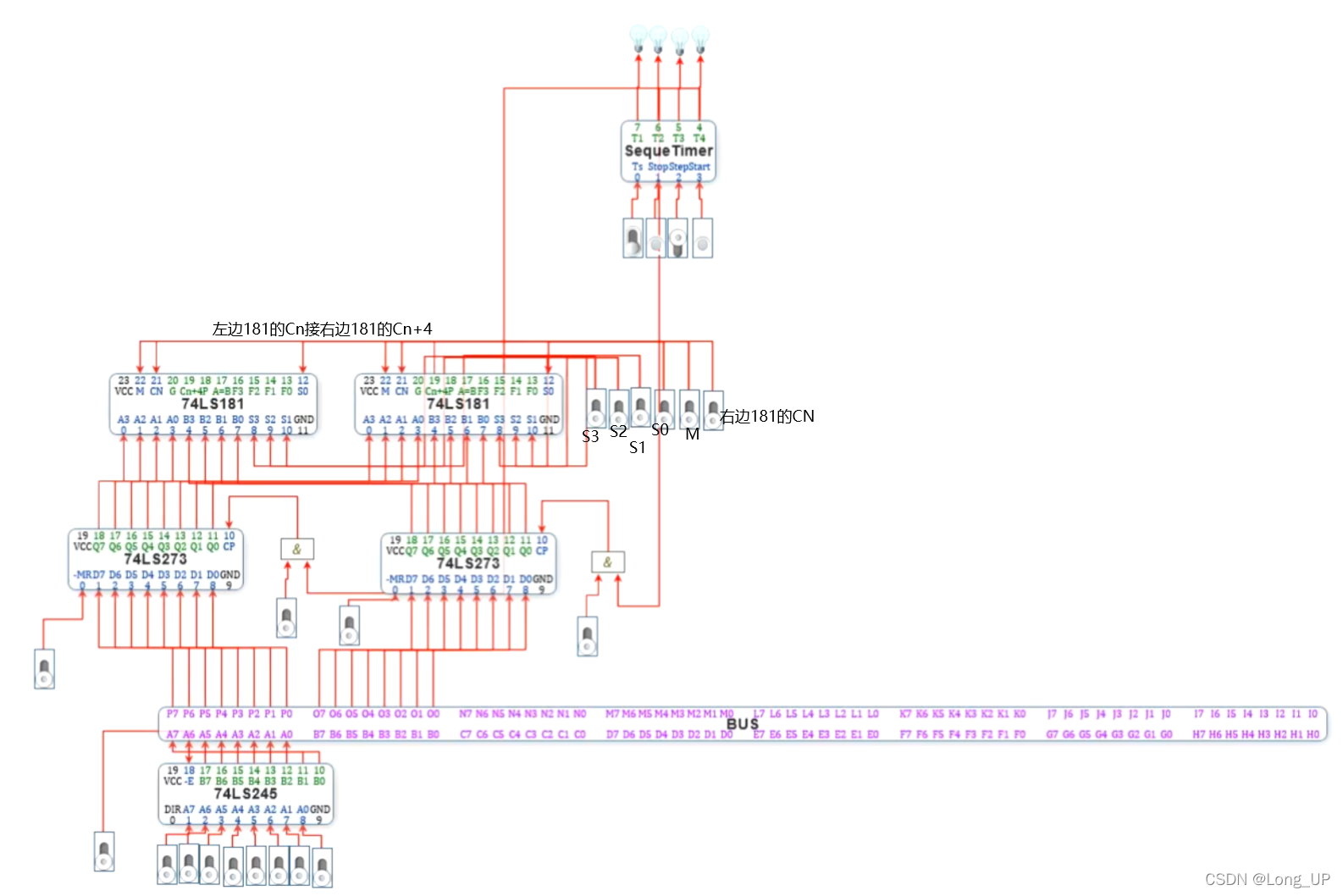

- M:选择 ALU 的运算模式 ( M=0,算术运算;M=1,逻辑运算 )。

- S3, S2, S1, S0:选择 ALU 的运算类型。如 M=0 时,设为 1001 表示加法运算。

- Cn :向 ALU 最低位输入的进位信号, Cn=0 时有进位输入, Cn=1时无进位输入。

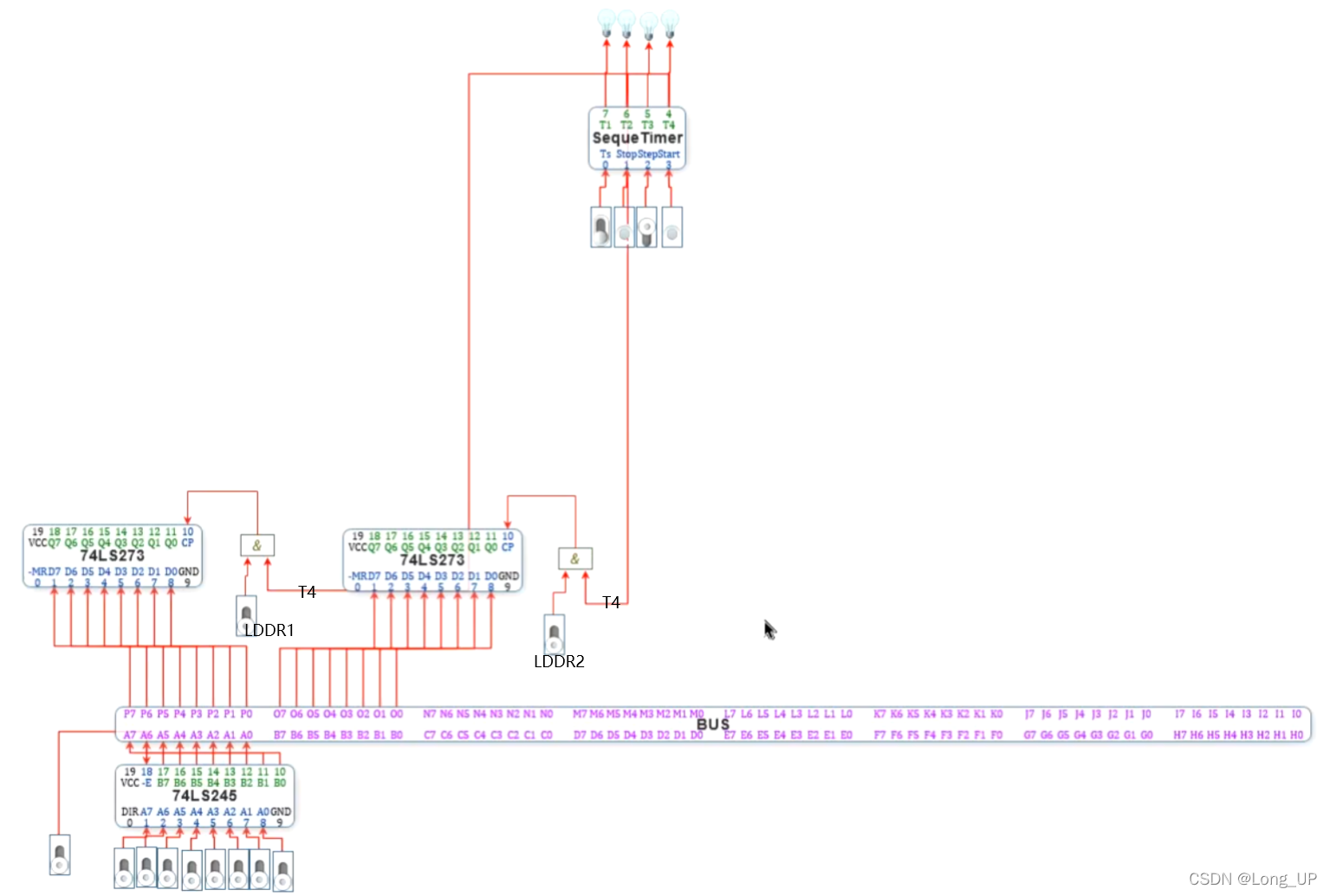

- LDDR1:DR1 的数据加载信号,与 T4 脉冲配合将总线上的数据打入 DR1 中。LDDR1 和 T4 通过与门进行与运算之后连接到74LS273芯片的CP引脚,当 LDDR1=1 时在 T4 的上升沿将数据锁存到 DR1 。

- LDDR2:DR2 的数据加载信号,与 T4 脉冲配合将总线上的数据打入 DR2 中。LDDR2 和 T4 通过与门进行与运算之后连接到 74LS273 芯片的 CP 引脚,当 LDDR2=1 时在 T4 的上升 沿将数据锁存到 DR2 。

- MR:芯片7 4LS273 的清零信号,低电平有效。本实验恒置为 1 。

- ALU-BUS:ALU输出三态门使能信号,为 0 时将 ALU 运算结果输出到总线。

- SW-BUS:开关输出三态门使能信号,为 0 时将 SW7 ~ SW0 数据发送到总线。

- SW-BS:6116 片选信号。为 0 时 6116 正常工作。

- OE:存储器读信号。 CE=0 , OE=0 时为读操作,实验中将其接地,恒置为 0。

- WE:存储器写信号,与 T3 脉冲配合实现存储器写操作 ,WE 与 T3 通过与非门进行与非运算之后连接到 6116 芯片的 WE 引脚, WE 引脚低电平有效。在 CE=0、 OE=0 的条件,与 WE=1,T3=1 时进行行写操作,否则进行读操作。

- LDAR:AR 的地址加载信号,与 T3 脉冲配合将总线上的地址打入到 AR 中,LDAR 和 T3 通过与门进行与运算之后连接到 74LS273 芯片的 CP 引脚,当 LDAR=1 时在 T3 的上升沿将地址锁存到 AR。

实验原理

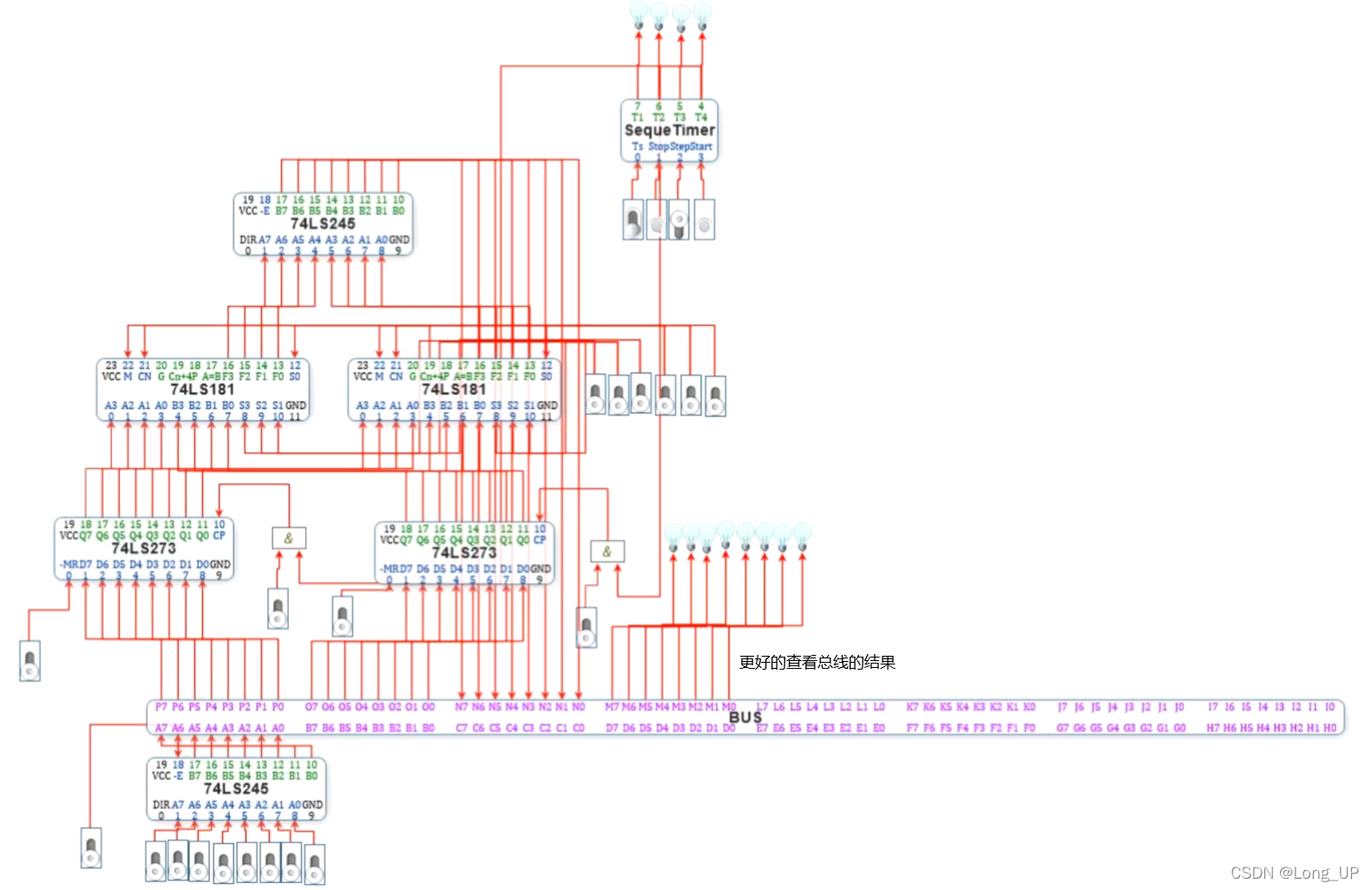

实路所用数据通路如图 2 所示,数据开关、数据显示灯、运算器、存储器通过总线相连,数据开关 (SW7~ SW0) 用于设置数据或地址,数据和地址经三态门发送至总线。DR1 和DR2 从总线上接受数据并传送到ALU进行运算,运算结果经三态门送回至总线。地址寄存器AR从总线上获取地址并送至存储器,存储器按地址进行读写,将读出的数据发送至总线,或者从总线输入数据并写入。数据显示灯与总线相连,流经总线的所有数据和地址都将在数据灯上显示。

计算机控制器通过控制线向执行部件发出各种控制命令,这些控制命令被称为微命令,执行部件接收微命令后所进行的操作,叫作微操作。图 2 中的控制信号线都与控制器相连,并由控制器的相应微命令控制,例如当控制器中表示 SW-BUS 的微命令位设置为0时, 低电平信号通过控制线传送到数据开关的三态门,三态门即执行“打开”微操作。

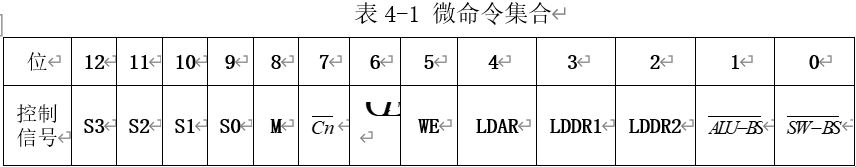

为方便进行实验,将图 2 中所有控制信号归纳在表中。实验的主要任务就是确定这些控制信号在每一个 CPU 周期的取值。

可以设计不同的微命令组合,来实现不同的功能。例如,微命令组合 0000 0110 01010 表 示 DR1 载入,数据开关三态门打开,存储器、DR2 和 ALU 三态门都关闭,其功能即为:将数据开关上的数据送入DR1。注意,表 4-1 里的微命令只是实际计算机中的部分, 计算机话行所需要的微命令远不止这些。

在存储逻辑型控制器中,计算机需要用到的所有微命令组合都已预先设计好并存储在控制存储器中,由控制器根据程序自动找出需要的微命令组合,通过控制线发送给各执行部件执行。其中的每一个微命 令组合又叫一条微指令。本实验用人工设置数据开关的方法来代替控制器生成微命令,完成一系列操作和任务。

实验内容与步骤

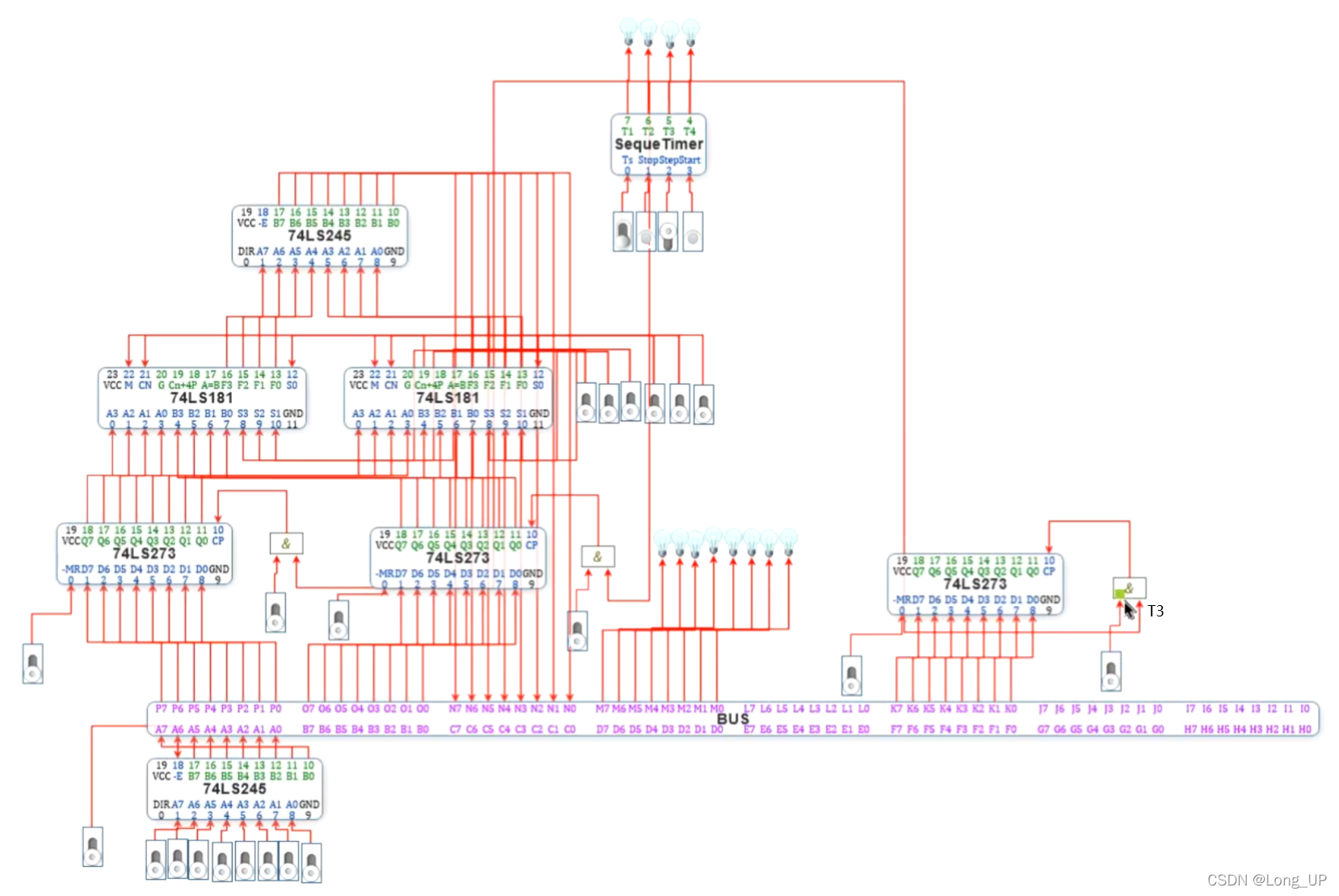

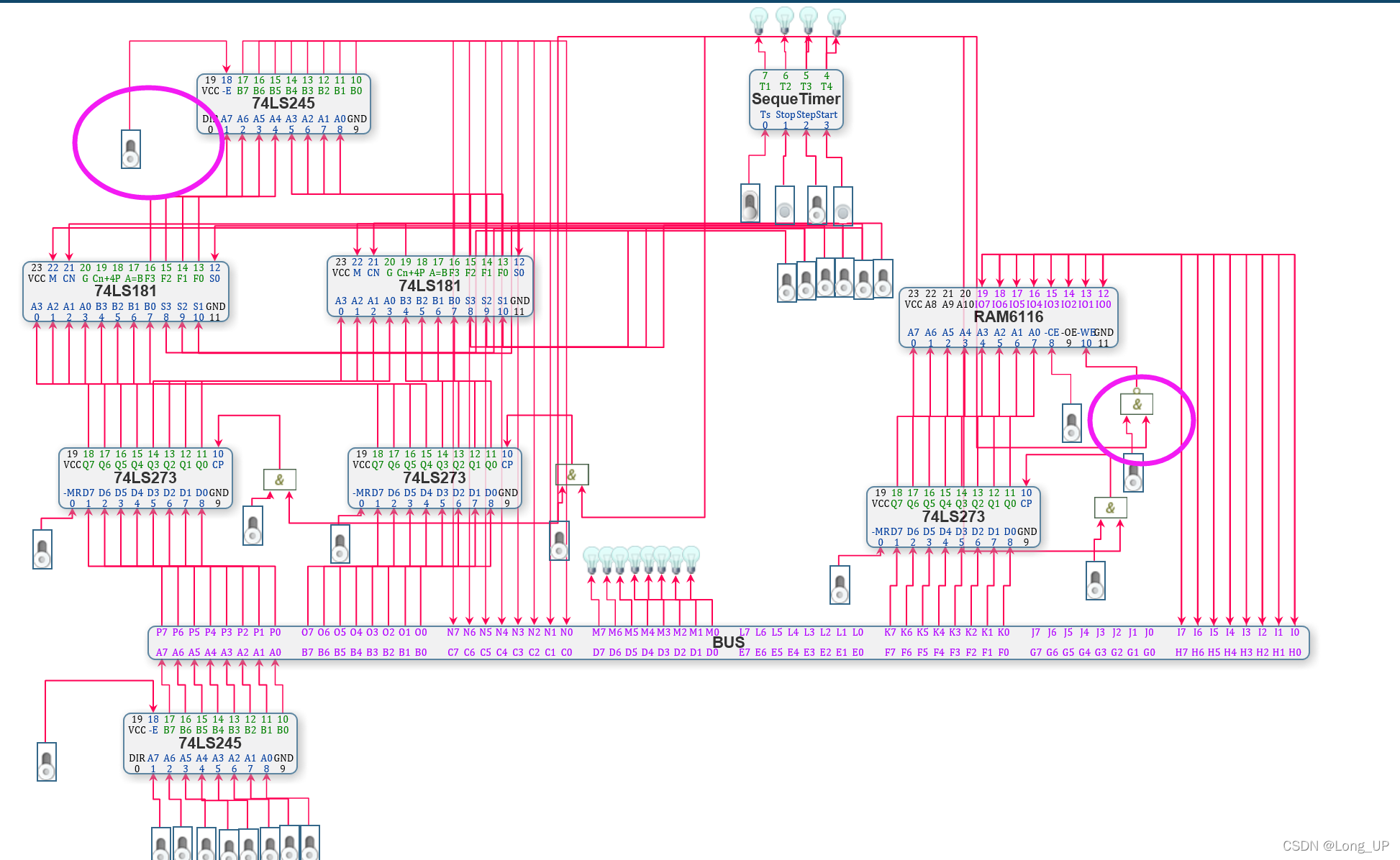

- 运行虚拟实验系统,导入实验电路,接好表 4-1 中列出的控制信号线,将控制线分别接至电路图上方的数据开关上,并仔细检查一遍, 确保连接正确。连接好的电路下图所示。

- 进行电路预设置。将 DR1、 DR2 和 AR 的 置 1,时序发生器的 Step 置1。

- 打开电源开关。

- 求 A+B, A 从数据开关输入,B 是存储器操作数,B 的地址也从数据开关输入,运算结果在数据显示灯上显示。具体步骤如下:

(1) 准备好要使用的微命令,如表 4-2 所示。

(2) 打开电源。

(3) 设置控制信号:数据开关 DR1 ( 0000011001010 );将数据开关设置为 A (00000011) ;单击时序发生器的 Start 按钮。等待一个 CPU 周期后,数据开关上的值已存入 DR1 。

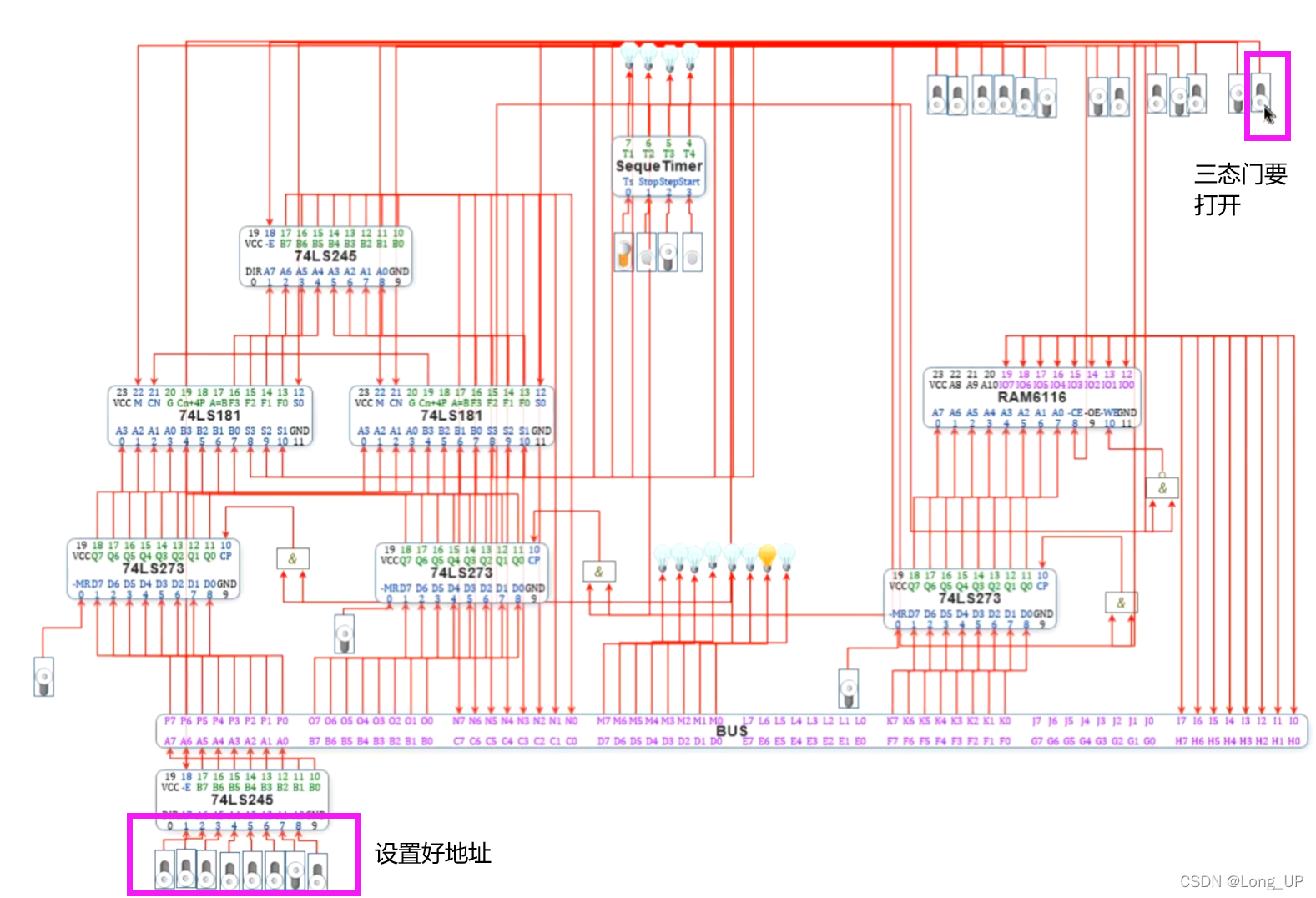

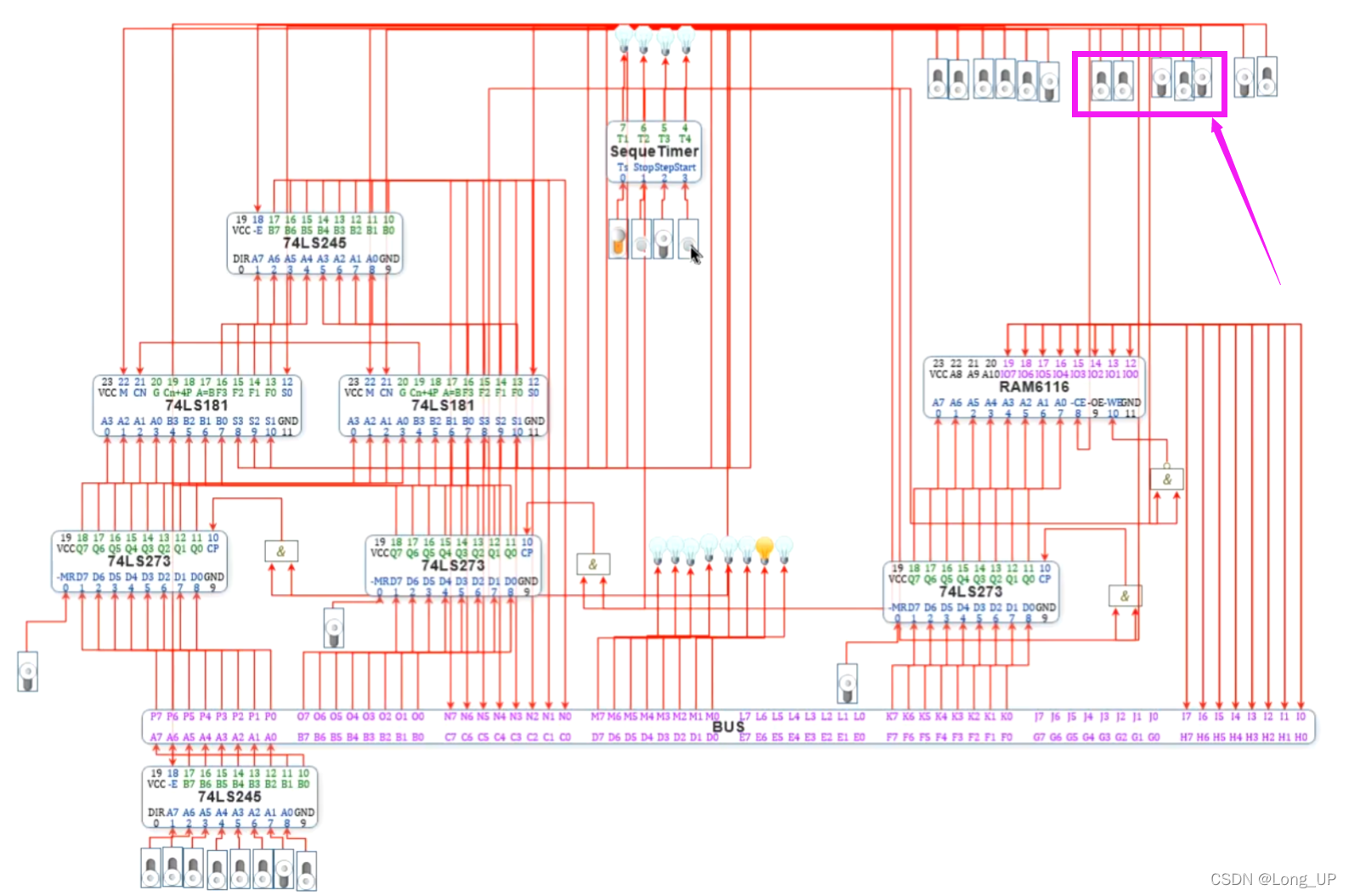

(4)设置控制信号:存储器操作数 DR2 (000010010110);将数据开关设为B的地址(0000010); 单击 Start 按钮。等待一个 CPU 周期后,B 的值已存入 DR2 。

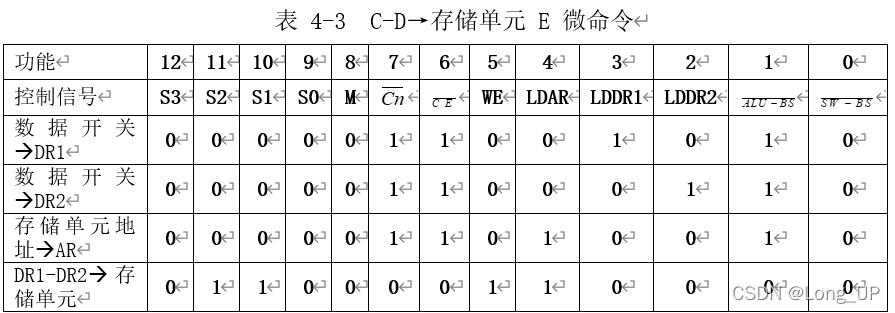

(5)设置控制信号: DR1+DR2 DR1(1001011000001)。运算结果在数据灯上显示。 - 计算 C-D→存储单元 E,数据 C、 D 和地址 E 都从数据开关输入。具体步骤如下:

(1) 设计微命令,填入表 4-3 中:

(2) 设置控制信号:数据开关 → DR1( 0000011001010 );将数据开关设置为 C ( 00010111 );单击时序发生器的 start 按钮。等待一个 CPU 周期后, C 已存入 DR1。

(3) 设置控制信号:数据开关 →DR2( 0000011000110 );将数据开关设置为 D ( 00001000 );单击start 按钮。等待一个 CPU 周期后, D 已存入 DR2。

(4) 设置控制信号:存储单元地址 →AR( 0000011010010 );将数据开关设置为 E ( 00000000 );单击 start 按钮。等待一个 CPU 周期后,地址 E 已存入 AR。

(5) 设置控制信号: DR1-DR2→存储单元( 0110000100001 );单击 start 按钮。等待一个 CPU 周期后,运算结果已存入存储单元 00H。

(6) 单击菜单中的“工具/存储器芯片设置”,查看存储单元 00H 的值是否正确,如果不正确,找到错误的原因,调试至正确为止。 - 计算 F∧G→存储单元 H。 F 和 G 都是存储器操作数, F、 G 的地址以及地址 H 都从数据开关输入。具体步骤如下:

(1) 设计微命令,填入表 4-4 中:

(2) 设置控制信号: 存储器操作数 →DR1( 0000011001010 );单击 start 按钮。等待一个 CPU 周期后, F 已存入 DR1。

(3) 设置控制信号: 存储器操作数 →DR2(0000011000110 );单击 start 按钮。等待一个 CPU 周期后, G 已存入 DR2。

(4) 设置控制信号:存储单元地址 →AR( 0000011010010 );将数据开关设置为 H ( 00001100 );单击 start 按钮。等待一个 CPU 周期后,地址 H 已存入 AR。

(5) 设置控制信号: DR1∧DR2→存储单元( 1011110100001 );单击 start 按钮。等待一个 CPU 周期后,运算结果已存入存储单元 00H。

(6) 单击菜单中的“工具/存储器芯片设置“,查看存储单元 00H 的值是否正确,如果不正确,找到错误的原因,调试至正确为止。

具体连线步骤

注意是 与非门 和不要缺少 ALU-BS

实验验证

电路预设置

打开电源

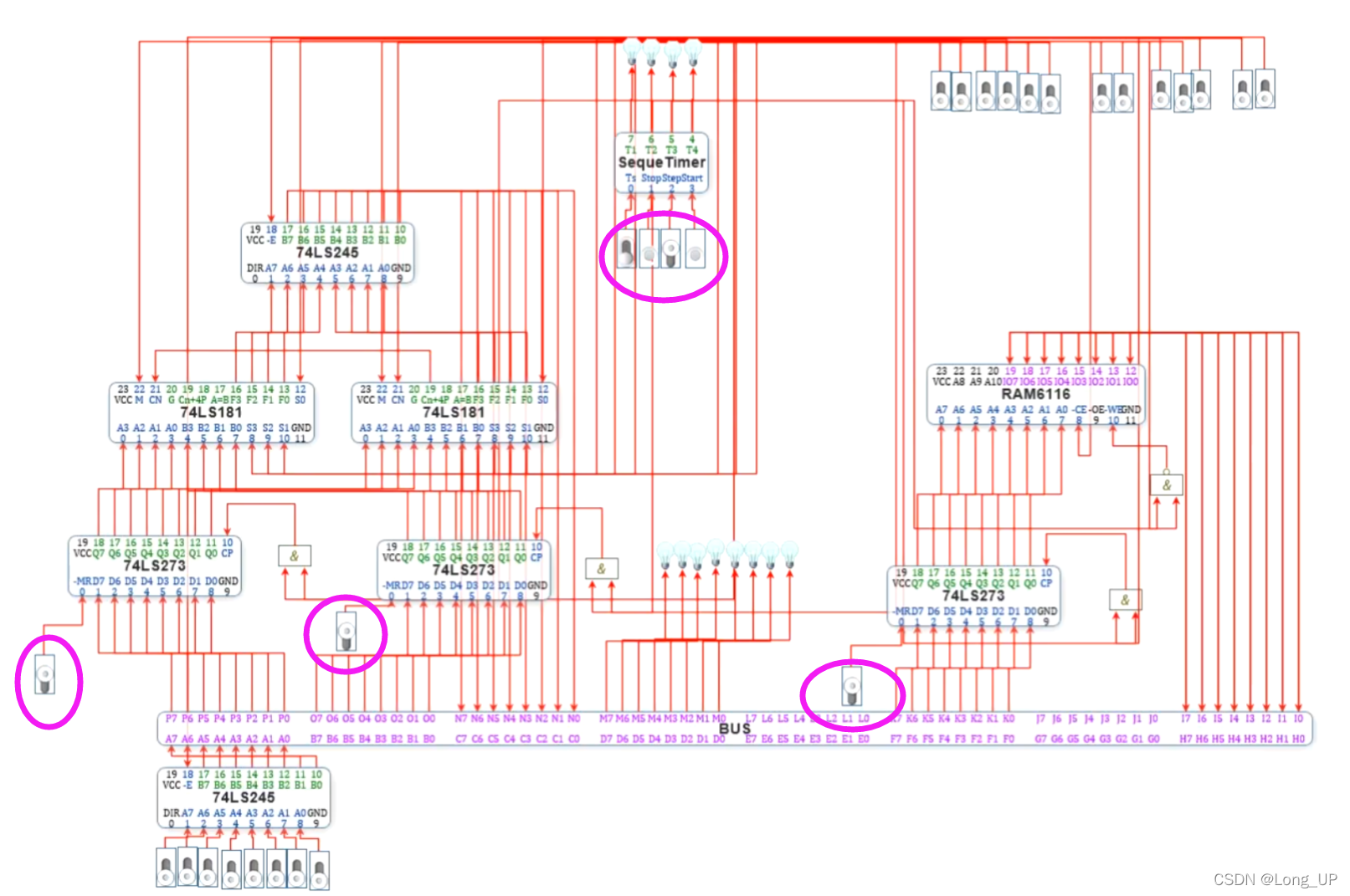

右上角按钮分别对应

S3、 S2、 S1、 S0、 M、 Cn、 CE、 WE、 LDAR、 LDDR1、 LDDR2、 ALU-BS、 SW-BS、

设置微命令

- SW-BS 设置使能端低电平有效

- ALU-BS 设置为高电平无效

- S3 S2 S1 S0 运算器,因为这里没有用到,所以全部设置为无效信号

- S3 S2 S1 S0 高电平有效设置为低电平

- M 高电平有效,设置为低电平

- Cn 低电平有效,设置为高电平,因为用不到控制信号

- CE 片选,低电平有效,设置为高电平

- WE 写,高电平有效,设置为低电平,因为用不到控制信号

- LDAR 地址载入信号,高电平有效,设置为低电平

- LDDR1 数据载入到寄存器1,设置为有效

- LDDR2 数据载入到寄存器1,设置为无效

设置微命令的原则:需要哪个控制信号就设置为有效,其他都为无效

设置控制信号1

数据开关 DR1(0000011001010);将数据开关设置为A (00000011);单击时序发生器的Start按钮,执行微命令。等待一个CPU周期后,会产生T1,T2,T3,T4 的时钟脉冲,在时钟脉冲的配合下,数据开关上的值已存入DR1。

设置控制信号2

设置好地址00000010,打开三态门,把地址送到地址寄存器

让存储器为读,WE为1是写,让WE为0 ,通过总线读到DR2,因为要送到DR2

LDDR2 数据载入到寄存器2,设置为有效

存储器操作数 DR2 (000010010110);将数据开关设为B的地址(00000010); 单击Start按钮。等待一个CPU周期后,B的值已存入DR2。

进行算数运算,DR1+DR2 →DR1(1001011000001)。运算结果在数据灯上显示。

思考与分析

- 总线的功能是什么?连接部件可以分为几类?

- 为什么要设总线判优控制?集中式总线控制有哪几种,各有什么样的特点。