计算机组成原理期末复习总结

冯·诺依曼计算机的特点:

-

五大部件:运算器,存储器,控制器,输入设备,输出设备;

-

机器以运算器为中心(现代的机器以存储器为中心);

现代计算机:

-

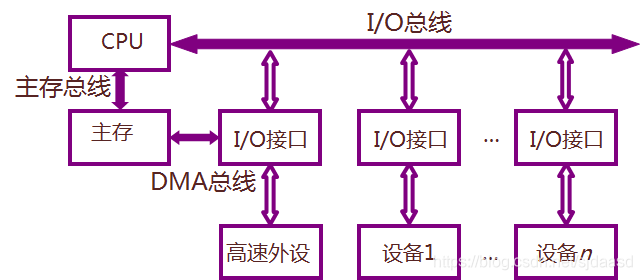

可由三部分组成:CPU,I/O设备及主存储器组成;

-

主机:CPU与主存储器(内存);

-

I/O设备:外部设备(外存,输入设备,输出设备);

ALU(算术逻辑单元)

ACC(累加器)

MAR(存储器地址寄存器)

MDR(存储器数据寄存器)

控制器(PC IR CU)

PC(程序将计数器)存放预执行的指令的地址

IR(指令寄存器) 存放预执行的指令

CU(控制单元)

存储单元:存放一串二进制代码;

存储字:存储单元中二进制代码的组合;

存储字长:存储单元中二进制代码的位数,每个存储单元赋予一个地址号;

中小规模集成电路第三代计算机

单总线结构:

双总线结构:

三总线结构:

总线分类:

-

片内总线

-

系统总线:

-

数据总线;

-

地址总线;

-

控制总线;

- 通信总线;

总线特性:

- 机器特性;

- 电气特性;

- 功能特性;

- 时间特性;

总线复用:地址总线和数据总线共用一组物理线路;

总线标准:ISA,EISA,VESA,PCI,AGP,RS-232C(串行通信总线标准),USB

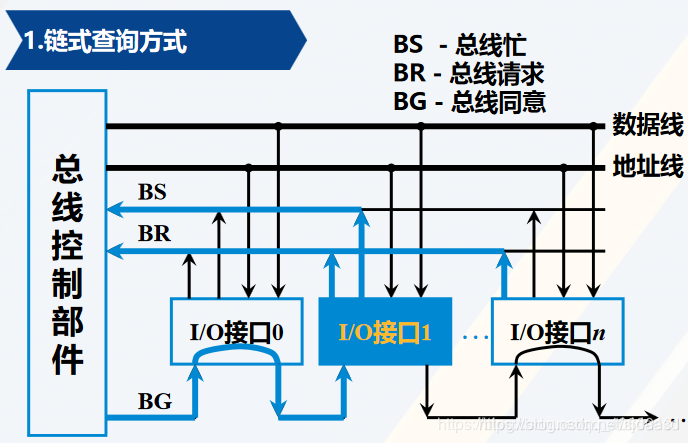

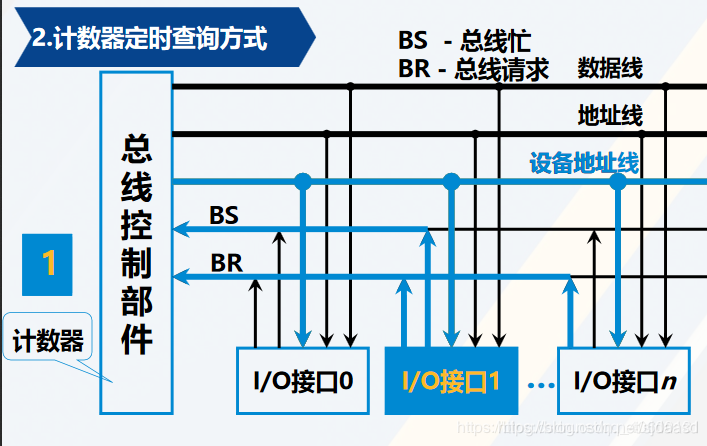

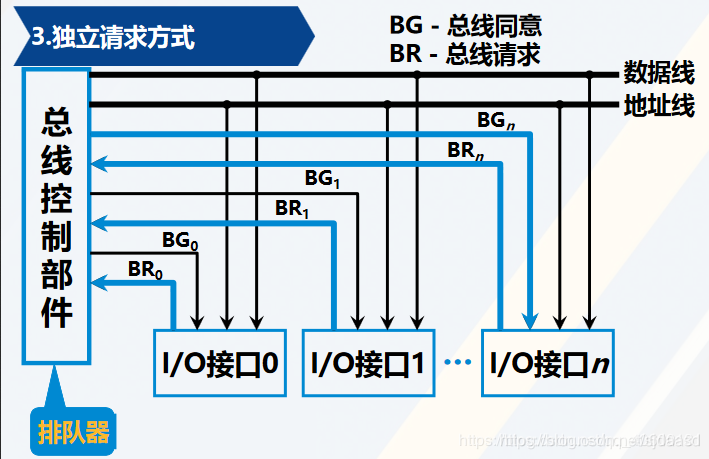

总线判优控制可分为集中式和分布式

链式查询:(电路故障敏感)

计数器定时查询:

独立请求方式:响应速度快

总线周期:

- 申请分配阶段—》寻址阶段----》传数阶段-----》结束阶段

总线通信控制方式:

- 同步通信;

- 异步通信;{

应答方式:不互锁,半互锁,全互锁;

} - 半同步通信;

- 分离式通信;

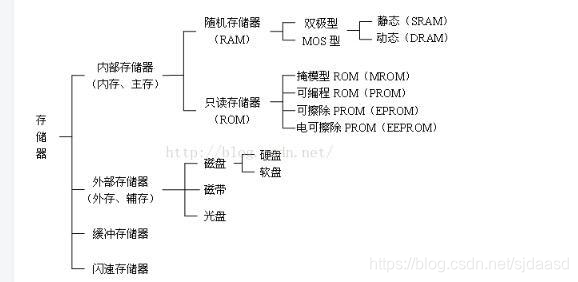

存储器

RAM(随机存储器)

ROM(只读存储器)

地址线是单向输入的;

数据线是双向输入的;

译码驱动方式:线选法和重合法;

再生或刷新: 恢复一次原状态的过程;

动态RAM的刷新:

- 集中刷新;

- 分散刷新;

- 异步刷新;

掩模ROM(用户无法改变原始状态)

PROM(一次性编程的只读存储器)

EPROM(可擦除可编程只读存储器)

书本(计算机组成原理第二版)例题4.1

存储器的校验:

已知接收到的汉明码为0110101(按配偶原则配置),发送的信息是?

| 二进制序号 | 1 2 3 4 5 6 7 |

|---|---|

| 汉明码 | 0 1 1 0 1 0 1 |

p1=1异或3异或5异或7=1

p2=2异或3异或6异或7=1

p4=4异或5异或6异或7=0

p4p2p1=011 ,第011(3)位错误,改正为0100101,发送的信息是:0101;

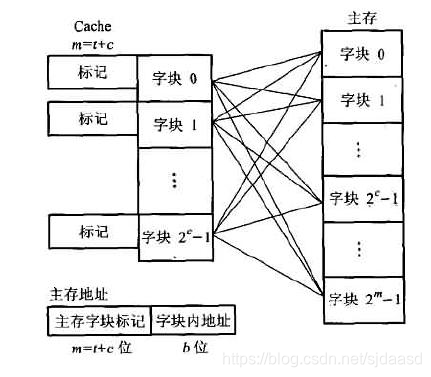

地址映射:

- 直接映射:

- 全相联映射:

- 组相联映射:

通道指令是通道自身的指令;

I/O指令是CPU指令系统的异一部分;

I/O设备编址方式: 统一编址(无专用的I/O指令) 和 不统一编址(专用的I/O指令)

程序查询方式:(踏步等待,CPU和I/O串行工作)

程序中断方式:(没踏步等待,中断现行程序)

DMA方式:

窃取或挪用:CPU总是将总线占有权让给DMA

中断触发器EINT为“1”,触发器可用开中断指令(开中断)

也可用关中断指令或硬件自动复位(关中断)

中断时间: 指令执行阶段的结束时刻

中断处理过程:

中断请求—》中断判优—》中断响应----》中断服务—》中断返回

中断服务程序流程:

-

保护现场

-

中断服务

-

恢复现场

-

中断返回

DMA传送过程:预处理,数据传送,后处理

程序中断方式是靠程序传送的,DMA方式是靠硬件传送;

程序中断方式是在一条指令执行结束时响应,DMA方式是指令周期内任一存取周期结束时响应;

计算机的计算方法:

数值为正数:原码,反码,补码都一样;符号位为“0”

数值为负数:反码为原码的“每位求反”,补码“取反加1”;符号位为“1”

设浮点数字长为16位,其中阶码位5位(含1位阶符),尾数11位(含1位数符);将十进制 +(13)/(128)写成定点数和浮点数,并分别写出它在定点机和浮点机中的机器数形式。

+(13)/(128) = + (13) / ( 2^7) = 0, 0001101

二进制形式: x = 0.0001101000 (尾数11位(含1位数符))

定点数: x=0.0001101000

浮点数规格化: x =0.1101000000x(2^-11) (二进制:-11(-3))

定点机: [x]原=[x]反=[x]补

阶码位5位(含1位阶符)

浮点机中:

[x]原 = 1,0011:0.1101000000

[x]反 = 1,1100:0.1101000000

[x]补 = 1,1101:0.1101000000

已知x=-0.1110,y=-0.1101,求[xy]原*

[x]原=1.1110 x*=0.1110(绝对值) x0=1(符号位)

[y]原=1.1101 y*=0.1101(绝对值) y0=1(符号位)

符号位 x0异或y0 = 0

x* x y* = 0.10110110

[x*y]原 = 0.10110110

========================================================================================================

指令系统

指令是由 操作码 和 数据码 组成的

指令字长 = 操作码的长度 + 操作数地址的长度 + 操作数地址的个数

寄存器的位数可反应机器字长

指令寻址:

数据寻址:

- 立即寻址

- 直接寻址

- 隐含寻址

- 间接寻址

- 寄存器寻址

- 寄存器间接寻址

- 基址寻址

- 变址寻址

- 相对寻址

RISC :精简指令系统计算机

CISC :复杂指令系统计算机

指令周期:

- 取指周期

- 【间址周期】

- 执行周期

- 【中断周期】

中断判优可用硬件实现,或软件实现;

保护程序断点就是要将当前程序计数器PC的内容保存在存储器中;

中断隐指令是硬件自动完成的;

========================================================================================================

设CPU内部采用非总线结构;

(1)取指周期的全部微操作

PC->MAR

1-R

M(MAR)->MDR

MDR->IR

OP(IR)->CU

(PC)+1->PC

(2) 取数指令“LDA M"操作:

Ad(IR) -> MAR

1->R

M(MAR)->MDR

MDR->ACC

(3)存数指令"STA M"操作

Ad(IR)->MAR

1->W

ACC->MDR

MDR->M(MAR)

(3)加法指令"ADD M”操作

Ad(IR)->MAR

1-R

M(MAR)->MDR

(ACC)+(MDR)->ACC

(4) 指令为间接寻址时,需要添加间址周期操作

Ad(IR)->MAR

1-R

M(MAR)->MDR

进入执行周期,3条指令的第一个微操作均为MDR->MAR,其余操作不变;

(5) 无条件转移指令"JMP Y"

Ad(IR) - >PC

结果为零的移指令“BAZ Y"

Z*Ad(IR)->PC***

指令周期 包含若干个 机器周期

机器周期 包含若干个 时钟周期

一条机器指令对应一条微程序

微指令格式:

| 操作控制 | 顺序控制 |

|---|

分为

| 水平型微指令 | 垂直型微指令 |

|---|

========================================================================================================

某微程序控制器中,采用水平型直接控制(编码)方式的微指令格式,后续微指令地址由微指令的下地址字段给出。已知机器共有28个微命令,6个互斥的可判定的外部条件,控制储器的容量为512X40位。设计微指令格式,说明理由;

| 操作控制 | 判断 | 下地址 |

|---|---|---|

| 28位 | 3位 | 9位 |

采用直接编码方式,操作控制字段的位数等于微命令数,为28位;

后续微指令地址由微指令的下地址字段给出,下地址字段的位数可根据存储器容量(512X40位),2^9=512,可定为9位;

6个互斥的可判定的外部条件,可编译 2^3 > 6 ,可以编译成3位状态位;

[参考文档]计算机组成原理第二版