计算机:是现代一种用于高速计算的电子计算机器。进行数值计算和逻辑计算,具有记忆存储功能,按照程序运行,自动,高速处理海量数据的现代智能电子设备

计算机组成:是计算机系统结构的逻辑实现,包括物理机器级内的数据流和控制流的组成以及逻辑设计,它着眼于物理机器级内各事件的排列方式和控制方式,各部件的功能以及各部件的联系

第一章 计算机系统概论

计算机系统:由计算机配以相应的外围设备(如键盘,显示器等)、电源和其他辅助设备,及足够的软件而构成的系统

计算机:以中央处理器为核心,配以内存储器、输入/输出接口电路,通过总线(Bus)结构连接而构成的裸机

中央处理器(CPU):是一块超大规模的集成电路,是计算机的控制中心和运算中心,主要功能是解释计算机指令以及处理计算机软件中的数据

数字计算机的硬件组成

运算器:进行数值和逻辑运算

存储器:保存解题的原始数据和解题步骤

存储单元:保存一个字的单元

地址:在存储器中被分为许多存储单元,每个存储单元的编号为地址

存储容量:存储器中所有存储单元的总数

控制器:是计算机中发号施令的部件,它控制计算机的各个部件有条不紊的进行工作,它的主要任务是从内存中取出解题步骤加以分析,然后执行某种操作

计算机中的CPU由运算器、控制器和cache组成

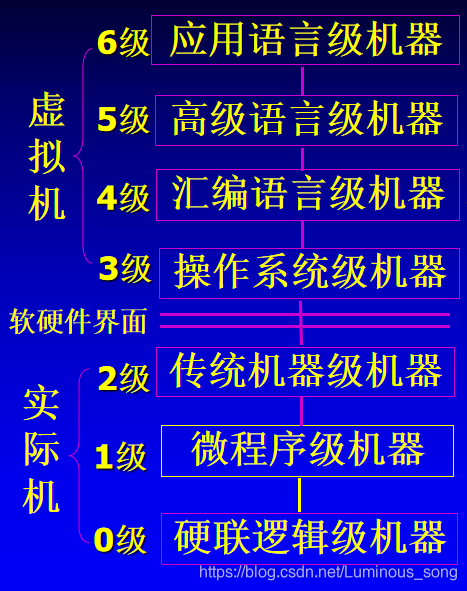

计算机系统的层次结构

分层次认识计算机系统的方法,从机器语言的角度出发,把计算机系统按功能划分成多级层次结构

第二章 运算方法和运算器

真值:是变量本身所具有的真实值,是理想的概念,一般是无法得到的,一般用约定真值或相对真值来代替。在计算机数值表示中,用正负号加绝对值表示数据的形式被称为“真值”

机器数:是将符号数字化的数,是数字在计算机中的二进制表示形式

机器码:是将硬件序列号经过一系列加密、散列形成的一串序列号。是根据电脑的硬件(主板)信息经过一定公式运算而自动生成的一组数字

数据与文字的表示方法

机器数的特点:符号数字化,其数的大小受机器字长的限制

带符号位的机器数对应的值成为机器数的真值

进制转换

- 非十进制数转为十进制:按权展开再相加

- 十进制转换为其他进制:整数除基取余,小数部分乘基取整

数据格式

- 定点表示法

- 浮点表示法

尾数:用定点小数表示,给出有效数字的位数决定了浮点数的精度

阶码:用整数形式表示,指明小数点在数据中的位置,决定了浮点数的表示范围

IEEE754标准:32位浮点数的标准格式为

S:浮点数的符号位,1位,0表示整数,1表示负数

M:尾数,23位,用小数表示,小数点放在尾数域的最前面

E:阶码,8位,采用移码的方式表示,浮点数指数真值e = E -127

x=(-1)s×(1.M)×2E-127

e=E-127 (2.5)

IEEE754标准:64位浮点数的标准格式为

S:符号位,1位

E:阶码,11位

M:尾数,52位

机器零:当浮点数的尾数为0,不论其阶码为何值,或者当阶码的值遇到比它能表示的最小值还小时,不管其尾数为何值,计算机都把该浮点数看出零值

正零:阶码全为0且尾数也全为0时,表示的真值x为0,符号位也为0

负零:阶码全为0且尾数也全为0是,符号位为1

正无穷大:阶码全为1,尾数为0,符号位为0

负无穷大:阶码全为1,尾数为0,符号位为1

在32位浮点数表示中,要除去E全用0和全1表示零和无穷大的特殊情况,所以指数的偏移值不选128,而选127,

对于规格化浮点数,E的范围为1到254,真正的指数e的范围在-126到127.因此32位浮点数表示的绝对值的范围是10(-38)到1038

数的机器码表示

在数的机器码表示中,通常有原码,反码,补码和移码

原码:有正零和负零

补码:0的补码只有一种形式,原码除符号位其他取反+1

反码:原码除符号位其他取反

移码:一般是补码符号位取反

字符的表示方法

国际上通用的七位ASCII码,一共128个元素

定点加法减法运算

补码加减法:在模2n+1意义下,任意两个数的补码之和等于该两数之和的补码,这以为着,补码运算符号位也参与,同时高于n+1的位要丢掉

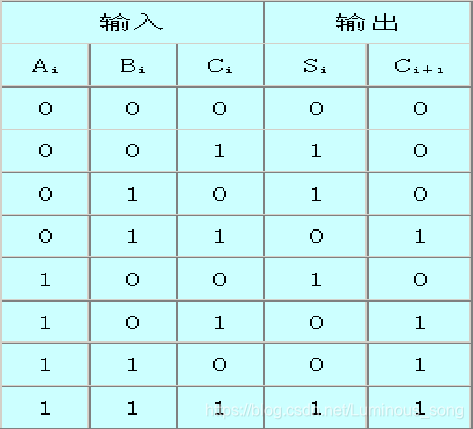

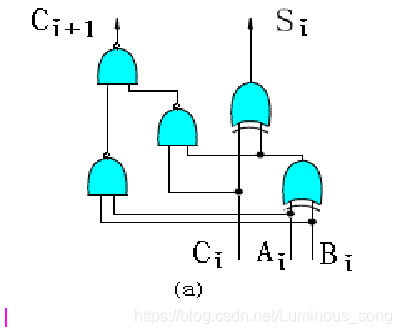

全加器

考虑底位进位和向高位的进位

内部总线

按总线的位置分为:内部总线(CPU内各部件的连线)和外部总线(系统总线)

按总线的逻辑结构分为:单向传送总线和双向传送总线

浮点运算

- 0操作数检查

- 比较阶码大小并完成对阶(小阶向大阶对齐)

- 尾数求和

- 结果规格化

- 舍入操作

- 溢出处理

第三章 多层次的存储器

存储器概述

主存储器的技术指标

处理机字:运算器中一次运算,能够完成的二进制数

处理机字长:运算器中一次运算,能够完成的二进制数的长度

字存储单元:存放一个机器字的存储单元,相应的单元地址称为字地址

字节存储单元:存放一个字节的存储单元,相应的地址称为字节地址

存储容量:指一个存储器中可以容纳的存储单元总数。存储容量越大,能存储的信息越多

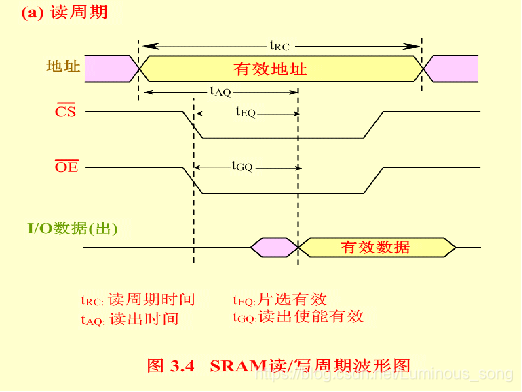

存取时间:指一个读操作从发出到该操作完成,将数据读取到数据总线上所经历的时间,通常取写操作时间等于读操作时间

存储时间:指连续启动两次读操作所需间隔的最小时间,存储时间略大于存取时间

存储器带宽:单位时间里存储器所存取的信息量,通常以位/秒或字节/秒做度量单位

SRAM

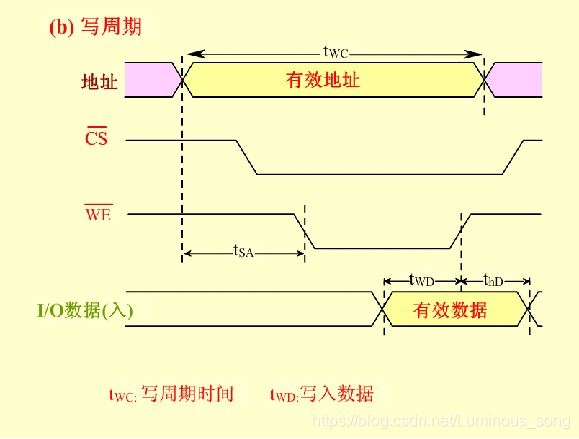

读、写周期波形图

存储器容量的扩充

并行存储器

由于CPU和存储器的速度不匹配,CPU的速度越来越快,而存储器的速度还是比较慢,为了提高存储器的读写毒素,采用不同的组织方法来提高主存与CPU之间的数据交换速度

提高CPU和主存之间的数据交换速度:

- 采用更高的存储器或加长存储器字长

- 采用并行操作的双端口存储器

- 采用cache

- 采用交叉存储器

为了提高主存和CPU之间的数据传输率,除了主存采用更高速的技术来缩短读出时间外,还可以采用并行技术的存储器

双端口存储器

双端口存储器是指一个存储器具有两组相互独立的读写控制线路,是一种高效工作的存储器

交叉存储器

交叉存储器实质上是一种多模块存储器,它用资源重复的方式执行多个独立的读写操作

程度访存的局部性原理(按层次构成存储器体系的主要依据)

由于程序在运行过程中,大部分是可放在容量较大,速度较慢,成本较低的慢速存储部件中,只需将其中一小部分(10%-20%)存放在高速的存储部件中,这便是虚存,cache高速缓存得以实现的具体根据

Cache

高速缓冲存储器技术是利用程序访存的局部性原理,将程序正在使用的部分存放在一个小容量的高速cache中,使得CPU大部分访存操作针对cache进行,从而解决高速CPU与低俗主存之间速度不匹配的问题,使程序的执行速度大大提高

cache是介于CPU和主存之间的小容量存储器