写在前面

内容与https://blog.csdn.net/qq_46640863/article/details/124998142

完全一致。但本文不是手写版本。

第一章

1.某计算机主频4MHz,各类指令平均执行时间和使用频度如下表所示。则该机MIPS为 0.5 ‾ \underline{0.5} 0.5,CPI为 8 ‾ \underline{8} 8

指令类型 存取 加减、比较、转移 乘除 其他 平均执行时间 1.0 μ s 0.5 μ s 10 μ s 2.5 μ s 使用频度 30 % 40 % 10 % 20 % \begin{array}{c|c|c|c|c} 指令类型&存取&加减、比较、转移&乘除&其他\\\hline 平均执行时间&1.0\mu s&0.5\mu s&10\mu s&2.5\mu s\\\hline 使用频度&30\%&40\%&10\%&20\% \end{array} 指令类型平均执行时间使用频度存取1.0μs30%加减、比较、转移0.5μs40%乘除10μs10%其他2.5μs20%

单条指令总平均时间: 1.0 ∗ 30 % + 0.5 ∗ 40 % + 10 ∗ 10 % + 2.5 ∗ 20 % = 2 μ s 1.0*30\%+0.5*40\%+10*10\%+2.5*20\%=2\mu s 1.0∗30%+0.5∗40%+10∗10%+2.5∗20%=2μs

M I P S = 指令数 时间 = 1 ( 一条指令 ) 2 × 1 0 − 6 × 1 0 6 = 0.5 C P I = 主频 M I P S ∗ 1 0 6 = 4 ∗ 1 0 6 0.5 ∗ 1 0 6 = 8 MIPS=\frac{指令数}{时间}=\frac{1(一条指令)}{2\times 10^{-6}\times 10^6}=0.5\\ CPI=\frac{主频}{MIPS*10^6}=\frac{4*10^6}{0.5*10^6}=8 MIPS=时间指令数=2×10−6×1061(一条指令)=0.5CPI=MIPS∗106主频=0.5∗1064∗106=8

2.假定计算机 M 1 M_1 M1和 M 2 M_2 M2具有相同指令体系结构,主频分别为1.5GHz和1.2GHz,在 M 1 M_1 M1和 M 2 M_2 M2上运行程序P,平均CPI分别是2和1,则程序1和2的运行时间比

1 1.5 G H z × 2 1 1.2 G H z × 1 = 8 5 \frac{\frac{1}{1.5GHz}\times 2}{\frac{1}{1.2GHz}\times 1}=\frac{8}{5} 1.2GHz1×11.5GHz1×2=58

3.冯诺依曼计算机体系结构的基本思想?核心思想?

(1)采用二进制;(2)程序存储,把指令存放在存储器,指令控制计算机。(核心思想);(3)由运算器、存储器、控制器、输入、输出五大部件组成。

第二章

1.设某机器数为10001000,分别写出其为原码、反码、补码对应的十进制数。

原码:-8

反码:对应原码1111 0111,真值-119

补码:对应原码1111 1000,真值-120

2.有如下C语言语句

short s=-32767;

unsigned us=s;

执行上述语句后,us值是多少?

s原码:1111 1111 1111 1111

s补码:1000 0000 0000 0001(根据-32768的补码为1000 0000 0000 0000推导)

us=s,us原码=s补码=1000 0000 0000 0001

us=32769

3.float数据采用IEEE 754单精度表示,假定两个float X、Y存放在32位寄存器 F 1 F_1 F1, F 2 F_2 F2中, F 1 F_1 F1=CC90 0000H, F 2 F_2 F2=B0C0 0000H,则X,Y的大小关系是什么?

F 1 = C C 90 0000 H = 1 100 1100 1 ‾ 001 0000 0000 0000 0000 0000 ‾ F_1=CC90\ 0000H=1\underline{100\ 1100\ 1}\overline{001\ 0000\ 0000\ 0000\ 0000\ 0000} F1=CC90 0000H=1100 1100 1001 0000 0000 0000 0000 0000

则符号为1,阶码(偏置127)为153,数值位为1.001

F 1 = ( 1.001 ) 2 × 2 26 = − 9 8 × 2 26 F_1=(1.001)_2\times 2^{26}=-\frac 98\times 2^{26} F1=(1.001)2×226=−89×226

F 2 = B 0 C 0 0000 H = 1 011 0000 1 ‾ 100 0000 0000 0000 0000 0000 ‾ F_2=B0C0\ 0000H=1\underline{011\ 0000\ 1}\overline{100\ 0000\ 0000\ 0000\ 0000\ 0000} F2=B0C0 0000H=1011 0000 1100 0000 0000 0000 0000 0000

则符号为1,阶码(偏置127)为97,数值位为1.1

F 2 = ( 1.1 ) 2 × 2 − 30 = − 3 2 − 30 F_2=(1.1)_2\times 2^{-30}=-\frac 32^{-30} F2=(1.1)2×2−30=−23−30

F 1 < F 2 F_1<F_2 F1<F2

4.写出-5的IEEE 754浮点数编码

5 = ( 101 ) 2 = 1.01 × 1 0 ( 10 ) 2 5=(101)_2=1.01\times 10^{(10)_2} 5=(101)2=1.01×10(10)2

符号位:1

阶码偏置位:2+127=129=1000 0001

1 100 0000 1 ‾ 010 0000 0000 0000 0000 0000 ‾ 1\underline{100\ 0000\ 1}\overline{010\ 0000\ 0000\ 0000\ 0000\ 0000} 1100 0000 1010 0000 0000 0000 0000 0000

C0A0 0000

5.将 67 128 \frac{67}{128} 12867用浮点数表示

128有7位,所以可以用7位小数表示。

( 67 ) 10 = ( 0100 0011 ) 2 (67)_{10}=(0100\ 0011)_2 (67)10=(0100 0011)2

( 67 128 ) 10 = 0.100011 = 1.000011 × 1 0 − 1 (\frac{67}{128})_{10}=0.100011=1.000011\times 10^{-1} (12867)10=0.100011=1.000011×10−1

0 011 1111 0 ‾ 000 0110 0000 0000 0000 0000 ‾ 0\underline{011\ 1111\ 0}\overline{000\ 0110\ 0000\ 0000\ 0000\ 0000} 0011 1111 0000 0110 0000 0000 0000 0000

3F06 0000

第三章

1.设机器字长8位(含一位符号位),用补码加减计算 [ X − Y ] 补 [X-Y]_补 [X−Y]补,将结果还原为真值,并说明PSW中的SF,OF,ZF,CF分别是什么。其中,X=-65,Y=78

X = X n − 1 . . . X 0 Y = Y n − 1 . . . Y 0 S = X o p Y = S n S n − 1 . . . S 0 X=X_{n-1}...X_0\\Y=Y_{n-1}...Y_0\\S=X\ \mathrm{op}\ Y=S_nS_{n-1}...S_0 X=Xn−1...X0Y=Yn−1...Y0S=X op Y=SnSn−1...S0

O F OF OF用于判断补码溢出,需要双符号位判断

C F = S n CF=S_n CF=Sn;

S F = S n − 1 SF=S_{n-1} SF=Sn−1

Z F = S n − 1 + S . . . + S 0 ‾ ZF=\overline{S_{n-1}+S_{...}+S_0} ZF=Sn−1+S...+S0

则 X = ( − 65 ) 10 = 1011 1111 X=(-65)_{10}=1011\ 1111 X=(−65)10=1011 1111; Y = ( 78 ) 10 = 0100 1110 Y=(78)_{10}=0100\ 1110 Y=(78)10=0100 1110

− Y 补 -Y_{补} −Y补为 Y Y Y连同符号位一起变反+1=1011 0010

[ X ] 补 + [ − Y ] 补 = 1011 1111 + 1011 0010 = 1 0111 0001 [X]_补+[-Y]_补=1011\ 1111+1011\ 0010=1\ 0111\ 0001 [X]补+[−Y]补=1011 1111+1011 0010=1 0111 0001

所以,CF=1,SF=0,ZF=0.

将0111 0001还原为真值113

OF:双符号位判断。双符号位运算结果不看最高位,只看第2/3位。

X = 1 10111 1111 X=1\ 10111\ 1111 X=1 10111 1111

− Y = 1 1011 0010 -Y=1\ 1011\ 0010 −Y=1 1011 0010

X − Y = 1 1 0 ‾ 111 0001 X-Y=1\underline{1\ 0}111\ 0001 X−Y=11 0111 0001

发生了负溢出,则OF=1

2.设浮点数字长12位,阶码4位(阶符2位),尾数8位(尾符2位),机器数形式自定(可以定位阶码在前,尾数在后),按浮点数加减求 [ X + Y ] 浮 [X+Y]_浮 [X+Y]浮, X = 0.110101 × 2 − 01 , Y = − 0.100101 × 2 + 01 X=0.110101\times 2^{-01},Y=-0.100101\times 2^{+01} X=0.110101×2−01,Y=−0.100101×2+01

X = 0.110101 × 2 − 01 Y = − 0.100101 × 2 + 01 X=0.110101\times 2^{-01}\\Y=-0.100101\times 2^{+01} X=0.110101×2−01Y=−0.100101×2+01

对阶:(01)-(-01)=2,X右移2位变成 X = 0.001101 × 2 01 X=0.001101\times 2^{01} X=0.001101×201

0.0000 1101+0.1110 0101=0.1111 0010

0.1111 0010 × 2 0001 0.1111\ 0010\times 2^{0001} 0.1111 0010×20001

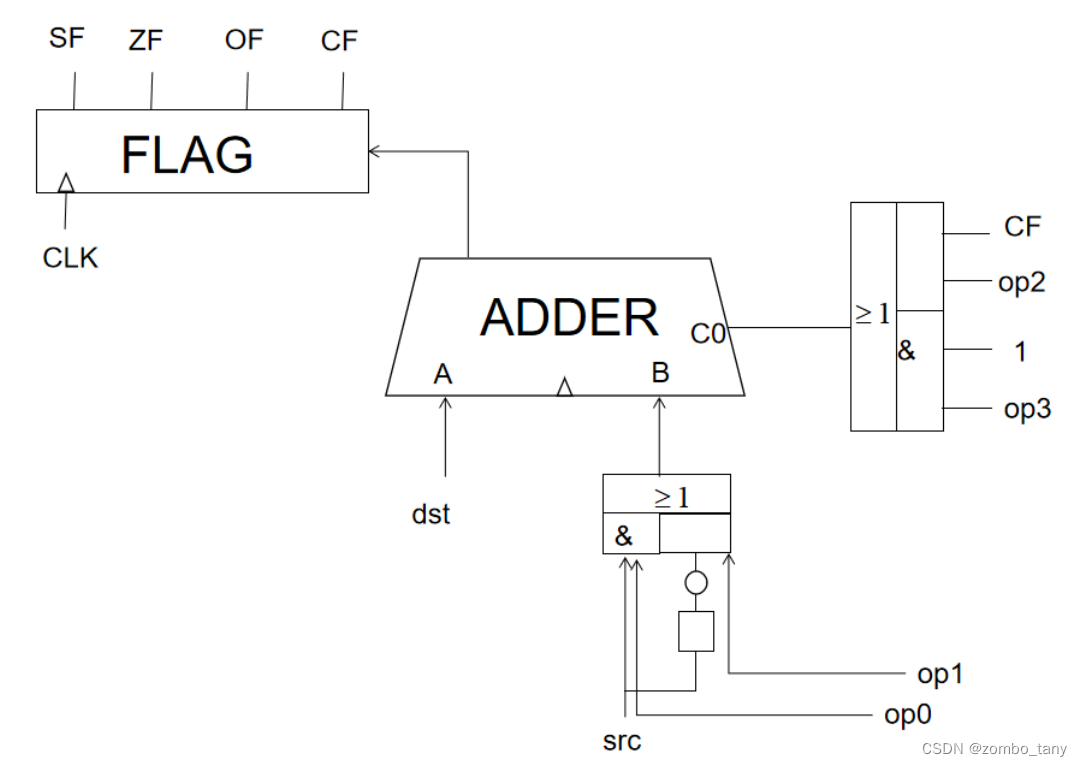

3.某字长8位加减运算电路如图

(1)假设dst=86H,src=F6H,控制op0~op3进行减法,F=? FLAG=?

o p 3 ∼ 0 = 1010 op_{3\sim0}=1010 op3∼0=1010

dst=1000 0110,src=1111 0110

F=dst-src=0 1001 0000

CF=0,SF=1,ZF=0,双符号计算得01 1001 0000,OF=0

(2)如果上述两运算数是无符号数,十进制值是多少?根据什么判断溢出?是否溢出?

144 CF判断溢出,溢出。(无符号减法中CF=0为溢出,CF=1为不溢出)

(3)如果两运算数是有符号数,十进制值是多少?怎么判断是否溢出?

-112 OF 不溢出

4.假定一个8位字长计算机运行如下C程序段

unsigned int x = 134;

unsigned int y = 246;

int m = x;

int n = y;

unsigned int z1 = x-y;

unsigned int z2 = x+y;

int k1 = m-n;

int k2 = m+n;

假设编译器将 R 1 ∼ R 8 R_1\sim R_8 R1∼R8分配给x,y,m,n,z1,z2,k1,k2

(1)执行上述程序段后, R 1 , R 5 , R 6 R_1,R_5,R_6 R1,R5,R6的内容分别是?

R 1 = X = 1000 0110 = 86 H R_1=X=1000\ 0110=86H R1=X=1000 0110=86H

y=1111 0110, ( − y 补 ) (-y_补) (−y补)=0000 1010, R 5 R_5 R5=x-y=1001 0000=90H, R 6 R_6 R6=x+y=0111 1100=7CH

(2)m和k1的值分别是?

m=x= ( 1000 0110 ) 补 (1000\ 0110)_补 (1000 0110)补=-122

k1=m-n= ( 1001 0000 ) 补 (1001\ 0000)_补 (1001 0000)补=-112

(3)上述程序段涉及带符号整数加减、无符号整数加减,能否用同一种加法器及辅助电路?

能

(4)计算机内部如何判断带符号整数加减是否溢出?哪些带符号数执行结果溢出?

OF状态,k2溢出。

第五章

1.设有一个具有14位地址和8位数据的存储器

(1)该存储器容量是多少?

(2)如果该存储器用1K*1的存储芯片构成,需要多少片?

(3)需要用哪几位地址译码片选?

(1)

2 14 × 2 8 = 2 22 = 4 M 2^{14}\times 2^8 =2^{22}=4M 214×28=222=4M

(2)

位扩展: 8 1 = 8 \frac 81=8 18=8

字扩展: 2 14 2 10 = 2 4 = 16 \frac{2^{14}}{2^{10}}=2^4=16 210214=24=16

16*8=128

(3)

A 13 A 12 A 11 A 10 A_{13}A_{12}A_{11}A_{10} A13A12A11A10

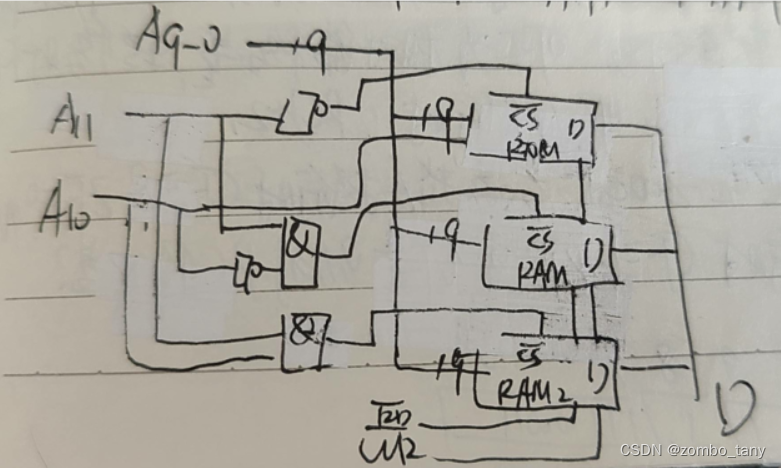

2.某个存储器容量为4KB,ROM为2KB,选用2K × 8 \times 8 ×8的ROM芯片;RAM为2KB,选用1K × 8 \times 8 ×8的RAM芯片,画主存储器的存储结构

ROM要1片,RAM要2片,字扩展

ROM地址:

片内 11 位 { 0 ∣ 000 0000 0000 0 ∣ 111 1111 1111 片内11位\begin{cases} 0|000\ 0000\ 0000\\ 0|111\ 1111\ 1111 \end{cases} 片内11位{

0∣000 0000 00000∣111 1111 1111

RAM地址:

片内 10 位 { R A M 1 { 10 ∣ 00 0000 0000 10 ∣ 11 1111 1111 R A M 2 { 11 ∣ 00 0000 0000 11 ∣ 11 1111 1111 片内10位 \begin{cases} RAM_1 \begin{cases} 10|00\ 0000\ 0000\\ 10|11\ 1111\ 1111 \end{cases}\\ RAM_2 \begin{cases} 11|00\ 0000\ 0000\\ 11|11\ 1111\ 1111 \end{cases} \end{cases} 片内10位⎩

⎨

⎧RAM1{

10∣00 0000 000010∣11 1111 1111RAM2{

11∣00 0000 000011∣11 1111 1111

R O M = A 1 ‾ ROM=\overline{A_1} ROM=A1,

R A M 1 = A 11 A 10 ‾ RAM_1=A_{11}\overline{A_{10}} RAM1=A11A10

R A M 2 = A 11 A 10 RAM_2=A_{11}A_{10} RAM2=A11A10

第六章

1.某机器字长32位,指令为单字长指令,系统中具有二地址指令、一地址指令和零地址指令若干条。已知每个地址码长12位,采用扩展操作码方式,则二地址指令、一地址指令最多几条?

O P 地址 1 地址 2 8 12 12 \begin{array}{c|c|c} OP&地址1&地址2\\\hline 8&12&12 \end{array} OP8地址112地址212

二地址指令: 2 8 − 1 = 255 2^8-1=255 28−1=255

一地址指令:假设二地址指令有且只有一条,则一地址指令 255 ∗ 2 12 − 1 255*2^{12}-1 255∗212−1条

2.主存按字节编址,地址为7EA8H为首地址存放一条两字节指令,第一个为操作码OP是转移指令,第二个字节为相对寻址,位移量是D,是一个8位补码

1.位移量D表示范围?

-128~+127

2.该指令转移空间?

7EA8H为首地址,操作码+2为7EAA

7EAA-128=7E2A

7EAA+127=7F29

3.某计算机采用16位定长指令字格式,设计3条件转移(N为符号标志)

15 ∼ 11 10 9 8 7 ∼ 0 00000 C Z N O F F S E T \begin{array}{c|c|c|c|c} 15\sim 11&10&9&8&7\sim 0\\\hline 00000&C&Z&N&OFFSET \end{array} 15∼110000010C9Z8N7∼0OFFSET

00000为op,CZN为CF、ZF、NF检测位,某检测位为1就检测对应位,CF、ZF、NF有一个为1就转移,OFF为相对偏移量,转移时目标地址 ( P C ) + 2 + 2 × O F F S E T (PC)+2+2\times OFFSET (PC)+2+2×OFFSET,顺序执行时 ( P C ) + 2 (PC)+2 (PC)+2

(1)某条件转移指令地址为200CH,若该指令执行时CF=0,ZF=0,NF=1,则执行后的PC值?若执行时CF=1,ZF=0,NF=0,则PC值又是?

15 ∼ 11 10 9 8 7 ∼ 0 00000 0 1 1 1110 0011 \begin{array}{c|c|c|c|c}15\sim 11&10&9&8&7\sim 0\\\hline00000&0&1&1&1110\ 0011\end{array} 15∼110000010091817∼01110 0011

NF=1,

OFFSET=1110 0011=1111 1111 1110 0011=FFE3

PC=200C+2+2*FFE3=1FD4

CF=1,ZF=0,NF=0时,不转移。200C+2=200E

(2)实现无符号数比较小于等于时转移,CZN应是什么?

Z=1,C=1

第七章

1.指令DEC(100H)为减1指令,操作数寻址方式为间接寻址

0000 H 1000 H 1000 H 2000 H 2000 H 0000 H \begin{array}{c|c||} \hline 0000H&1000H\\\hline 1000H&2000H\\\hline 2000H&0000H\\\hline\end{array} 0000H1000H2000H1000H2000H0000H

(1)该指令操作数是?

0000H

(2)该指令周期中,DR改变几次?

5

(3)该指令执行结束,DR=FFFF

(4)SOCZ

1000

取指令,改变一次DR

将1000H取出,改变一次

将2000H取出,改变一次

将0000H取出,改变一次

执行0000H,FFFH->DR

2.某CPU主频1.03GHz,采用4级指令流水线,每个流水线执行需要1个时钟周期。假定CPU执行100条指令没有阻塞,则吞吐率?

T P = n k T + ( n − 1 ) T = 100 ( 4 + 99 ) 1 主频 = 1 × 1 0 9 TP=\frac{n}{kT+(n-1)T}=\frac {100}{(4+99)\frac{1}{主频}}=1\times 10^9 TP=kT+(n−1)Tn=(4+99)主频1100=1×109

3.某计算机采用微程序控制器,微操作控制字段直接编码,共33个微命令。5个互斥类,分别包括7,3,12,5,6微命令。控制字段需要几位?

7 3 12 5 6 3 2 4 3 3 \begin{array}{c|c|c|c|c} 7&3&12&5&6\\\hline 3&2&4&3&3 \end{array} 73321245363

3+2+4+3+3=15

4.在5个功能段指令流水线中,假设每段执行时间10ns,8ns,10ns,10ns,7ns,对12条指令流水线而言,加速比多少?实际吞吐率多少?

S p = 加速比 = 不流水线时间 流水线时间 = n k T k T + ( n − 1 ) T = 3.375 T = max i T i = max ( T 1 , T 2 , . . . , T n ) T p = n k T + ( n − 1 ) T = 12 10 × 5 + 11 × 10 = 0.075 S_p=加速比=\frac{不流水线时间}{流水线时间}=\frac{nkT}{kT+(n-1)T}=3.375\\T=\max_iT_i=\max(T_1,T_2,...,T_n)\\T_p=\frac{n}{kT+(n-1)T}=\frac{12}{10\times 5+11\times 10}=0.075 Sp=加速比=流水线时间不流水线时间=kT+(n−1)TnkT=3.375T=imaxTi=max(T1,T2,...,Tn)Tp=kT+(n−1)Tn=10×5+11×1012=0.075

第八章

1.主存-高速缓存采用直接映像,块大小32B,高速缓存单元4块,主存容量64块

(1)画主存和高速缓存地址格式

区号 区内块号 块内 c a c h e 块号 块内地址 4 2 5 2 5 \begin{array}{|c|c|c| |c|c|} \hline 区号&区内块号&块内&&cache块号&块内地址 \\\hline 4&2&5&&2&5\\\hline \end{array} 区号4区内块号2块内5cache块号2块内地址5

(2)若开始时cache无数据,CPU依次读21H,23H,05H,3FH,63H,82H(内存按字节编码),写出区号和块号,地址变换表内容?

21H:000 0010 0001,初次,地址变换表01块内tag为0000

23H:000 0010 0011,命中,地址变换表01块内tag为0000

05H:000 0000 0101,初次,地址变换表00块内tag为0000

3FH:000 0011 1111,命中,地址变换表01块内tag为0000

63H:000 0110 0011,初次,地址变换表11块内tag为0000

82H:000 1000 0010,没命中,地址变换表00内tag为0001

命中率 1 3 \frac 13 31

地址变换表

地址变换表 t a g 块号 1 00 0 01 x 10 0 11 \begin{array}{c|c} 地址变换表tag&块号\\\hline 1&00\\\hline 0&01\\\hline x&10\\\hline 0&11 \end{array} 地址变换表tag10x0块号00011011

2.主存-高速缓冲器采用全相连映像,块大小32B,cache有4个块,主存容量64块

(1)画出主存和cache的地址格式

主存块号 块内地址 c a c h e 块号 块内地址 6 5 2 5 \begin{array}{|c|c| |c|c|}\hline主存块号&块内地址&&cache块号&块内地址\\\hline 6&5&&2&5\\\hline\end{array} 主存块号6块内地址5cache块号2块内地址5

(2)开始时cache无数据,装入时从小到大顺序装入空cache块,cache按FIFO替换,若CPU依次读21H,23H,05H,3FH,63H,82H,写出块号,这些操作完成后,地址变换表4个单元内容?

21H:0010 0001

23H:0010 0011 命中

05H:0000 0101

3FH:0011 1111 命中

63H:0110 0011

82H:1000 0010

命中率 1 3 \frac 13 31

t a g 块号 001 00 000 01 011 10 100 11 \begin{array}{c|c} tag&块号\\\hline 001&00\\\hline 000&01\\\hline 011&10\\\hline 100&11 \end{array} tag001000011100块号00011011

第九章

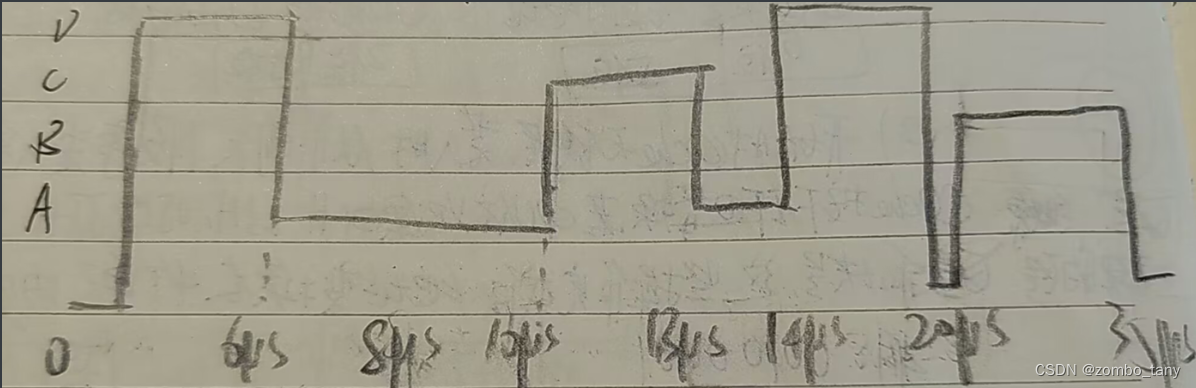

1.设某计算机有四级中断ABCD,硬件排队优先级ABCD,下表给出了执行每级中断服务程序所需时间,以执行中断服务程序时间作为中断处理优先级依据,时间越短优先级越高

程序 A B C D 时间 5 μ s 15 μ s 3 μ s 12 μ s \begin{array}{c|c|c|c|c} 程序&A&B&C&D\\\hline 时间&5\mu s&15\mu s&3\mu s&12\mu s \end{array} 程序时间A5μsB15μsC3μsD12μs

(1)设置屏蔽字

A B C D A 1 1 0 1 B 0 1 0 0 C 1 1 1 1 D 0 1 0 1 \begin{array}{c|c|c|c|c} &A&B&C&D\\\hline A&1&1&0&1\\\hline B&0&1&0&0\\\hline C&1&1&1&1\\\hline D&0&1&0&1 \end{array} ABCDA1010B1111C0010D1011

(2)如果ABCD分别在6 μ s \mu s μs,8 μ s \mu s μs,10 μ s \mu s μs,0s发出中断请求,画出执行序列

2.CPU与外设之间采用中断的方式实现数据输入输出,连接方式如图

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-0rYOM9t7-1681545144484)(C:\Users\Administrator.LAPTOP-21R73479\AppData\Roaming\Typora\typora-user-images\image-20230415153858268.png)]](https://img-blog.csdnimg.cn/a0a6989d3c5849fcbe00bcd09a18eac7.png)

(1)INTA的有效条件是什么?

CPU允许中断

(2)中断响应优先级从高到低?

2->3->4->1

(3)如果允许中断嵌套处理优先级从大到小顺序4231,则3屏蔽字?

1010

(4)中断响应周期需要解决娜几个问题?

CPU响应请求INTR后,由INTA回答中断机构。

中断机构将申请中断优先级最高的向量地址VA送给CPU

CPU将当前PC和PSW压栈保护

根据向量地址从内存中的中断向量表取出中断向量送入PC,关中断。

硬布线控制器需要占用几个机器周期时间为中断响应周期。

3.某总线有104根信号线,其中数据线32根,地址线25根,控制总线47根,工作频率33MHz,该总线宽度?传输率?

32bit, 32 8 × 33 M = 132 M B / s \frac{32}{8}\times 33M=132MB/s 832×33M=132MB/s

4.结合查询方式输入接口电路,说明CPU与外设数据传输过程

当输入设备准备好数据,将数据送入数据寄存器,产生脉冲信号STB,将输入数据锁存入数据寄存器中,将状态寄存器Ready位置1.

CPU检测状态字,先读取状态字,检测Ready位是否为1,若Ready=1,则执行第2步:从数据端口读取数据,将Ready置0

5.某计算机指令分4功能:IF、ID、EXE、WR,假设各功能时间90ns,80ns,70ns,60ns

(1)该CPU时钟周期至少是?

90ns

(2)若相邻指令数据相关,则后一条指令推迟多少个时钟周期?

I F I D E X W R 阻塞 阻塞 I F I D E X W R I F 阻塞 阻塞 I D E X W R \begin{array}{c|c|c|c|c|c|c} IF&ID&EX&WR\\\hline &阻塞&阻塞&IF&ID&EX&WR\\\hline &IF&阻塞&阻塞&ID&EX&WR \end{array} IFID阻塞IFEX阻塞阻塞WRIF阻塞IDIDEXEXWRWR

(两种阻塞与取指令先后方式都可以)

(3)若相邻指令数据相关,为了不推迟后一条指令,可采取什么措施?

32 8 × 33 M = 132 M B / s \frac{32}{8}\times 33M=132MB/s 832×33M=132MB/s

4.结合查询方式输入接口电路,说明CPU与外设数据传输过程

当输入设备准备好数据,将数据送入数据寄存器,产生脉冲信号STB,将输入数据锁存入数据寄存器中,将状态寄存器Ready位置1.

CPU检测状态字,先读取状态字,检测Ready位是否为1,若Ready=1,则执行第2步:从数据端口读取数据,将Ready置0

5.某计算机指令分4功能:IF、ID、EXE、WR,假设各功能时间90ns,80ns,70ns,60ns

(1)该CPU时钟周期至少是?

90ns

(2)若相邻指令数据相关,则后一条指令推迟多少个时钟周期?

I F I D E X W R 阻塞 阻塞 I F I D E X W R I F 阻塞 阻塞 I D E X W R \begin{array}{c|c|c|c|c|c|c} IF&ID&EX&WR\\\hline &阻塞&阻塞&IF&ID&EX&WR\\\hline &IF&阻塞&阻塞&ID&EX&WR \end{array} IFID阻塞IFEX阻塞阻塞WRIF阻塞IDIDEXEXWRWR

(两种阻塞与取指令先后方式都可以)

(3)若相邻指令数据相关,为了不推迟后一条指令,可采取什么措施?

转发、旁路(建立专用数据通路,将寄存器运算结果直接给ALU输入)