16位寄存器(16位)

电路功能:根据控制信号,将相应的输入进行输出。

输入:16位数据输入Din,1个使能信号En, 1个时钟信号Clk。

输出:16位输出Q。

要求:

(1)当En=1且有时钟信号输入变化时(Clk从0变化到1)时,Q=Din;否则Q的值维持不变;

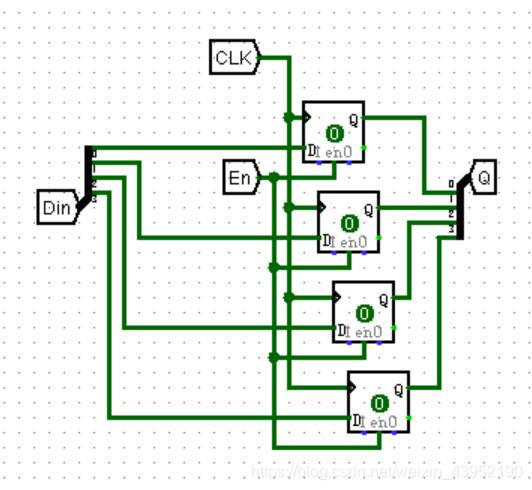

(2)先使用4个D触发器设计4位的并行加载寄存器并进行封装;

(3)用4个4位的并行加载寄存器进行并发得到16位的并行加载寄存器;

(4)电路完成后,通过改变输入16位数据以及变化En和时钟信号输入进行测试。

1. 先使用4个D触发器设计4位的并行加载寄存器并进行封装

2.封装后,4个4位的并行加载寄存器进行并发得到16位的并行加载寄存器

3. 电路完成后,通过改变输入16位数据以及变化En和时钟信号输入进行测试