Preface

When reviewing the microcontroller, the memory of the corresponding registers felt very confusing. Let’s sort it out here. The following words are used by me to assist memory, and may not represent the original meaning.

Second function of P3 port

| 0 |

RXD |

Serial data input port |

| 1 |

TXD |

Serial data output port |

| 2 |

INT0 |

External interrupt 0 input |

| 3 |

INT1 |

External interrupt 1 input |

| 4 |

T0 |

Timer 0 external count input |

| 5 |

T1 |

Timer 1 external count input |

| 6 |

WR |

Write strobe control signal for external data memory |

| 7 |

RD |

Read strobe control signal for external data memory |

Program Status Word Register (PSW)

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

| PSW |

Cy |

Ac |

F0 |

RS1 |

RS0 |

OV |

|

P |

D0H |

- Cy carry flag: can also be written as C. If there is carry/borrow, Cy=1; otherwise, Cy=0.

- Ac auxiliary carry flag: used for decimal adjustment during BCD code operation. When D3 and D4 bits generate a carry or borrow, Ac=1; otherwise, Ac=0.

- Flag bit used by F0 users: You can use instructions to set it to "1" or clear it. You can also use instructions to test the flag bit, and control the flow of the program based on the test results.

- RS1, RS04 group working register area selection control bit 1 and bit 0: used to select one of the 4 groups of working register areas in the on-chip RAM area as the current working register area.

- OV overflow flag: used to indicate whether the operation result overflows. If the result overflows, OV=1; otherwise, OV=0.

- P parity flag, the number of "1"s in accumulator A is an odd number, P=1, otherwise, P=0.

| RS1 |

RS0 |

4 sets of registers |

| 0 |

1 |

Area 0 (on-chip RAM 00H~07H) |

| 0 |

1 |

Area 1 (on-chip RAM 08H~0FH) |

| 1 |

0 |

Area 2 (on-chip RAM 10H~17H) |

| 1 |

1 |

Area 3 (on-chip RAM 18H~1FH) |

| Correspondence between RS1, RS0 and 4 groups of working register areas |

Interrupt entry address of the interrupt source

| Interrupt source |

Entrance address |

| External interruption 0 |

0003H |

| Timer T0 |

000BH |

| external interruption 1 |

0013H |

| Timer T1 |

001BH |

| Serial port |

0023H |

AUXR register

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

| AUXR |

|

|

|

WHIDLE |

DISTRIBUTION |

|

|

DISALE |

8EH |

- DISRTO: Disable/enable the reset output when the watchdog timer (WDT) overflows. 1: Disable the reset output when WDT overflows; 0: When WDT overflows, a high-level pulse is allowed to be output to the RST pin to reset the microcontroller.

- WDIDLE: WDT disable/enable bit in idle mode. 1: Disable WDT counting in idle mode; 0: Allow WDT counting in idle mode.

TCON (Timer/Counter Control Register)

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

| TCON |

TF1 |

TR1 |

TF0 |

TR0 |

IE1 |

IT1 |

ie0 |

IT0 |

88H |

| bit address |

8FH |

|

8DH |

|

8BH |

8AH |

89H |

88H |

|

- TF: The overflow interrupt request flag of the on-chip timer/counter T. After the counting is started, the count will be incremented by 1 from the initial value. When the count overflows, the hardware will automatically set "1" for TF and apply for an interrupt from the CPU. When the CPU responds to the TF interrupt, the flag bit is automatically cleared by hardware, and can also be cleared by software. (Flag)

- IE: Interrupt request flag bit for external interrupt request (enable)

- IT: Select the interrupt mode of the external interrupt request, 0 is the level trigger mode, and 1 is the negative transition trigger mode.

- TR: Counting operation control bit. 1: Necessary condition to start timer/counter counting; 0: Stop. Set or cleared by software.

SCON (Serial Port Control Register)

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

| DISCON |

SM0 |

SM1 |

SM2 |

REN |

TB8 |

RB8 |

OF |

RI |

98H |

| bit address |

9FH |

9EH |

9DH |

9CH |

9BH |

9AH |

99H |

98H |

|

- SM0, SM1: Serial port working mode selection bits.

- SM2: Multi-machine communication control bit.

- REN: Allow serial port reception bit (set to "1" or cleared by software), 1: Allowed; 0: Disabled.

- TB8: The 9th bit of data sent.

- RB8: The 9th bit of data received.

- TI: Serial port sends interrupt request flag. When the CPU writes 1 byte of data into the serial port's transmit buffer SBUF, it will start sending a frame of serial data. After each frame of serial data is sent, the hardware automatically sets the TI interrupt request flag. "1", after sending, it needs to be cleared with instructions in the interrupt service routine. TI must be cleared by software. (transmit)

- RI: Serial port reception interrupt request flag. After receiving a serial data frame on the serial port, the hardware automatically sets the RI interrupt request flag to "1", which needs to be cleared with instructions in the interrupt service routine. RI must be cleared by software. (receive)

| SM0 |

SM1 |

Function Description |

| 0 |

0 |

Mode 0, synchronous shift register mode (used for extended I/O port) |

| 0 |

1 |

Mode 1, 8-bit asynchronous reception and reception, variable baud rate (controlled by timer) |

| 1 |

0 |

Mode 2, 9-bit asynchronous reception and reception, baud rate fosc/64 or fosc/32 |

| 1 |

1 |

Mode 3, 9-bit asynchronous reception and reception, variable baud rate (controlled by timer) |

IE (interrupt enable register)

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

| IE |

EA |

|

|

ES |

ET1 |

EX1 |

ET0 |

EX0 |

A8H |

| bit address |

AFH |

|

|

ACH |

ABH |

AAH |

A9H |

A8H |

|

- EA: Interrupt enable master switch control bit. 1: Allow; 0: Block. (enable all)

- ES: Serial port interrupt enable control bit. 1: Allow; 0: Block. (enable serial)

- ET: Timer/counter overflow interrupt enable control bit. 1: Allow; 0: Block. (enable timer)

- EX: External interrupt interrupt enable control bit. 1: Allow; 0: Block. (enable external)

IP (interrupt priority register)

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

| IP |

|

|

|

PS |

PT1 |

PX1 |

PT0 |

PX0 |

B8H |

| bit address |

|

|

|

BCH |

BBH |

BAH |

B9H |

B8H |

|

- PS: Serial port interrupt priority control bit, 1: high priority; 0: low priority. (priority serial)

- PT: Timer T interrupt priority control bit, 1: high priority; 0: low priority. (priority timer)

- PX: External interrupt interrupt priority control bit, 1: high priority; 0: low priority. (priority external)

Query sequence of interrupts at the same level (interrupt level): External interrupt 0>T0 overflow interrupt>External interrupt 1>T1 overflow interrupt>Serial port interrupt.

TMOD (timer/counter operating mode memory)

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

| TMOD |

GATE |

C/T |

M1 |

M0 |

GATE |

C/T |

M1 |

M0 |

89H |

|

T1 mode field |

T0 mode field |

|

- GATE: Gate control bit, 1: controlled by the level on the external interrupt pin (or INT1) INT0 and the running control bit TRx; 0: controlled only by the control bit TRx (x=0,1).

- M1, M0: working mode selection bits.

- C/T: Counter mode and timer mode selection bit. 1: Counter working mode, counting the internal pulses after the system clock is divided by 12; 0: Counter working mode, the counter counts the external buying weight (negative transition) of the external input pin T0 or T1.

| M1 |

M0 |

Way of working |

| 0 |

0 |

Mode 0, 13-bit timer/counter |

| 0 |

1 |

Mode 1, for 16-bit timer/counter |

| 1 |

0 |

Mode 2, timer/counter automatically reloaded with 8-bit constant |

| 1 |

1 |

Mode 3:, only applicable to T0. At this time, T0 is divided into two 8-bit counters, and T1 stops counting. |

PCON

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

| PCON |

SMOD |

|

|

|

GF1 |

GF0 |

PD |

IDL |

87H |

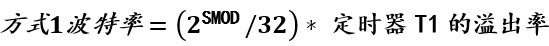

When SMOD=1, the baud rate is doubled compared to when SMOD=0.

Summarize

This article is mainly used to distinguish the general functions of different registers, so it is not very detailed. I write this mainly for my own memory, so it is a bit watery.

![]()