有关I2C的测试平台的代码可以参考我的https://blog.csdn.net/Real003/article/details/88920736(eeprom–24LC64)中有仿真代码。

-

I2C(Inter-Integrated Circuit)总线是一种由PHILIPS公司开发的两线式串行总线

-

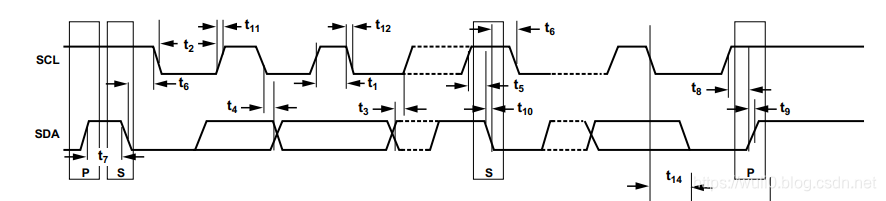

I2C总线在传送数据过程中共有三种类型信号:开始信号、结束信号和应答信号

开始信号:SCL为高电平时,SDA由高电平向低电平跳变,表示START。

结束信号:SCL为高电平时,SDA由低电平向高电平跳变,表示STOP。

应答信号:接收数据的Slave在接收到8bit数据后,向发送数据的Master发出特定的低电平脉冲,表示已收到数据。 -

I2C总线支持三种数据传输速度: 标准,快速模式和高速模式。

标准模式是100Kbps。 快速模式为400Kbps。 高速模式支持快至3.4Mbps的速度。 所有的与次之传输速度的模式都是兼容的。I2C总线支持7位和10位地址空间设备和在不同电压下运行的设备。 -

I2C 总线是一种用于IC器件之间连接的双向二线制总线,所谓总线它上面可以挂多个器件,并且通过两根线连接,占用空间小。I2C总线有两根信号线,一根为SDA(数据线),一根为SCL(时钟线)。任何时候时钟信号都是由主控器件产生。

-

I2C总线死锁有关问题也需要注意,在这篇文章中有提到:https://blog.csdn.net/fengel_cs/article/details/50563291(I2C死锁原因及解决方法)

在正常情况下,I2C总线协议能够保证总线正常的读写操作。但是,当I2C主设备异常复位时(看门狗动作,板上电源异常导致复位芯片动作,手动按钮复位等等)有可能导致I2C总线死锁产生。

在I2C主设备进行读写操作的过程中.主设备在开始信号后控制SCL产生8个时钟脉冲,然后拉低SCL信号为低电平,在这个时候,从设备输出应答信号,将SDA信号拉为低电平。如果这个时候主设备异常复位,SCL就会被释放为高电平。此时,如果从设备没有复位,就会继续I2C的应答,将SDA一直拉为低电平,直到SCL变为低电平,才会结束应答信号。而对于I2C主设备来说.复位后检测SCL和SDA信号,如果发现SDA信号为低电平,则会认为I2C总线被占用,会一直等待SCL和SDA信号变为高电平。这样,I2C主设备等待从设备释放SDA信号,而同时I2C从设备又在等待主设备将SCL信号拉低以释放应答信号,两者相互等待,I2C总线进人一种死锁状态。同样,当I2C进行读操作,I2C从设备应答后输出数据,如果在这个时刻I2C主设备异常复位而此时I2C从设备输出的数据位正好为0,也会导致I2C总线进入死锁状态。SCL为高,SDA一直为低原因

从:正常时序下:SDA信号是在SCL为低的状态下改变,即从应答SDA为低电平时,此时SCL应为为低电平(即从设备是先拉低SDA信号,等待主设备SCL由高变低,“取走”ACK信号后,从再释放SDA为高)。但如果此时时序被打乱,例如单片机i2c通信时突然复位,SCL突然变高,则从设备SDA一直为低,等待SCL变低。

主:SDA被从拉低,故主认为i2c总线占用,一直等待SDA变高

I2C死锁解决方法

最好用模拟I2C实现,则不会死锁

(1) 尽量选用带复位输人的I2C从器件。

(2) 将所有的从I2C设备的电源连接在一起,通过MOS管连接到主电源,而MOS管的导通关断由I2C主设备来实现。

(3) 在I2C从设备设计看门狗的功能。

(4) 在I2C主设备中增加I2C总线恢复程序。每次I2C主设备复位后,如果检测到SDA数据线被拉低,则控制I2C中的SCL时钟线产生9个时钟脉冲(针对8位数据的情况),这样I2C从设备就可以完成被挂起的读操作,从死锁状态中恢复过来。这种方法有很大的局限性,因为大部分主设备的I2C模块由内置的硬件电路来实 现,软件并不能够直接控制SCL信号模拟产生需要时钟脉冲。

(5) 在I2C总线上增加一个额外的总线恢复设备。这个设备监视I2C总线。当设备检测到SDA信号被拉低超过指定时间时,就在SCL总线上产生9个时钟脉冲,使 I2C从设备完成读操作,从死锁状态上恢复出来。总线恢复设备需要有具有编程功能,一般可以用单片机或CPLD实现这一功能。

(6) 在I2C上串人一个具有死锁恢复的I2C缓冲器,如Linear公司的LTC4307如图2所示:LTC4307是一个双向的I2C总线缓冲器,并且具有I2C总线死锁恢复的功能。LTC4307总线输人侧连接主设备,总线输出侧连接所有从设备。当LTC4307检测到输出侧SDA或SCL信号被拉低30ms时,就自动断开I2C总线输人侧与输出侧的连接.并且在输出侧SCL信号上产生16个时钟脉冲来释放总线。当总线成功恢复后,LTC4307会再

次连接输人输出侧,使总线能够正常工作。

- I2C位传输 数据传输:SCL为高电平时,SDA线若保持稳定,那么SDA上是在传输数据;

若SDA发生跳变,则用来表示一个会话的开始或结束

数据改变:SCL为低电平时,SDA线才能改变传输的bit

- I2C开始和结束信号

开始信号:SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据。

结束信号:SCL为高电平时,SDA由低电平向高电平跳变,结束传送数据。

- I2C应答信号

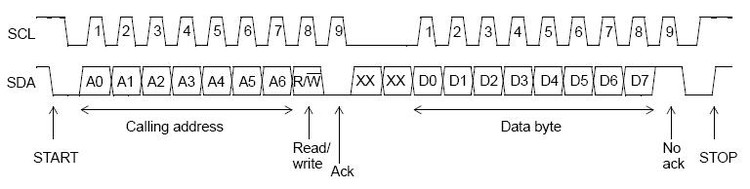

Master每发送完8bit数据后等待Slave的ACK。

即在第9个clock,若从IC发ACK,SDA会被拉低。

若没有ACK,SDA会被置高,这会引起Master发生RESTART或STOP流程

- I2C写流程

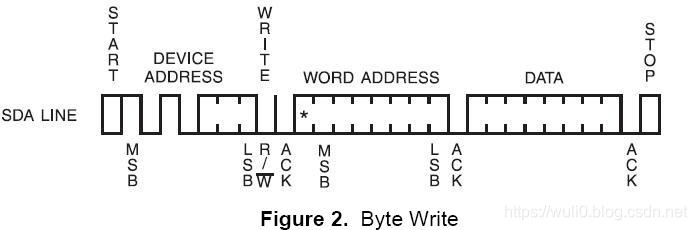

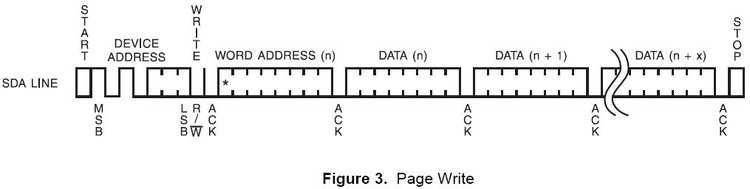

写寄存器的标准流程为:

(1. Master发起START

(2. Master发送I2C addr(7bit)和w操作0(1bit),等待ACK

(3. Slave发送ACK

(4. Master发送reg addr(8bit),等待ACK

(5. Slave发送ACK(第4步和第5步可以重复多次,顺序写多个寄存器地址)

(6. Master发送data(8bit),即要写入寄存器中的数据,等待ACK

(7. Slave发送ACK

(8. 第6步和第7步可以重复多次,即顺序写多个寄存器数据

(9. Master发起STOP

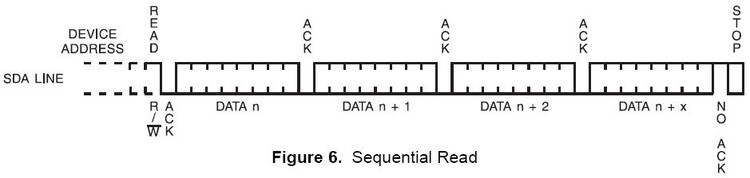

- I2C读流程

读寄存器的标准流程为:

(1. Master发送I2C addr(7bit)和w操作1(1bit),等待ACK

(2. Slave发送ACK

(3. Master发送reg addr(8bit),等待ACK

(4. Slave发送ACK

(5. Master发起START

(6. Master发送I2C addr(7bit)和r操作1(1bit),等待ACK

(7. Slave发送ACK

(8. Slave发送data(8bit),即寄存器里的值

(9. Master发送ACK

(10. 第8步和第9步可以重复多次,即顺序读多个寄存器

参考文档:https://blog.csdn.net/chenze2017/article/details/65938194(I2C总线协议及应用)