理解I2C总线

摘要

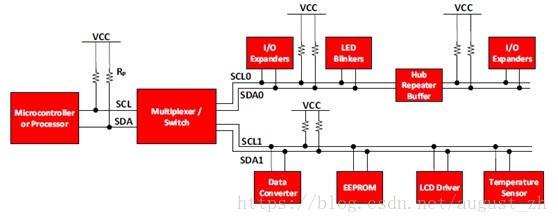

I2C是一种非常流行的2 wires总线,主要用在单个(或者多个)主机与单个或多个从机设备进行通信。其具体应用的框图如图1所示。

图1 I2C总线应用框图

本文主要的目的是帮助读者理解I2C总线工作的原理。

图1描述了一个I2C主机上连接多个从机设备的应用场景,在当今的嵌入式系统中较为常见。

1. 电气特性

I2C在电路设计中采用的是开漏/开集(open-drain/open-collector)这种驱动方式,保正了I2C在一根数据线上可以进行双向通信的能力。

1.1 开漏电路(open-drain)

所谓开漏电路概念中提到的“漏”指的是MOSFET的漏极,开漏电路就是指以MOSFET的漏极为输出的电路,一般的用法是在漏极外部的电路上增加上拉电阻。用在I2C电路中,可以把总线拉低到地,也可以不驱动总线,让连接在总线上的上拉电阻将其拉到高电平。这样,在I2C应用场景中,如果主机或者从机都没有去驱动总线,在这种情况下,

利用总线上的上拉电阻Rpu,就可以把总线上的电压上拉到指定电平。同时,由于设备不会去强制在总线上输出高电平,这样也就避免了通信过程中一个设备发送高电平,而另外一个设备发送低电平,而导致冲突的情况。

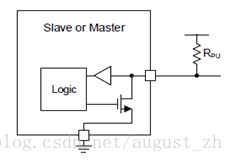

图2 SDA/SCL线上的内部结构

图2为主机或者从机SDA/SCL line内部结构框图,由Buffer与FET两部分组成。设备只能把总线拉低或者释放总线,不对其进行驱动,依靠外部的上拉电阻把其拉高到高电平。在设计I2C总线设备时,一定要意识到这一点,即设备没有这种让总线保持为高电平的能力。

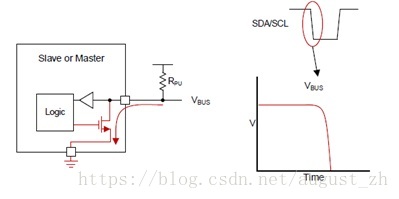

1.1.1 open-drain pulling low

正如上文所述,open-drain仅会把总线拉低,或者不驱动依靠外部的上拉电阻把总线进行拉高。图3展示了把总线拉低相应的电流流向。逻辑端想发送低电平信号只需要激活pull-down FET.,对地短路,把总线拉低。

图3 Pulling the bus low with an open-drain interface

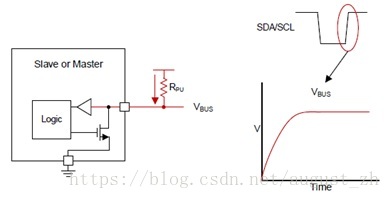

1.1.2 open-drain releasing bus

当主机或者从机传送逻辑高电平时,只需要释放总线,不对其进行驱动,关闭pull-down FET.此时总线处于悬空状态,总线外部的上拉电阻会把其拉高到指定电压。图4展示了 通过上拉电阻把总线拉高,电流的流向。

图4 Releasing the bus with an open-drain interface

2 I2C接口

2.1 通用的I2C操作

I2C总线是一个标准的双向接口,通过主机控制器与其连接的从机设备进行通信。通信时每次都是由主机发起。主机通过从机设备的地址来进行区分I2C总线上的从机设备。I2C接口一般是由SCL与SDA线组成. SDA与SCL线上需要通过上拉电阻上拉到Vcc. 所需要上拉电阻的阻值的大小是由I2C总线上的电容量所决定. 并且只有当总线处于空闲状态时,才能发起数据的传输。如果I2C总线SDA与SCL线都处于高电平状态,可以认为I2C总线处于空闲状态。

一般情况下,主机是按照如下流程与从机设备进行交互。

1. 主机给从机发送数据

主机发送START condition以及要访问的从机地址;

主机给从机发送数据;

主机发送STOP condition结束本次的数据传输;

- 主机接收从机发送过来的数据

主机发送START condition以及要访问的从机地址;

主机将待访问的地址发送给从机;

主机接收从机发送过来的数据;

主机发送STOP condition结束本次的数据传输;

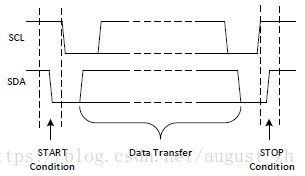

2.1.1 开始信号(START)与结束信号(STOP)

I2C总线在传送数据过程中共有三种类型的控制信号,分别为开始信号,结束信号以及应答信号。

开始信号:SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据;

结束信号:SCL为高电平时,SDA由低电平向高电平跳变,终止数据传输;

图5 START与STOP conditions