背景

昨天出去了一趟,人问:你熟悉什么?答:软硬件。结果,好尴尬。

硬件一般都做什么内容?

答:电源设计。

能说下升压、降压电路是怎么实现的吗?

答:不能。(Ps:后续增加 电源设计原理)

通讯都用到什么接口?

答:UART、I2C、SPI。

然后我想,I2C 我研究了好久,我得把话题转到 I2C 上。

我说:我最近在做 I2C 的接口。

I2C 和 SPI 有什么区别?

答:I2C 总线只需要 2 根线, SPI 对于每个从设备都要外加一条 NSS。而且通讯速率相差甚异。I2C 最高通信频率只能到 4Mbit/s。SPI 能到 50Mbit/s,具体还取决于主从机的性能。

知道为什么 I2C 速度提不上去吗?

答:我猜是 阻容特性导致的,具体的不清楚。

…….

经过这次,我猜发现,我对 I2C 的了解程度并没有我想象中那么深入。

因此决定用篇文章专门研究 I2C 总线。

I2C 名称的由来

Ps:昨天和男票看《观复嘟嘟》,男票就提到,每次马老师讲一个事物时,总是会先长篇介绍这个事物名称的由来,实际上有助于帮助我们去了解。因此,首先,先介绍下 I2C 名称的由来。

I2C 是 Inter-Integrated Circuit 的简写,Inter-Intergrated Circuit 翻译过来,曰:内置集成电路。为什么 I2C 是内置集成电路?

I2C 总线是由飞利浦(Philips)半导体公司在 80 年代初设计出来的,为了让主板、嵌入式系统或手机用以连接低速周边装置而发展的。

从上面这段语句中,可以得知,I2C 是为了解决低速设备接入高速设备而存在的。

I2C 可以写成 I²C、IIC。

- I2C 读作: I - two - C

- I²C 读作: I - squared - C

- IIC 读作: I - I - C

- 在中国,咱们读: I 方 C。这个读法,我想国外友人应该是没法听懂的。

I2C 概述

I2C 总线是一种简单、双向二线制的同步串行总线。只需要 2 根线就可以和总线上的器件进行信息传递。

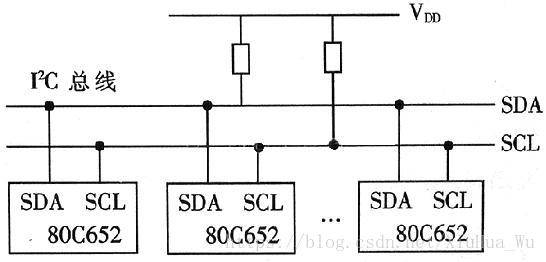

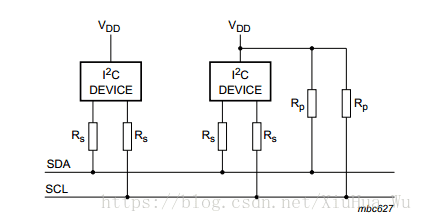

下图是一个典型的 I2C 总线连接示意图。

SDA 和 SCL

从硬件上来说, I2C 总线只有 2 根线,分别为 SDA 和 SCL,两者都是双向 I/O 线。总线接口已经集成在芯片内部,不需要特殊的接口电路。

- SDA :是串行数据总线,负责数据信号的传输。

- SCL:是串行时钟总线,负责时钟信号的传输。

电气特性

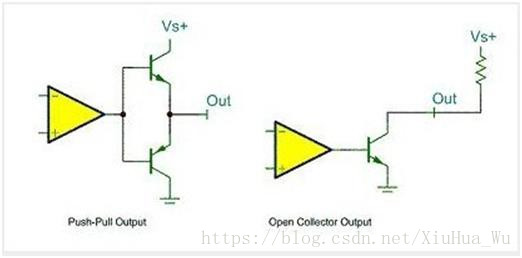

SDA 和 SCL 都是双向 I/O 线,接口电路为开漏输出(Open-drain),需要通过上拉电阻接电源 VCC。

这样,当总线空闲时,两根线都是 High。

NOTE:

I2C 总线器件均为 CMOS 器件,输出级均为开漏电路,因此,CMOS 器件在总线上消耗的电流很小。这样,就能保证 I2C 总线不需要太大的电流驱动能力,或者说,I2C 具有足够的驱动能力。

但是, I2C 总线扩展器件的数量并不是受限于电流驱动能力,而是受限于电容负载总量。I2C 总线的电容负载能力为 400pF(通过驱动扩展可达到 4000pF)。每一个器件的输入端都相当于一个等效电容,由于 I2C 总线扩展器件的连接方式为并联,因此,I2C 总线的总等效电容等于每一个器件等效电容之和,等效电容的存在会造成传输信号波形的畸变。在超出范围时,会导致数据传输出错。

Master 和 Slave

从接入的设备来说,I2C 总线上连接着主设备(Master)和从设备(Slave)。

- Master 用于启动数据传输,并产生时钟信号。

- 任何被寻址的器件均是被认为是 Slave。

NOTE:

Master 和 Slave 的关系不是恒定的,而是取决于此时数据传输的方向。

工作原理

若 Master 要发送数据给 Slave,则:

- Master 首先寻址 Slave

- Master 再主动发送数据给 Slave

- 最后由 Master 终止数据传送

若 Master 要接收 Slave 的数据,则:

- Master 首先寻址 Slave

- Master 再主动接收 Slave 发送的数据

- 最后由 Master 终止接收的过程

由此可见,无论是发送数据或者接收数据,都是由主机主动发起和终止数据传输过程。同时, Master 还负责在 SCL 上产生时钟。

数据传输

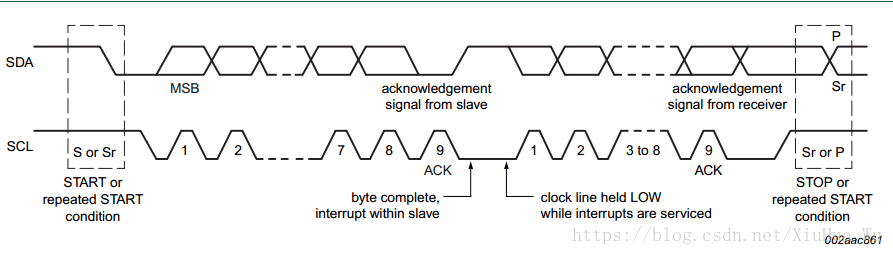

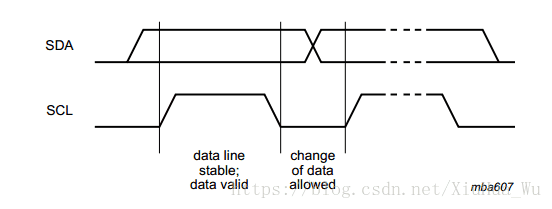

下图为 I2C Bus的数据传输示意图。

数据有效性

SDA 上的数据必须:

- 在 SCL 为 High 时,保持不变

- 在 SCL 为 Low 时,进行电平转换

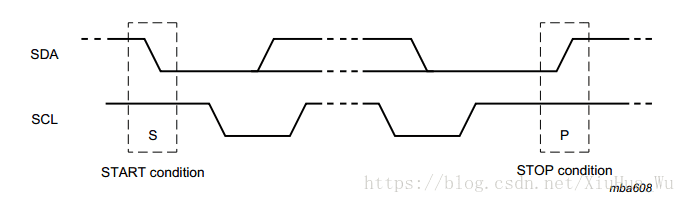

起始信号和停止信号

每次 Master 发起通讯时, Master 必须产生起始信号(Start)。

在每次通讯结束时,Master 必须产生停止信号(Stop)。

- Start 信号:SCL 为 High 时,SDA 由 High 变 Low ,产生下降沿。

- Stop 信号:SCL 为 High时, SDA 由 Low 变 High,产生上升沿。

Byte 格式

- 发送到 SDA 线上的每个数据长度必须为 1 Byte(8 bits)

- 每次传输可以发送的字节数量不受限制

- 每个字节后必须跟一个响应位(Ack)

- 首先传输的是数据的最高位(MSB)

应答响应

I2C 总线共有 2 种应答。当生产 Ack ,认为数据通讯正常,主机可继续通讯。当产生 NAck,认为数据通讯异常,主机可产生停止信号(P)结束通讯。

- Ack : 第 9 个 SCL 脉冲时,SDA 为 Low

- NAck : 第 9 个 SCL 脉冲, SDA 为 High

NOTE:

当为 I2C 读时序时, 最后一个 Byte 均产生 NAck,为正常情况。

当为 I2C 写时序是,最后一个 Byte 均产生 Ack,为正常情况。

I2C 总线共有 2 种情况,需产生应答:

Slave Address + W/R 响应。Master 发送 Slave Address + W/R 后,必须由被寻址的 Slave 产生 Ack,若不存在对应地址的 Slave,主机将接收到 NAck,产生停止信号(P)以终止数据传输。

数据响应。在每 Byte 数据后的第 9 个 SCL 脉冲,必须由 Receiver 产生 Ack,以响应 Transmitter 数据通讯正常,若 Receiver 正在进行其他操作而无法响应 Transmitter时,需产生 NAck 以终止数据传输。

NOTE:

- 地址应答必须由 Slave 应答

- 数据应答不区分 Master 和 Slave ,仅区分 Transmitter 和 Receiver。

时钟扩展

在数据传输过程中,如果 Slave 要完成一些其他功能后,才能接受或发送下一个完成的数据字节,可以使 SCL 保持 LOW,迫使 Master 进入等待状态,当 Slave 准备好接收下一个数据字节并释放 SCL 后,数据传输继续。

Slave Address 和 R/W

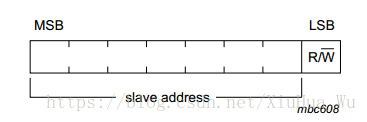

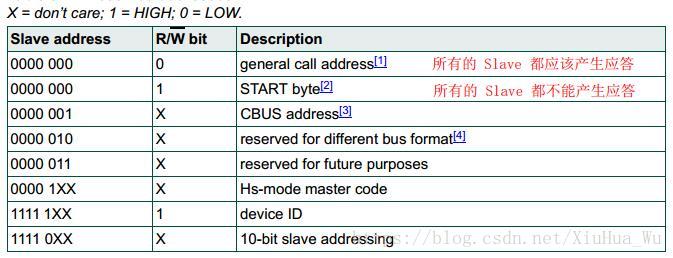

在 Master 发起通讯时,在产生 Start 信号后,Master 发送 Slave Address 和 R/W。

Salve Address 为 7 bits。实际可用地址为:(0x07, 0x78)

以下为特殊用途的 Slave Address:

R/W:

- R/W = 0 时,表示 Write

- R/W = 1 时,表示 Read

Software Reset

若在 General Call(0000 0000h)后,主机发送 0x06(0000 0110),将产生软件复位。

I2C 总线速率

I2C 共有 5 种通讯速率,分为双向(Bidirectional Bus)和单向(Unidirectional Bus)。

- 双向(Bidirectional Bus):

- Standard-mode(Sm):up to 100 kbit/s

- Fast-mode(Fm):up to 400 kbit/s

- Fast-mode Plus(Fm+):up to 1 Mbit/s

- High-speed mode(Hs-mode):up to 3.4 Mbit/s

- 单向(Unidirectional Bus):

- Ulrta Fast-mode(UFm):up to 5 Mbit/s

总线电气特性计算

上拉电阻 Rp 阻值计算

供电电压 VDD 和最大输出低电平,决定上拉电阻 Rp 的阻值。

Example:

VDD = 5 V ± 10%, Vol(max) = 0.4 V at 3 mA

Rp(min) = (5 + 5*10% - 0.4)/0.003 = 1.7 kOhm