对于FPGA调试,主要以Intel FPGA为例,在win10 Quartus ii 17.0环境下进行仿真和调试,开发板类型EP4CE15F17。主要包括一下几个部分:

- FPGA的调试-虚拟JTAG(Virtual JTAG)

- FPGA的调试-在线存储器内容编辑工具(In-system Memory Content Editor)

- FPGA的调试-内嵌逻辑分析仪(SignalTap)

- FPGA的调试-LogicLock

- FPGA的调试-调试设计的指导原则

上述内容主要参考《通信IC设计》,有兴趣的可以自己购买书籍进行研读。

1、相关理论知识

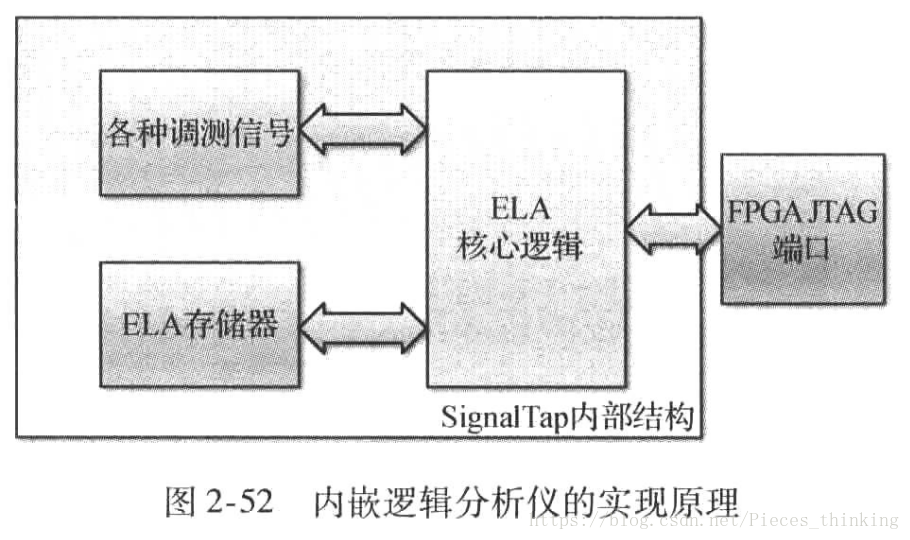

1.1内嵌逻辑分析仪

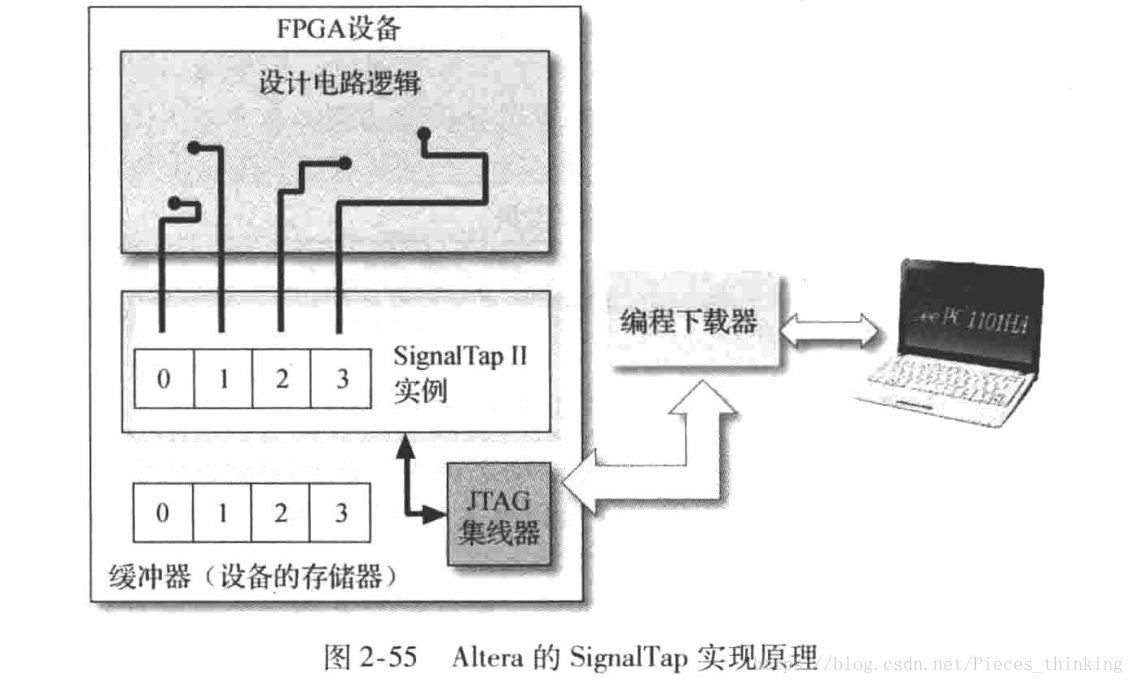

为方便用户进行调试,FPGA通常会内置信号观察逻辑,Altera提供的是GignalTap,而xilinx提供的则是ChipScope。此外还有第三方调试工具,如Synopsys的Identify。这类工具的核心原理为:以预先设定的时钟速率实时采样FPGA的内部信号或者引脚状态,并存储于FPGA的内部RAM中,然后通过统一的ELA(Embedded Logic Analyzer)进行数据分析和管理。当预设的触发条件满足后,ELA通过JTAG将存储在片内RAM中的数据缓存数据传输至PC上。当PC获得JTAG回传数据后,通过本地计算将对应的逻辑分析结果展现出来。

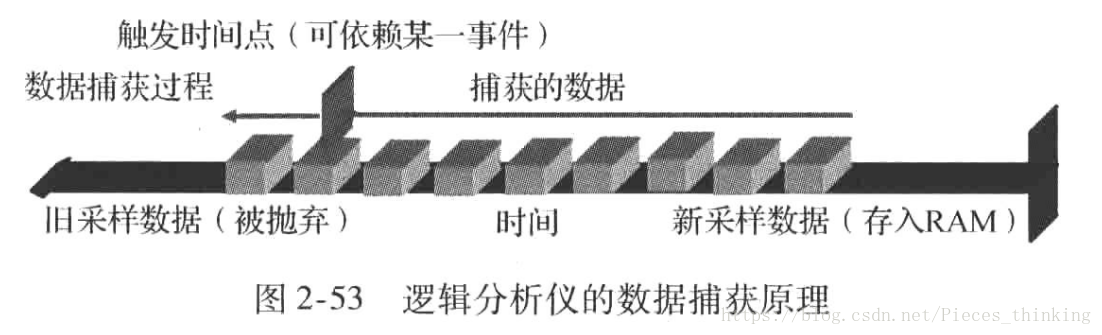

因此,无论是GignalTap还是ChipScope,其实都是在工程中额外加一些特殊模块实现信号的采集,所付出的代价包括:逻辑单元、内部RAM以及ELA资源。逻辑分析仪的数据捕获原理如图2-53所示,所有存储单元都是与当前逻辑设计的RAM共享的。如果当前逻辑占用RAM较大,内嵌的逻辑分析仪功能将会有非常大的存储深度限制。

从图2-53很容易发现,逻辑触发的时刻可以动态调整,而且存储的数据长度与时间也很容易调整。此外由于FPGA内置可编程能力,所以触发条件可以依赖于其他的事件触发,这样可以多级触发,形成基于状态的数据捕获。

例如当A信号为高电平,且持续32周期后,如果此时B信号为低电平且C信号有一个低脉冲,则触发一个等待事件;当等待事件发生65536个时钟周期后,再捕获数据,并通过逻辑分析仪发送出来。这就是基于状态机触发的逻辑分析功能,类似于Verilog中的Assertion断言和FSM状态机的有机结合体,是传统逻辑分析仪无法完成的。由于现在的逻辑通常都比较复杂,基于传统的条件触发模式,往往耗时耗力,很难快速找到BUG;而状态触发往往能够帮助设计者快速定位错误并调试。

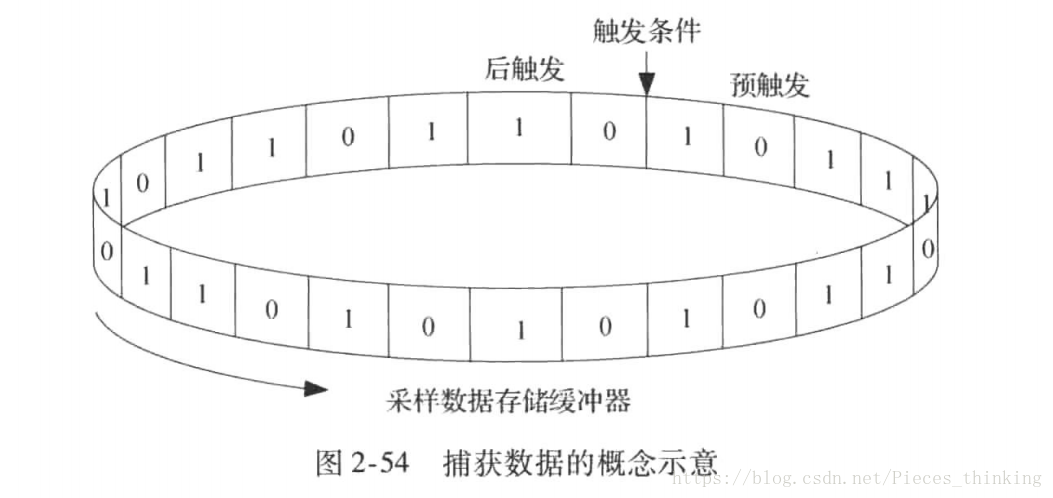

对于逻辑分析仪而言,除了触发条件外,还有一个存储位置的概念。正常情况下,FPGA会对需要CIA杨的数据一直采样,当数据放满后,将采用循环覆盖的方式存储,这类似于FIFO中的卷绕(WRAP)概念。当触发器触发后,通常缓冲器都是满的;如果采用预触发,将继续记录当前存储容量12%的数据后停止(有些厂商是不再记录,直接用当前记录数据);如果采用后触发,将继续记录当前存储容量的88%的数据后,停止记录(有些厂商是记录全部容量);如果是中间触发,将继续记录当前存储容量的1/2的数据。实际上什么时候开始记录,什么时候停止都可以通过状态触发实现。捕获数据的概念示意图如图2-54所示。

下面通过SignalTAP为例,简单讲述内嵌逻辑分析仪的调试技巧。

1.2 SignalTap

SignalTAP是Altera内置的逻辑信号观测工具,内部实现结构如图所示。

根据前面的逻辑分析仪原理,很容易得知FPGA可以实现多个并行的ELA。通过FSM和条件判断支持多级触发,FPGA也能够支持复杂的状态机数据捕获。令触发条件加上一个计数器,就很容易使FPGA能在不同的起始时刻捕获数据。而Altera所设计的SignalTAP正好是按照上诉方式设计的,其特点如下:

- 最大支持1024个数据捕获通道

- 单个器件支持多个并发的逻辑分析模块,包括跨多个时钟域的信号

- 每个数据捕获通道能够支持10级触发

- 支持在不同的位置进行捕获,包括信号前段、中段和后段。

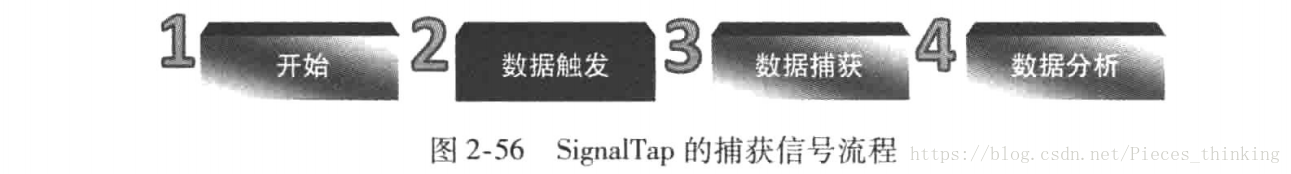

SignalTAP的捕获流程如图所示。

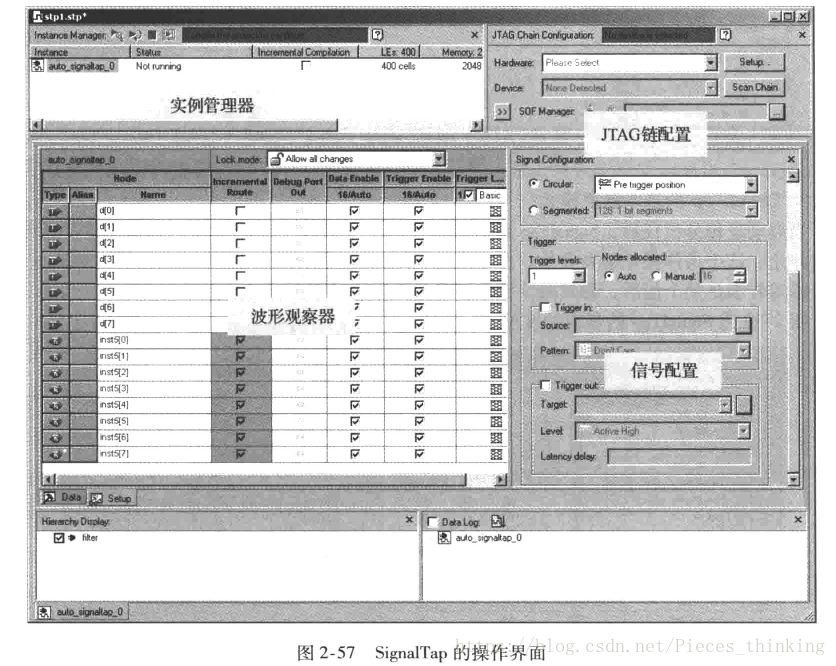

1.2.1 SignalTap的界面

操作界面如图所示。

1.2.2 SignalTap的演示

演示放在实例里

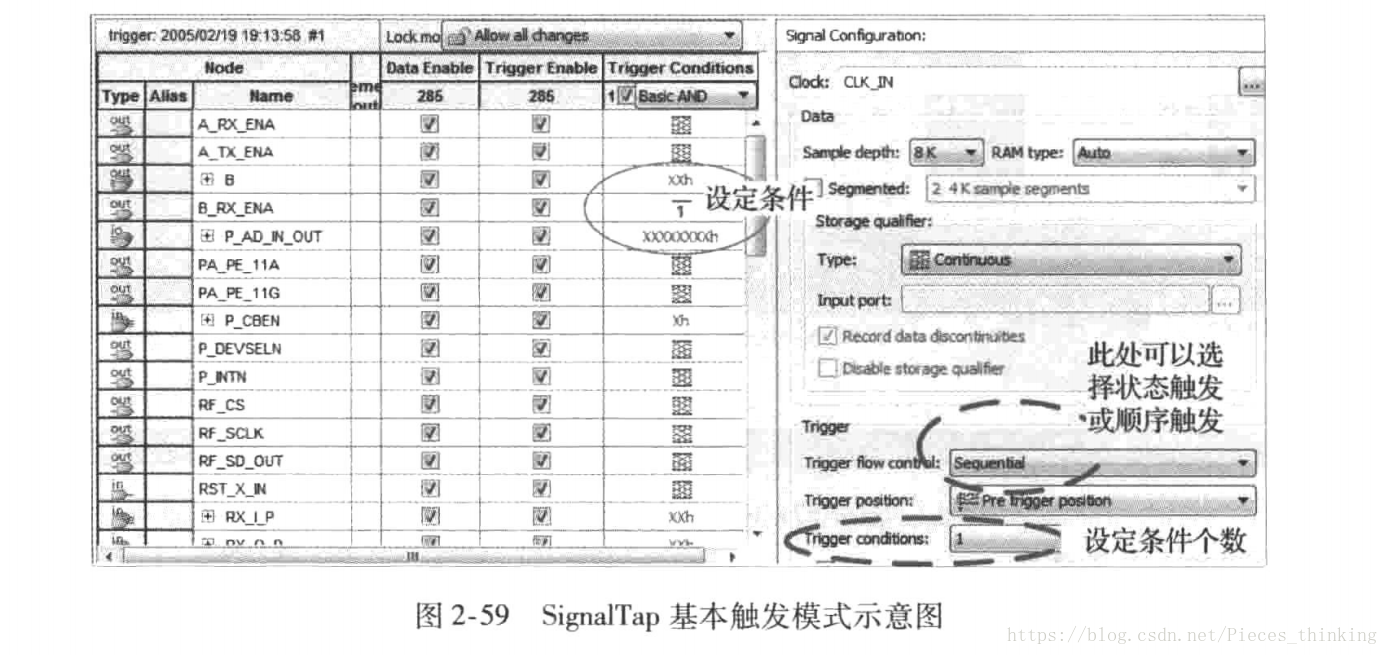

1.2.3 SignalTap的基本触发模式

当启动逻辑分析仪后,SignalTAP会对被监视的信号进行不断的采样,一直到某个条件满足后停止,这个条件就是触发条件。在基本模式下,触发条件被设定为当前信号的逻辑组合。当逻辑组合满足某个值后,触发条件将被满足,数据将被采样保存并上传到PC。

下图是SignalTAP的基本触发模式示意图。

1.2.4 SignalTap的Advanced Trigger模式

在信号列表Trigger Conditions栏的顶端选择Advanced,Advanced会弹出逻辑编辑器,在这里可以设计一个复杂的触发表达式。

1.2.4 SignalTap基于状态触发的触发模式

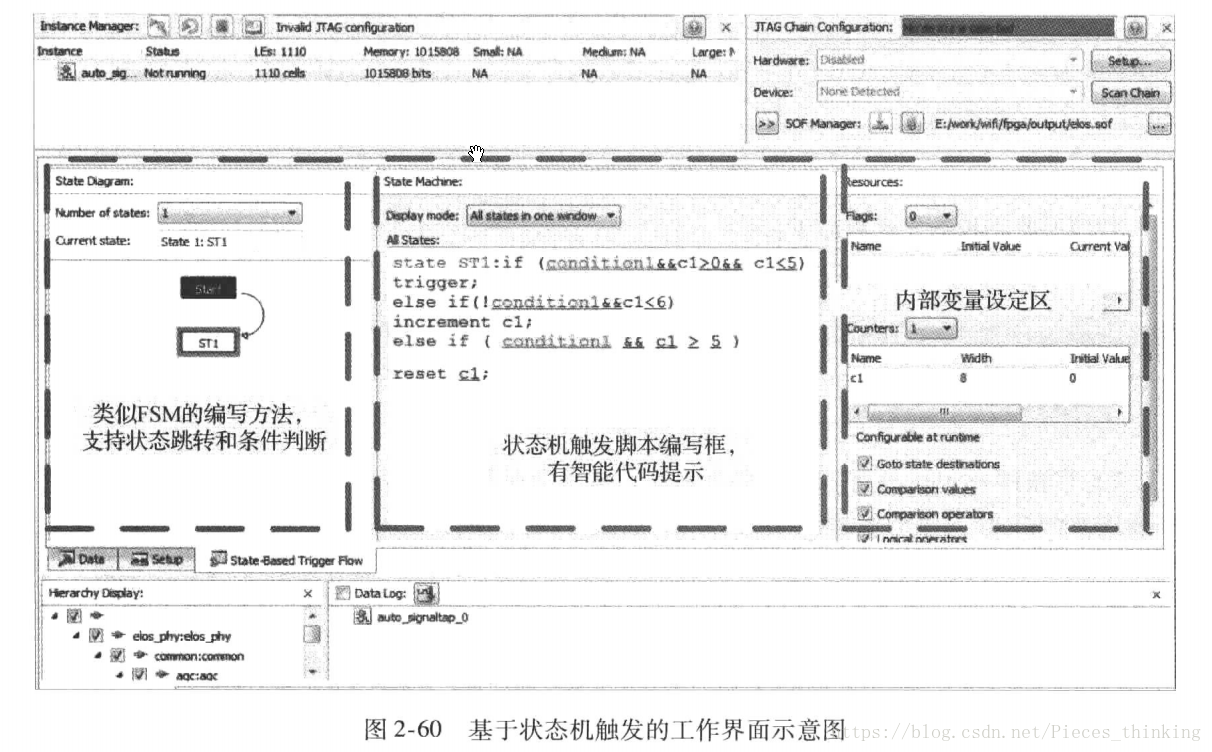

基于状态触发的逻辑分析仪模式是FPGA内嵌分析仪的而核心技术,主要技巧在于任何通过状态触发语句实现状态机的触发。下图是状态机触发的工作界面。

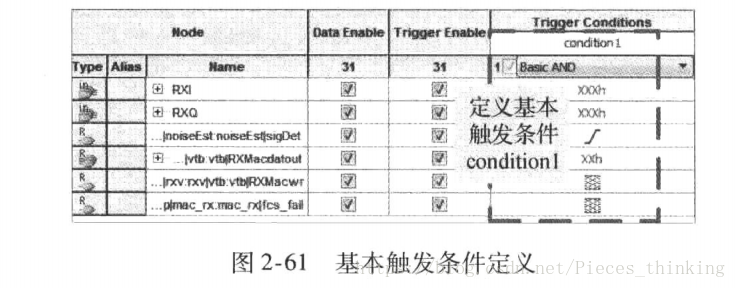

在设定触发条件前,先需要确定基本的触发条件,具体如图所示。

在设定基本触发条件后,就可以启动状态机的脚本设计,下面通过几个例子来说明状态机触发的实现方法:

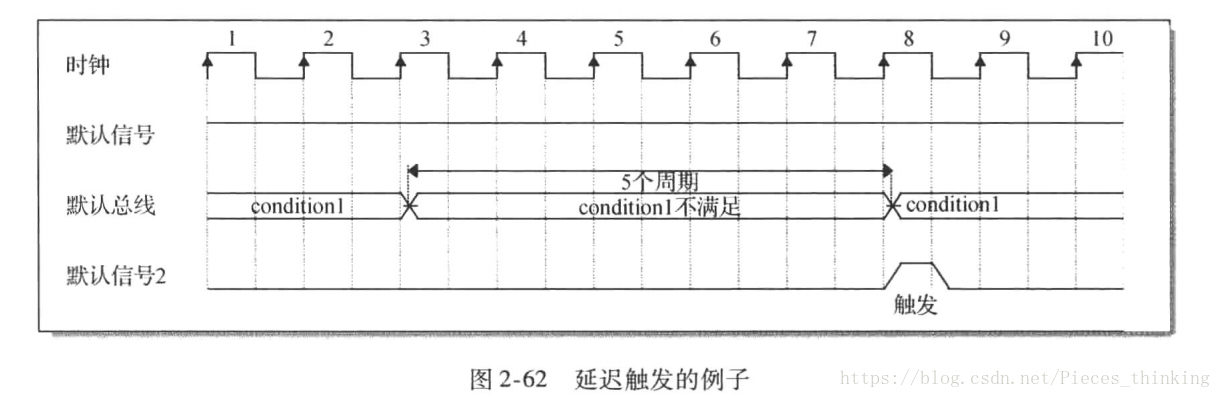

1)当条件condition1不满足,且持续时间超过5个时钟周期后,触发触发器,相关理想波形如图所示:

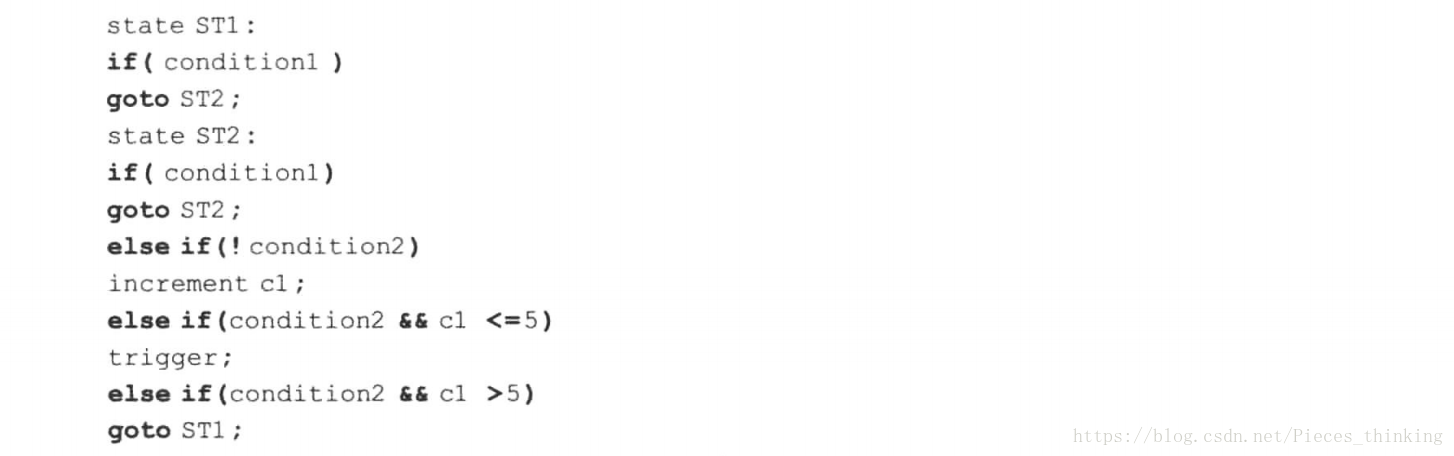

对应的状态机触发代码如下:

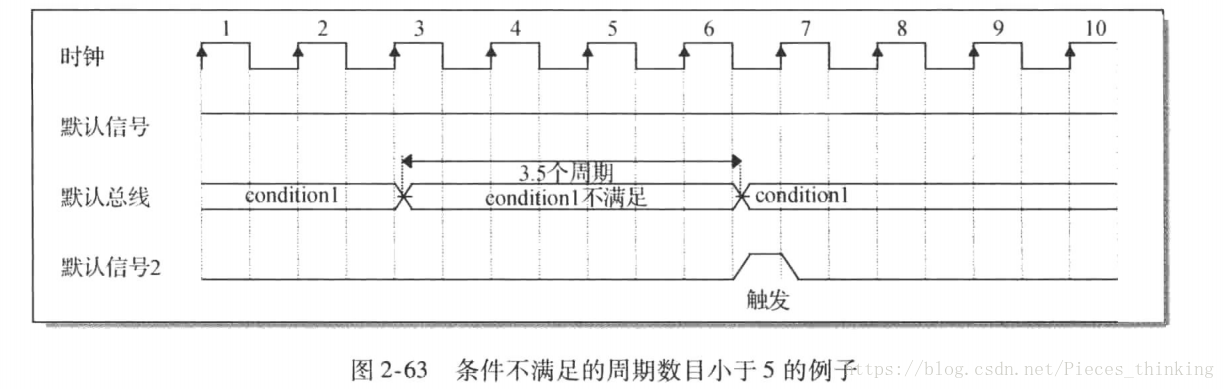

2)当条件condition1不满足情况发生,且不满足情况在不超过5个时钟周期内,又发生条件condition1满足的情况,则触发触发器,否则停止触发。一个典型的例子图下图所示。

上诉触发触发器的脚本如下:

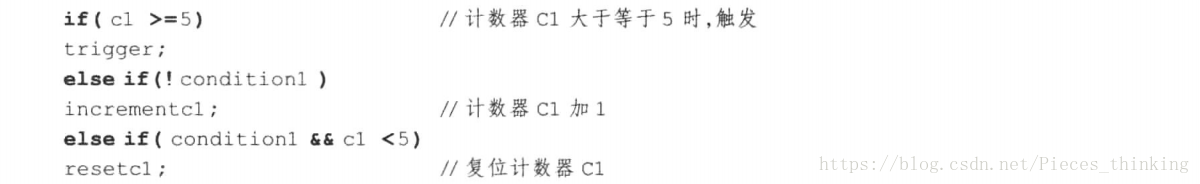

3)当condition条件满足5次后,触发触发器,否则停止触发。该例子的脚本如下:

4)当condition1条件满足后,如果condition2能够满足,则立即触发触发器,否则停止触发。该例子的脚本如下:

5)当condition1条件满足后,如果5个采样时钟周期内,condition2能够满足,则立即触发触发器,否则停止触发。该例子的脚本如下:

由于任何复杂的条件都可以简化为顺序、分支和循环3种情况,通过计数器能够实现循环,通过条件判断可实现分支,而通过状态机可实现流程控制。因此任意复杂的条件触发,都能够通过上诉条件组合捕获。

前面所举的5个例子,就是上诉不同场景的组合,因此读者只需要将上诉5个例子进行组合就能基本掌握触发条件的实现,熟练进行FPGA调试。

2、简单实例

留在下一篇吧。。。

传送门 内容很丰富,点一下哟!