FPGA开源工作室将通过五篇文章来给大家讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。

本实验和工程基于Digilent的Arty Artix-35T FPGA开发板完成。

软件使用Vivado 2018.1。

第一篇:DDR3和mig的介绍

1 DDR3介绍

以镁光的MT41K128M16为例来介绍DDR3。

通过以上信息我们即可知道DDR3的内存容量,Row,Column和Bank的地址位宽。开发板选用的MT41K128M16 DDR3的容量为16Megx16x8banks=2048Mb=2Gb。

1.1DDR3命名

我们通过Configuration,Package,Speed...等DDR3的命名可知道DDR3的容量,封装,速度等级等信息。

1.2 DDR3的内部结构

1.3接口

使用xilinx mig IP来控制DDR3的数据读写我们了解DDR3以上信息即可。

2 mig介绍

如上图所示,mig(Memory Interface Solution) IP由三部分组成User Interface Block,Memory Controller和Physical Layer。IP的一边是连接DDR3的接口(Physical Interface),另一边是用户逻辑控制接口(User FPGA Logic)。想要正确的控制DDR3的读写,我们需要正确的设置mig IP和正确的用户逻辑控制接口逻辑。

2.1 mig user interface

对于mig用户端接口含义我们将在《第三篇--mig IP用户逻辑接口读写时序分析》中详细介绍。

3 DDR3原理图和FPGA原理图

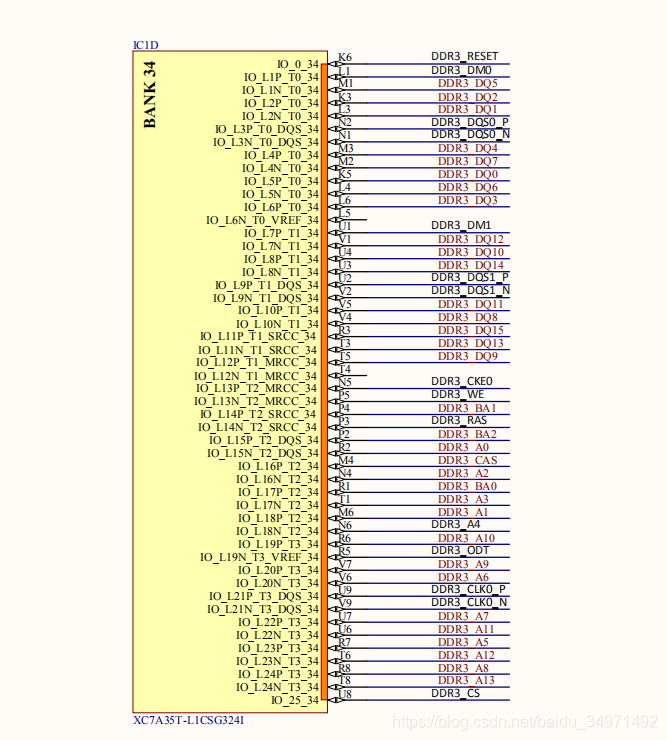

通过DDR3的原理图我们可以知道DDR3的供电电压为1.35V。DDR3挂在FPGA的34 bank上。

FPGA开源工作室为了大家更好的学习FPGA目前开通了知识星球(FPGA自习学院)。

FPGA自习学院将不断更新和总结FPGA相关的学习资料,欢迎大家加入。