计算机组成原理学习笔记——主存和CPU连接

其他

2020-04-01 12:45:00

阅读次数: 0

1、连接原理

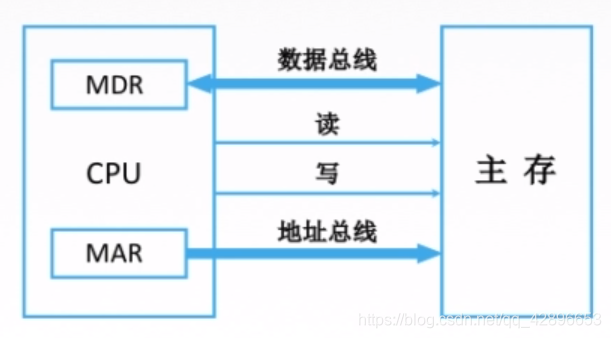

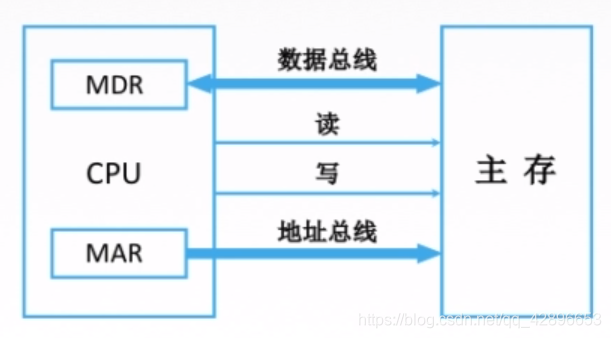

- 1)主存通过数据总线、地址总线和控制总线与CPU连接。

- 2)数据总线的位数与工作频率的乘积正比于数据传输率。

- 3)地址总线的位数决定了可寻址的最大内存空间。

- 4)控制总线(读/写)指出总线周期的类型和本次输入/输出操作完成的时刻。

- 主存和 CPU 连接方式大致如下图:

2、主存容量扩展技术

- CPU 的数据线数与存储芯片数据位数不一定相等,通常进行位扩展,用多个存储芯片对字长进行扩充,使数据位数与 CPU 的数据线数相等。可用的技术方法有位扩展法、子扩展法和字位同时扩展法。

2.1、位扩展法

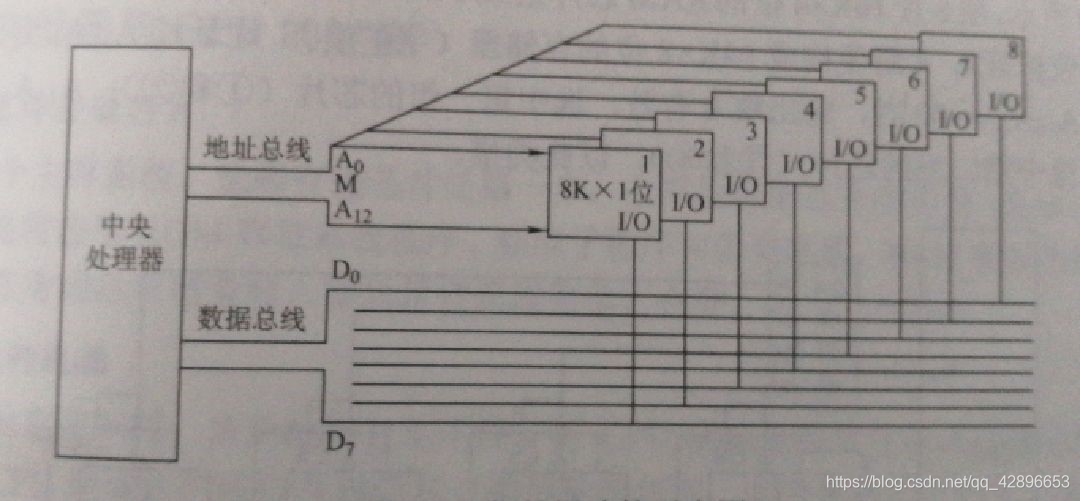

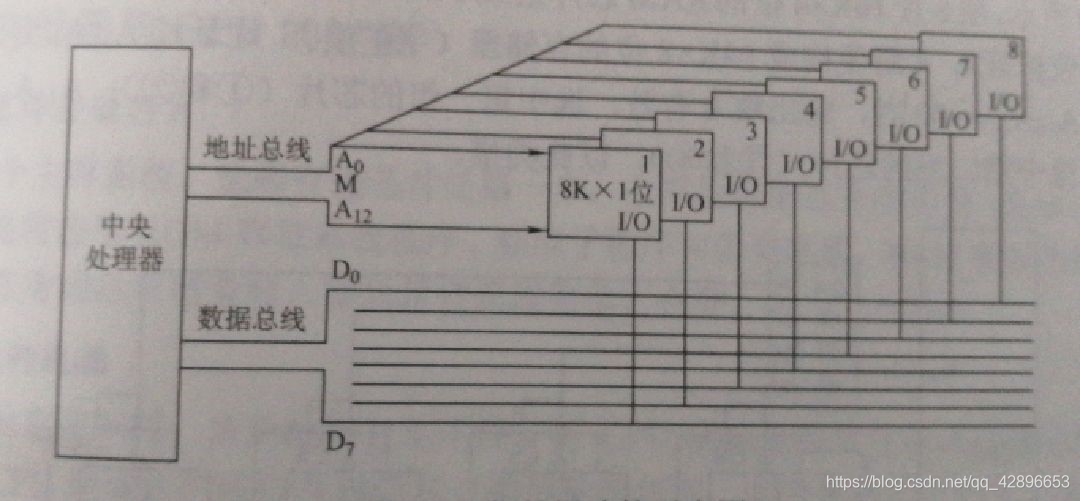

- 位扩展就是将多个存储芯片的地址端、片选端和读写控制端相应并联,数据端分别引出,

- 如图将 8 片 8K1 位芯片组成 8K8 位芯片组,所有芯片的地址线、片选信号线以及命令信号线都分别连在一起,而每片的数据线作为 CPU 数据线的一位。

- 注意:仅采用位扩展时,各个芯片连接地址线的方式一样,而连接数据线的方式不一样,某一时刻选中所有芯片,所以片选信号线要连接到所有芯片。

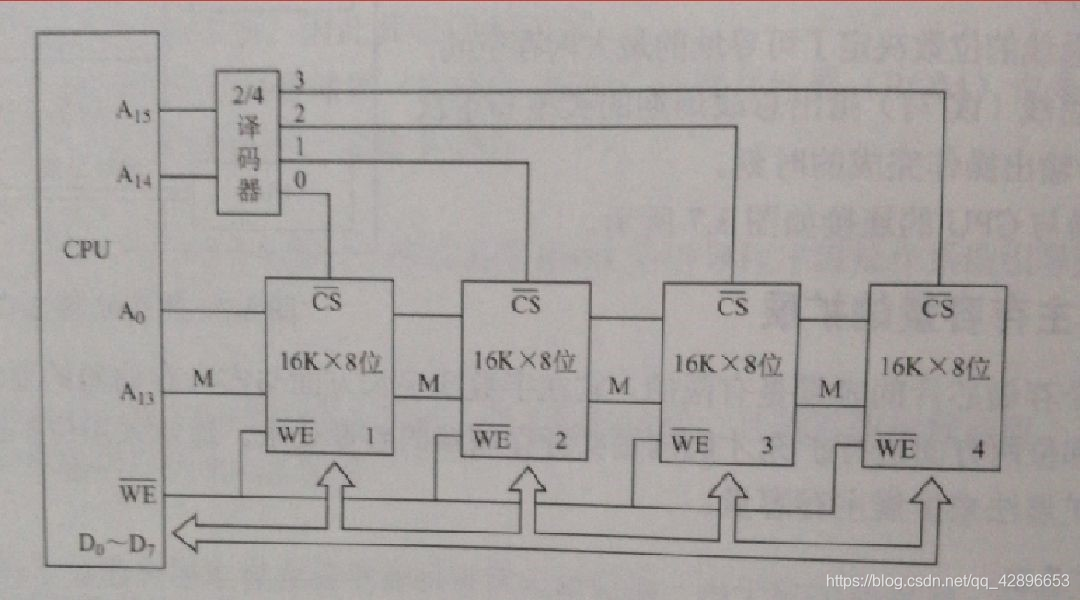

2.2、字扩展法

1.3、字位同时扩展

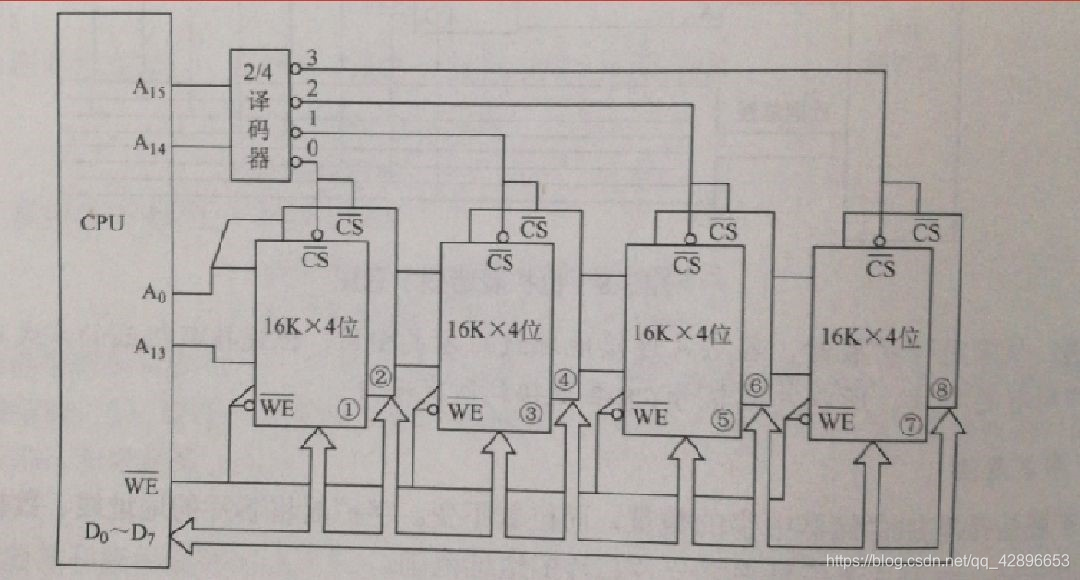

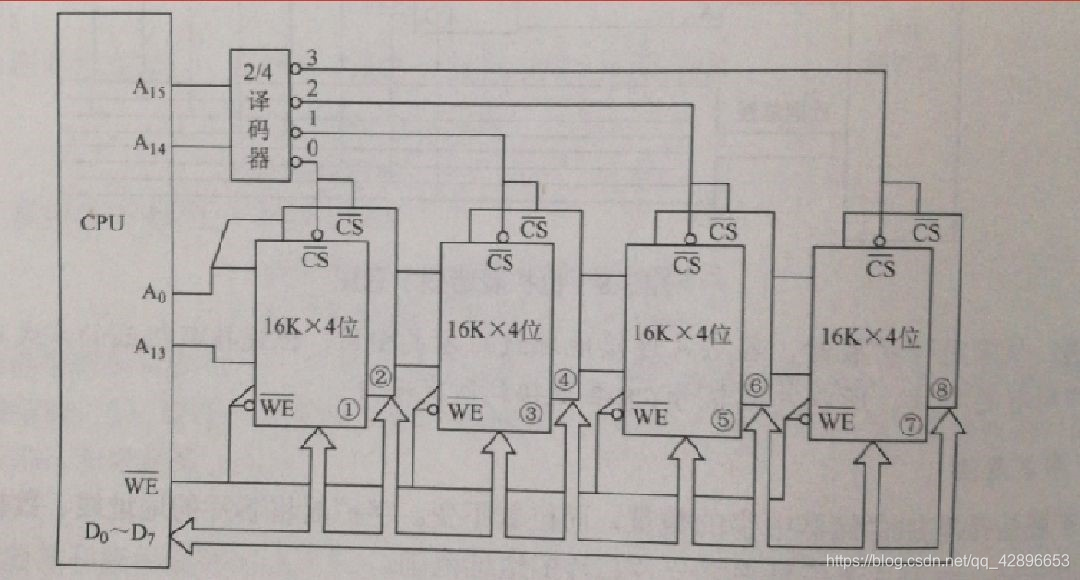

- 正如其名,字位同时扩展就是既增加存储字的数量,又增加存储字长。

- 如上图是将 8 片 16K4 位 RAM 芯片组成 64K8 位存储器,每两片构成一组 16K8 位存储器,在将这样的四组构成 64K8 位存储器。地址线 A15A14 经译码器得到 4 个片选信号,A15A14=00 时,输出端 0 有效,选中第一组芯片;A15A14=01 时,输出端 1 有效,选中第二组芯片,以此类推。

- 注意:采用字位同时扩展时,各个芯片连接地址线的方式相同,但连接数据线的方式不同,而且需要通过片选信号或采用译码器设计连接到相应的芯片。

3、存储芯片的地址分配与片选

- 片选是 CPU 访问存储单元的首要工作,然后为选中的芯片依地址码选择相应的存储单元,以进行数据的存取,也就是字选操作。字选通常由 CPU 送出的 N 条低位地址线完成,地址线直接连接到所有存储芯片的地址输入端,N 取决于存储容量 2^N;片选信号的产生有线选法和译码片选法。

3.1、线选法

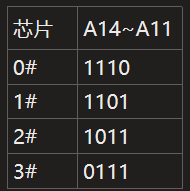

- 用除片内寻址外的高位地址线直接(或经反相器)分别连接到各个存储芯片片选端,当某些地址线信息为“0”时,就选中与之对应的存储芯片。值得注意的是,片选地址线每次寻址只能有一位有效,不允许同时多位有效,从而保证一次选中一个芯片或芯片组。

- 例子:

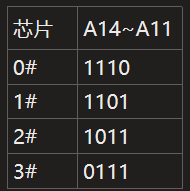

- 将 4 片 2K8 位存储芯片用线选法构成 8K8 位存储器,则地址分配可如下表:

- 其中 A10~A0 作为字选线,用于片内寻址。

线选法的优点是不需要地址译码器,线路简单;但是缺点是地址空间不连续,选片的地址线必须分时为低电平,不能充分利用系统存储空间。

3.2、译码片选法

- 用除片内寻址外的高位地址线通过地址译码器产生片选信号。

- 例子:

- 8 片 8K8 位存储芯片组成 64K8 位存储器,地址线16 位,数据线 8 位;需要 8 个片选信号,用一片 74LS138 作为地址译码器,则 A15A14A13=000 时选中第一片,A15A14A13=001 时选中第二片,以此类推。

4、搭建主存系统

- 搭建一个主存系统的步骤大致可以分为五步,分别是存储芯片的选取、地址线连接方式的选择、数据线连接方式的选择、控制命令线的连接方式和片选线的连接方式。

4.1、选取存储芯片

- 这是搭建主存系统的第一步,在这一步要决定主存所使用的存储芯片是 RAM、ROM还是两者兼用,以及每种芯片的数量;通常根据 ROM 不易失的特性,将系统程序、标准子程序和各种常数放在 ROM 中,RAM 则用于用户编程;而芯片的数量的选择上,应该尽量使主存系统的连线简单、方便。

4.2、地址线连接方式

- 通常 CPU 的地址线是要比存储芯片的地址线数多的,因此通常将 CPU 地址线的低位与存储芯片的地址线相连,以选择芯片的某一单元(字选),此部分的译码由芯片的片内逻辑完成;CPU 地址线的高位则在扩充芯片(位扩展法、字扩展法或字位同时扩展法)是使用,这部分的译码由外接译码器逻辑完成。

- 例子:

- CPU 地址线为 16 位,编号为 A15~A0,1K*4 位存储芯片只有 10 根地址线,根据低位地址线直接连接的原则,则可以将 CPU 编号为 A9~A0 的地址线与芯片地址线相连接。

4.3、数据线连接方式

- 通常,存储芯片的数据线也是比 CPU 地址线少的,通常采取存储芯片扩位,达到数据位数和 CPU 的数据线数相等;万一存储芯片的数据位数和 CPU 数据线数相等,那么就很简单了,直接相连即可。

4.4、控制命令线连接方式

- 控制命令,也就是读/写命令,CPU 读/写命令一般可以直接和存储芯片的读/写控制端连接,高电平为读,低电平为写。若是 CPU 采用读/写命令线分开的,则此时 CPU 读命令线与存储芯片允许读控制端连接,写命令线与存储芯片允许写控制端连接。

4.5、片选线连接方式

- 片选线的连接时 CPU 与存储芯片连接的关键。存储器通常由许多存储芯片叠加一起组成,哪一片选中取决于存储芯片片选控制端是否接收到 CPU 的片选有效信号。片选信号与 CPU 访存控制信号有关,因为只有当 CPU 要求访存时,才要求选中存储芯片;若 CPU 访问 I/O,则不需要存储器工作。

上一篇

下一篇

发布了184 篇原创文章 ·

获赞 24 ·

访问量 2万+

转载自blog.csdn.net/qq_42896653/article/details/104797579