目录

一般而言,要构成一个存储器,一般需要多个存储芯片一起来构成。那么多个存储芯片是如何构成一个大的存储器来进行工作的呢?

一、存储器容量的扩展

1、位扩展——增加存储字长

位扩展的目的是为了增加存储字的字长。

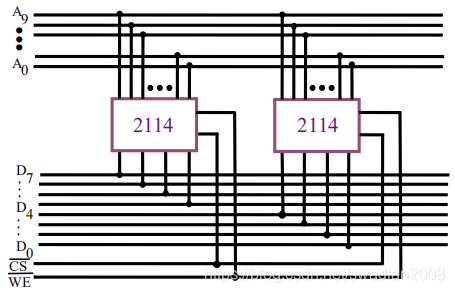

假设现在有1K(1024个)*4位的存储芯片(容量为4096bit)若干,要想构成一个1K*8位的存储器,我们可以使用两片1K*4位的存储芯片来构成,如下图

我们通过片选信号CS同时选中两片存储芯片,同时进行8位数据的读出和写入,例如,每片芯片有10跟地址线,4跟数据线,它们的连接方式如下

对于如上例子,位扩展的关键就是将两个存储芯片当成一个存储芯片来用,让两个存储芯片同时工作,同时被选中,同时做读操作,同时做写操作,要想保证同时,就是把两个芯片的片选CS,用相同的信号进行连接。

2、字扩展——增加存储字的数量

假设现在有1K*8位的存储芯片若干,要想构成一个2K*8位的存储器,我们可以使用两片1K*8位的存储芯片来构成,如下图

每一个存储芯片的容量是1K*8位,我们要构成一个2K(11位2进制位)*8的存储器,而存储芯片的每一片的容量是1K(10位二进制位),因此我们需要使用两片1K*8位的存储芯片来构成,如图

总共有11条地址线,对于A10,我们将它当成片选信号线,当A10=0时,片选选中左边的存储芯片工作,右边不工作,当A10=1时,通过一个取反,片选选择右边的芯片工作,这从外部看来就是从 0 0000000000 ~ 1 1111111111 刚好是从0~2047共2K个存储单元,每一个存储单元存放8位的二进制代码。

3、字、位扩展

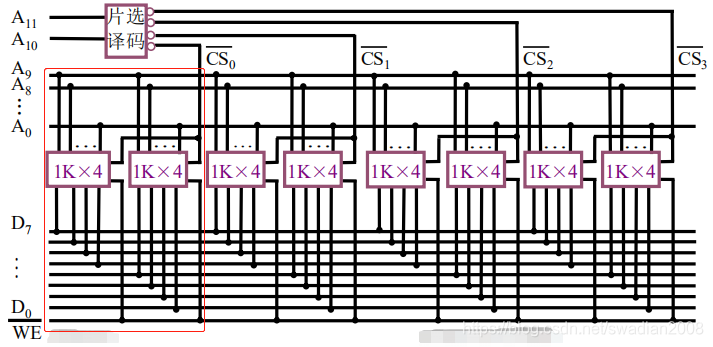

假设现在有1K*4位的存储芯片若干,要组成4K*8位的存储器,我们可以使用8片1K*4位的存储芯片来构成。首先拿两片,来构成1K*8位这样一组芯片,接着,我们需要4组来构成4K*8位的存储器。

那么如何进行连接呢?

其实就是将上述两种方法进行综合,4K*8的存储器,4K(12位二进制位,即12根地址线),8bit,就是8根数据线,1K*4bit的芯片有需要10根地址线,也就是说系统给出的从A0-A11 12根地址线,其中的10根A0-A9是直接送到芯片当中构成1K*8的一个小的存储器,剩余的2根地址线(4个地址)A11-A10,我们用来做片选信号,如下图

4K的空间我们分配到了4个存储器当中,每个存储器包含了两片1K*4bit的存储芯片,

- 第一个存储器的范围为 00 0...0(10个0)~00 1...1(10个1)

- 第二个存储器的范围为 01 0...0(10个0)~01 1...1(10个1)

- 第三个存储器的范围为 10 0...0(10个0)~10 1...1(10个1)

- 第四个存储器的范围为 11 0...0(10个0)~11 1...1(10个1)

由A11和A10来判断要访问的地址在哪一个存储器当中,我们采用译码器进行译码,当

- A11 =0 A10=0 选择第一个存储器

- A11 =0 A10=1 选择第二个存储器

- A11 =1 A10=0 选择第三个存储器

- A11 =1 A10=1 选择第四个存储器

二、存储器与 CPU 的连接

- 地址线的连接:由于CPU地址线一般多于存储芯片地址线,因此一般CPU低位地址线与存储芯片相连,高位地址线用作控制信号。

- 数据线的连接

- 读/写命令线的连接:CPU读/写命令线一般可直接与存储芯片的读/写控制端相连,通常高电平为读,低电平为写。

- 片选线的连接:由于存储器是由许多存储芯片组成的,存储芯片的片选控制线和CPU的高位地址有关,CPU的高位地址线经过译码器译码,和访存控制信号共同作用,产生存储芯片的片选信号。访存控制信号,例如,低电平有效时,访问存储器;高电平有效时,访问I/O。

- 合理选择存储芯片:系统程序区应该选择ROM ,用户程序区选择RAM。

- 其他,比如时序、负载等

三、例题练习

解题步骤:

1、写出对应的二进制地址码

CPU有16根地址线,说明芯片的寻址范围是16 x 16 = 64 K;MREO作为访存控制信号,低电平时访问存储器(顶方的横线表示),高电平时访问I/O;

系统缓存区:6000H~67FFH换算成地址范围 ——> 67FFH - 6000H= (67FFH+1-6000H) = 800H = 8 x 16 x 16 = 2 x 2^10 = 2K;

用户缓存区:6800H~6BFFH换算成地址范围 ——> 6BFFH - 6800H= (6BFFH+1-6800H) = 400H = 4 x 16 x 16 = 1 x 2^10 = 1K;

以上为10进制的换算,我们换成对应的二进制表示为:

2、确定芯片的数量及类型

根据地址范围的容量以及该范围在计算机中的作用,选择存储芯片。

根据6000H~67FFH为系统程序区的范围,应选择1片2K x 8 位的ROM,若选择其他的ROM,都超出了2K x 8 位的系统程序区范围。

根据6800H~6BFFH为用户程序区的范围,选2片 1K x 4位的RAM芯片正好满足1K x 8位的用户程序区要求

3、分配地址线

将CPU的低11位地址A10~A0与2K x 8 位的ROM地址线相连;将CPU的低10位地址A9~A0与2片 1K x 4位的RAM地址线相连。剩下的高位地址与访存控制信号MREQ共同产生存储芯片的片选信号。

4、确定片选信号