韦老师的nand flash一章操作的flash与我开发板上的nand flash型号不同,做了一些修改。我的开发板上nand flash型号为K9F2G08,即2Gbit,8bit或者说是256M,8bit。

1、配置nand flash

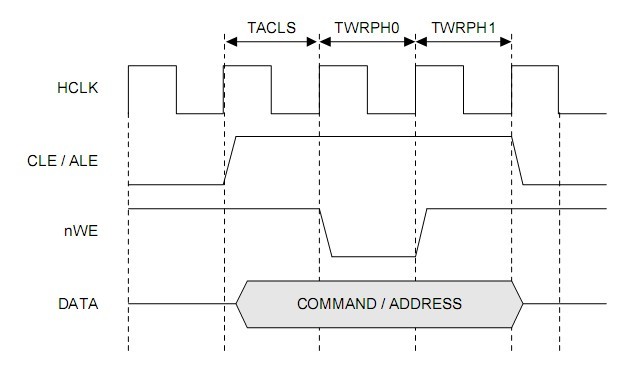

CPU的读写操作要满足flash的时序要求,主要牵涉到HCLK,CLE,ALE和nWE,如下图所示:

2440的CLK分为三种HCLK, FLCK和PCLK,默认的比例是1:1:1,在没有设置锁相环(PLLCON)的情况下,FCLK即为晶振的频率,datasheet上有这样一段话:

However, PLL is commonly known to be unstable after power-on

reset, so Fin is fed directly to FCLK instead of the Mpll (PLL output) before the software newly configures the

PLLCON. Even if the user does not want to change the default value of PLLCON register after reset, the user should

write the same value into PLLCON register by software.

而且PLLCON的默认值即使要起作用也要重新配置PLLCON寄存器。

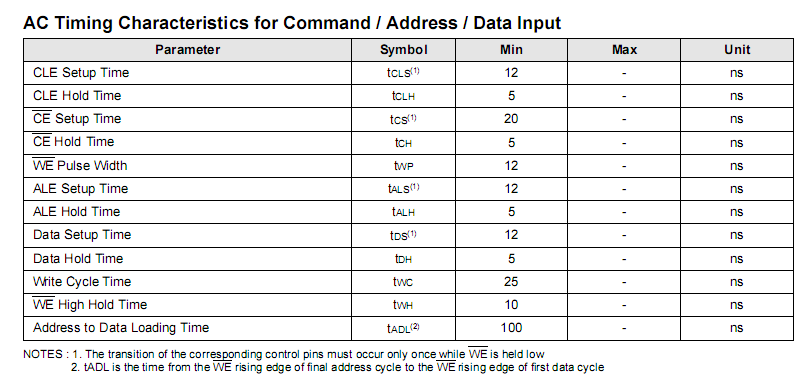

我的开发板晶振是12M的,默认HCLK为12M,而K9F2G08的时间特性如下:

MAX(setup time + hold time, WE plus width)=17ns,可以按照韦老师的设置,TACLS=0(1个HCLK),TWPRH0=3(4个HCLK),TWRPH1=0(1个HCLK),按照韦老师的说话,即使HCLK=100M,TACLS+TWPRH0+TWPRH1=6/(100M)=60ns,可以满足K9F2G08的要求。

另外NCON0,GPG13,GPG14,GPG15都是只读的,按照K9G2G08的配置应该为1 1 1 0,mini2440的原理图上有说明要去掉NR4和NR5的电阻。

2、字节对齐

flash的读操作是以页为单位的,所以起始地址和读取的大小都要是2Gbit的倍数。

3、写地址需要5个cycle

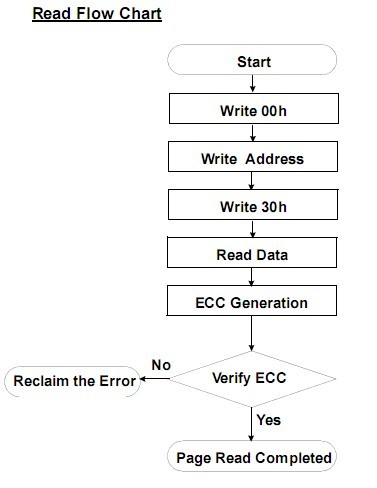

4、读flash的流程,如下所示:

完全手册中没有介绍ECC的校验,这要看烧写程序把校验码写到flash的spare area的哪个字节了,校验部分可以看赵春江老师的博客。

其他的也就差不多一样了。