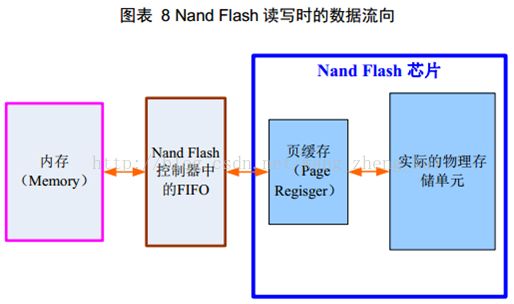

5、nand flash的数据流向

读时:

发送第一条命令00h时,实际的物理存储单元的数据先放到页缓冲(pageregister)里

发送第二条命令30h后,Nand flash控制器开始从页缓存中读取数据,读到其中fifo中,再读fifo数据到内存。

写时:

Nand flash控制器将memory中要写入nand的数据先读到其中的fifo中,发送第1条命令80h时,nand flash控制器将数据弄到nond flash的一个页缓存(pageregister)里

发送第二条命令10h后,实际的编程动作才开始,才开始把页缓存中的数据,一点点写到物理单元中去。

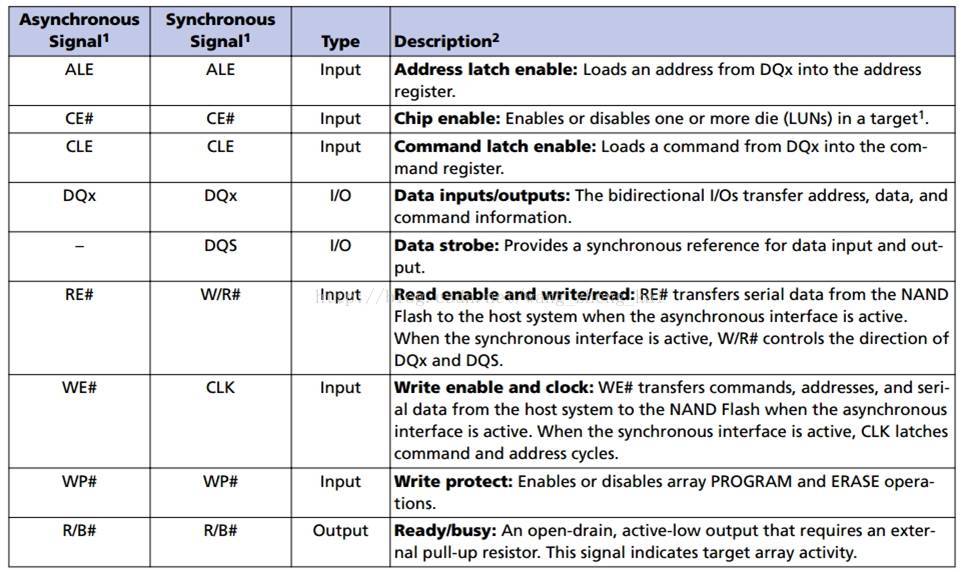

6、nand flash的引脚定义

7、nand flash的硬件连接

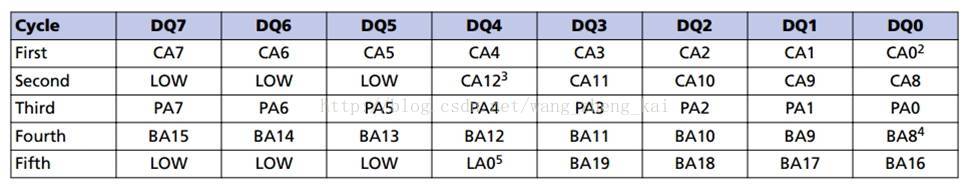

(二)Nand Flash的地址访问方法

MT29F32G08CBACA的访问地址序列

MT29F32G08CBACA总共的容量为34560MB(4G+224MB),8位位宽,需要36位的访问地址。但芯片只提供了8根地址线(复用),明显不足。所以对MT29F32G08CBACA访问时,访问地址被分割成5个地址序列,这5个地址序列中的前两个为页内地址,后三个为页面地址。两个页内地址序列有效地址位为13位,以满足对页内4096+224字节空间的访问;后三个地址序列有效地址为21位,以满足对一个芯片内共2*2048(块)*256(页)个页面的访问。MT29F32G08CBACA地址序列表见下图:

在实际驱动程序编程时用户必须严格按照这五个地址序列来向NFADDR寄存器中分别写入每个序列地址。也就是说用户发出一个完整的访问地址必须写5次NFADDR寄存器。

值得注意的是:小页面NAND flash仅仅提供了一个地址序列,8个访问地址位来访问512+16字节的页内空间,访问地址位明显足。所以小页面NANDflash将页内地址分割成A、B、C三个区,分别用不同的读命令进行访问,以弥补页内访问地址序列地址位不足的缺陷。

相对而言,大页面NAND flash它为页内地址访问提供了足够的地址序列和访问地址位(13位地址访问4096+224字节空间,足够了),所以大页面NAND flash对页内地址的访问也更为简洁。