上篇博文:【 FPGA 】FIR 滤波器之多相抽取器(Polyphase Decimator),这篇博文和它有点类似,为多相插值器。

多相插值滤波器将一组 N 个原滤波器系数 ,映射为P个多相子滤波器

,转换的公式上上篇博文:多相抽取器使用的公式一致,如下:

i从0到 P-1.

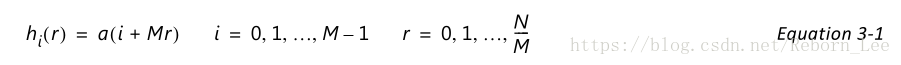

图3-27显示了多相插值滤波器结构,该选项实现了计算效率高的1-to-P插值滤波器。

每个新的输入采样x(n)同时并行送入P个多相子滤波器,同时得到P个输出采样,每个多相子滤波器输出一个采样送到滤波器输出端口,输出端口从第一个多相子滤波器开始依次选择多相子滤波器的输出。由于输入采样是同时并行送入每个多相子滤波器的,因此多相插值滤波器的输出采样速率是输入数据采样速率的P倍。相对于较高的输出采样速率,多相子滤波器工作在比较低的频率上(对于输入采样速率),同样,在每个输出点上有N个操作。

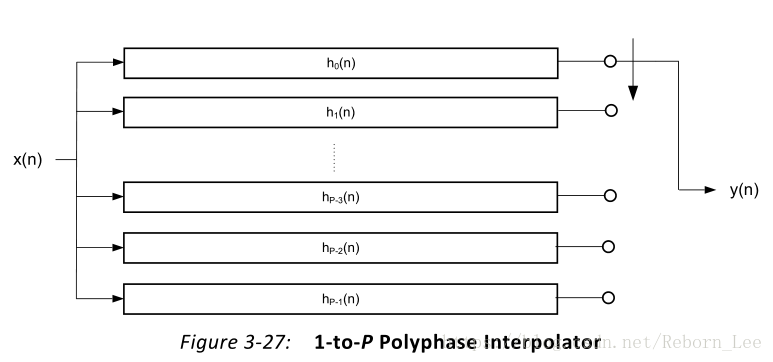

公式就懒着打了,给出英文描述:

(a) 利用对称性实现多相插值器

当应SMAC(见博文:【 FPGA 】FIR 滤波器的架构解释了SMAC为实现FIR滤波器的一种架构)实现插值滤波器时,可以用对称性技术实现系数对称处理。具体方法是通过在子滤波器系数的基础上加上和减去两个响应的非对称相位来得到包含对称系数的两个新相位。

不好理解,下面用例子说明:

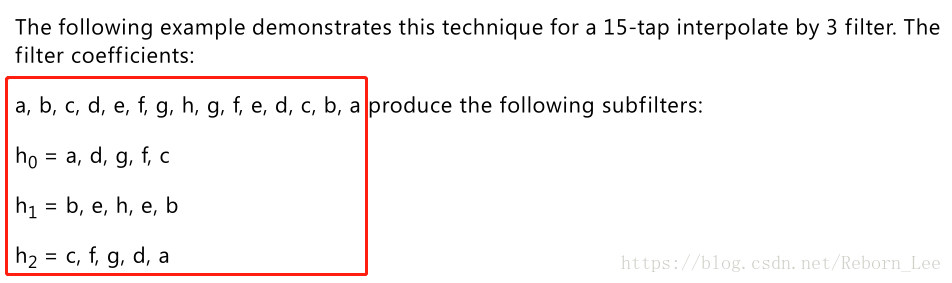

假设在一个抽头数为15的滤波器,滤波器系数如下,对该滤波器进行3倍插值,得到3个子滤波器,系数分别为:

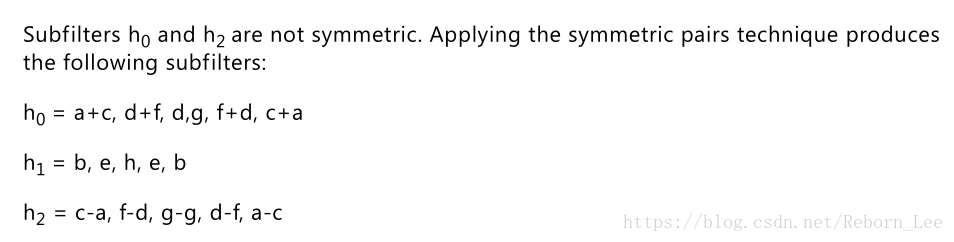

可见,第一个和第三个子滤波器是不对称的,应用对称性技术,经过简单的加法和减法运算对两个滤波器系数进行处理得到:

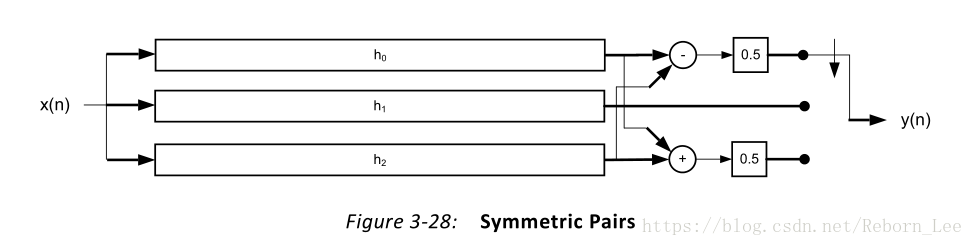

这样,h0为对称,而h2为负对称的。经过这样处理之后,实现这些子滤波器时就可以利用其对称性来节省资源。在输出端,第一个子滤波器的输出和第3个子滤波器的输出经过相加和相减运算后再乘以0.5就得到了原始滤波器的输出,如下图:

注:当用奇数个对称系数插值为2时,由于得到的多相子滤波器是对称的,所以不需要这种技术。

(b) 系数填充

关于系数填充的话题在博文中:【 FPGA 】FIR 滤波器结构和优化(二)也曾讲到过,那是对于使用MAC架构设计对称系数滤波器时提出的一种优化方案。这里的系数填充大同小异,只不过是应用到了具体的情况而已。

在对称滤波器基础上进行插值,如果速率和滤波器抽头数的组合导致子滤波器的系数个数不一致,则滤波器系数的重新组织将可能使滤波器的相位响应发生变化,即结果得到的冲激响应移位了若干个输出采样。

例如:对抽头数为14的滤波器进行4倍插值,则需要有16个抽头才合理,这样的话,我们就需要在系数矢量的前面补充一个零,在系数矢量的后面也补充一个零系数,从而保证子滤波器系数的对称性,但结果是滤波器的相位响应发生了变化。避免出现相位响应变化的方法是要么强制滤波器以非对称的结构实现,要么用能支持所选实现结构的额外系数来实现。下面给出了一些扩展到较大滤波器的例子: