上篇博文讲了半带抽取器,趁热打铁,这篇博文讲半带插值器;这种对应关系不止此一例,之前的博文:多相抽取器与多相插值器,也是这一类关系。

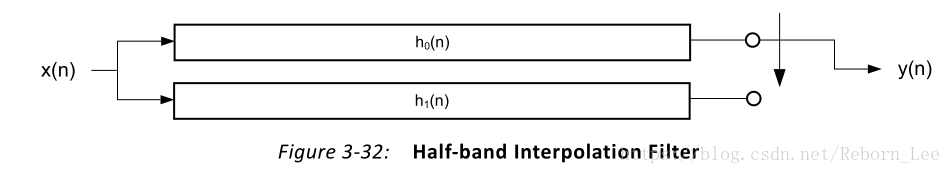

正如半带抽取器是更一般的多相抽取滤波器的优化版本一样,半带插值器是多相插值器的特殊情况。图3-32显示了半带插值器。

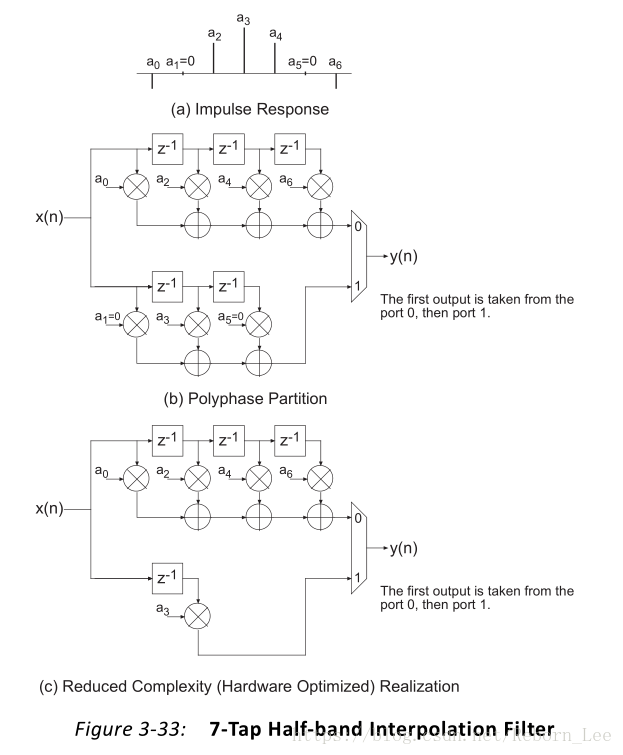

真正的半带插值器的系数集与具有相同规格的半带抽取器的系数集相同。在脉冲响应中大量的零分量的利用与半带抽取器完全相同的方式来生产硬件优化的半带插值器。

The process is presented in Figure 3-33. Figure 3-33(a) is the impulse response, Figure 3-33(b) shows the polyphase partition, and Figure 3-33(c) is the optimized architecture that has taken full advantage of the 0 entries in the coefficient data.

过程如图3-33所示。图3-33(a)为脉冲响应,图3-33(b)为多相划分,图3-33(c)为充分利用系数数据中0项的优化体系结构。

在FPGA实现中,利用零值滤波器系数的高密度特性,实现了最小面积的实现。

半带滤波器脉冲响应中的小非零偶数项

某些滤波器设计软件会导致半带滤波器脉冲响应中的奇数项产生很小的非零值。

In this situation, it can be useful to force these values to 0 and re-evaluate the frequency response to assess if it is still acceptable for the intended application.

在这种情况下,将这些值强制为0并重新评估频率响应以评估它是否仍然适用于预期应用可能很有用。

If the odd terms are not identically zero, the hardware optimizations described previously are not possible. If the small non-zero value terms cannot be ignored, the general polyphase decimator or interpolator described in Polyphase Decimator and Polyphase Interpolator, using a rate change of two, is more appropriate.

如果奇数项不是相同的零,则前面描述的硬件优化是不可能的。 如果不能忽略小的非零值项,则使用速率变化为2的多相抽取器和多相插值器中描述的一般多相抽取器或插值器更合适。