版权声明:本文为博主原创文章,未经博主允许不得转载。 https://blog.csdn.net/cc214042/article/details/61197371

序言

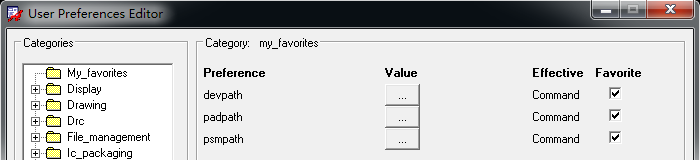

在导入网络表之前,首先请确认库文件路径是否设置好,常见的路径设置如下图所示。

实例

WARNING(SPMHNI-194): Symbol 'FW80-50' for device 'J15' not found in PSMPATH or must be "dbdoctor"ed.

Symbol extents are greater than the drawing extents ... increase the drawing extents.

现象:字面意思来看是Symbol尺度大于绘图的尺度,需要把PCB的边界扩大一些。

解决办法:执行菜单命令Setup-->Design Parameter,选择Design界面,在Extents中设置绘图区域的起始位置和页面范围。

ERROR(SPMHNI-196): Symbol 'MOLEX_47151' for device 'J1' has extra pin '25'.

ERROR(SPMHNI-196): Symbol 'MOLEX_47151' for device 'J1' has extra pin '24'.

现象:extra pin说明封装里面多出了两个管脚,编号分别为24、25,可检查下原理图,将多余的引脚删除,或者去除引脚编号。

解决办法:在Allegro中打开封装文件,对多余的pin进行编辑处理,可直接删除引脚,也可修改引脚编号。

WARNING(SPMHNI-337): Unable to load symbol 'PWC0103-M-C' for device 'J21': WARNING(SPMHUT-127): Could not find padstack PAD180_100OB40DJD.

due to ERROR(SPMHDB-274): Unable to load flash symbol 80 (Check PSMPATH setting for this symbol). [help]

现象:字面意思来看是由于缺少了flash symbol 80,导致PAD文件出错,最终导致封装文件出错。

在设计中,有部分封装是直接从brd文件导出生成的,目前怀疑是导出过程中,配置信息丢失导致问题出现。

解决办法:打开Pad_Designer工具,导入PAD文件,对使用了flash symbol文件的地方进行修改,然后保存覆盖源文件。

WARNING(SPMHNI-363): Signal model '74LVC1G125DBVR_SOT5' not found; may effect xnets and electrical constraints.

现象:未找到该model,在原理图部分修改,该警告可忽略。

总结

进行board layout时需要养成良好的习惯。先对板子的参数进行设置,比如界面大小、精度、单位、字符长度、这些都是会导致后面出错的源头。