前言

allegro的原理图设计和PCB设计用的是两款软件。而连接两款软件的桥梁是一种叫网表(netlist)的东西。网表记录了原理图中所以的元器件,元器件封装以及网络连接。

原理图规则检查(DRC)

在生成网表之前肯定需要一个完全正确无误的原理图,因此先对原理图进行规则检查。

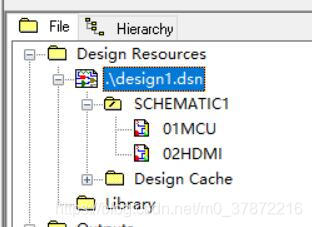

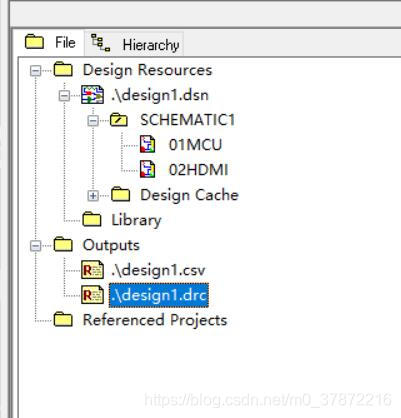

回到原理图根目录界面,选中原理图文件

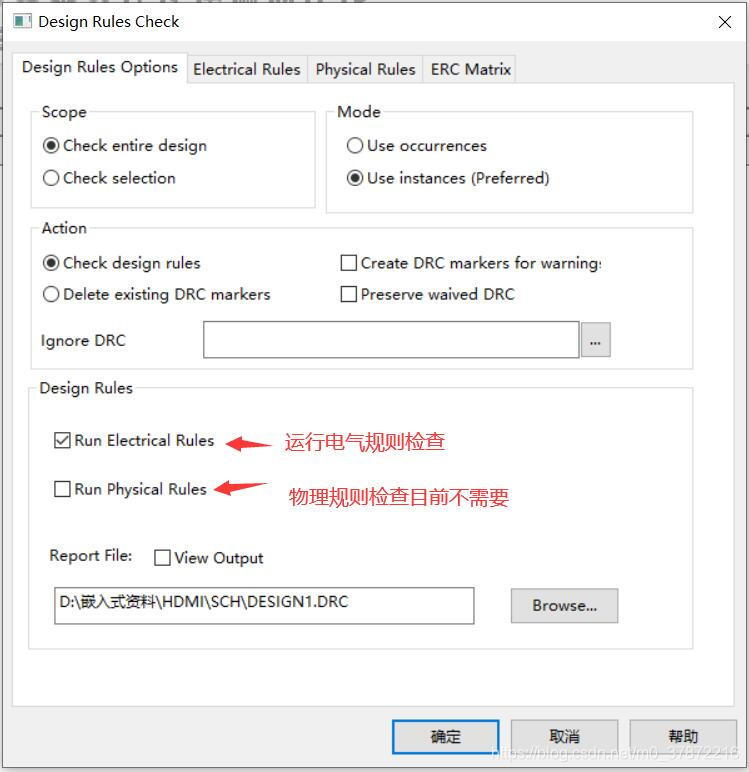

点击Tools ->Design rule check,弹出以下窗口:

这里的规则有两种,一种是electrical rules(电气规则),一种是physical rules(物理规则)。物理规则是目前所不需要的,因此在上图窗口中只勾选运行电气规则检查即可。

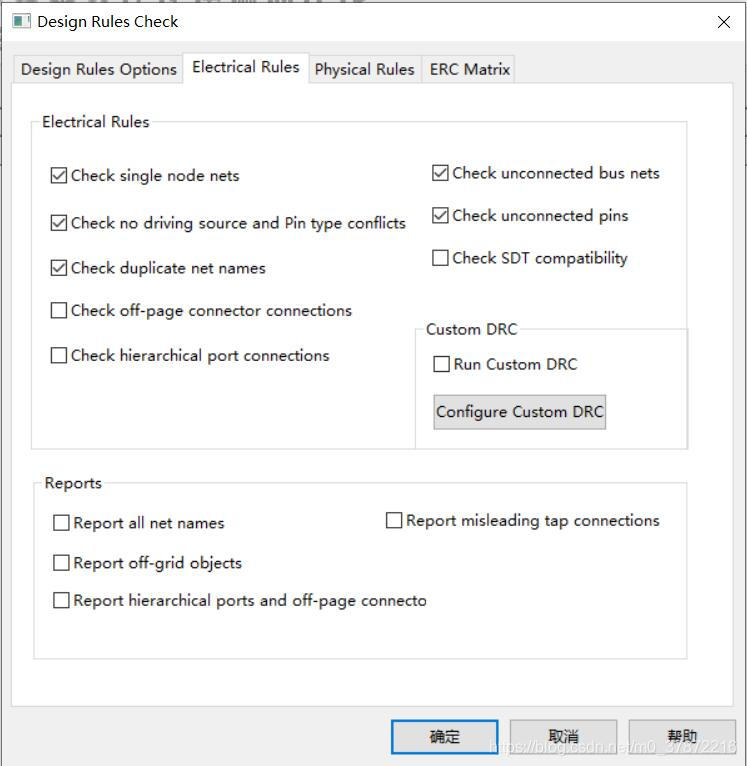

在第二栏中电气规则中,按照如上图所示,将电气规则中的五个检查情况勾选。这五个检查情况分别为:检查单端网络(看看是不是有网络没连接上);检查电源与引脚类型冲突;检查多重的标号命名(这个只要不手动改肯定不会出错,但是难免没有手动改过呢);检查未连接的总线网络;检查未连接的引脚(养成好习惯,不连接的引脚都放上叉号标记)。

确认完毕后点击确定即可,会在文件目录中生成一个drc文件。

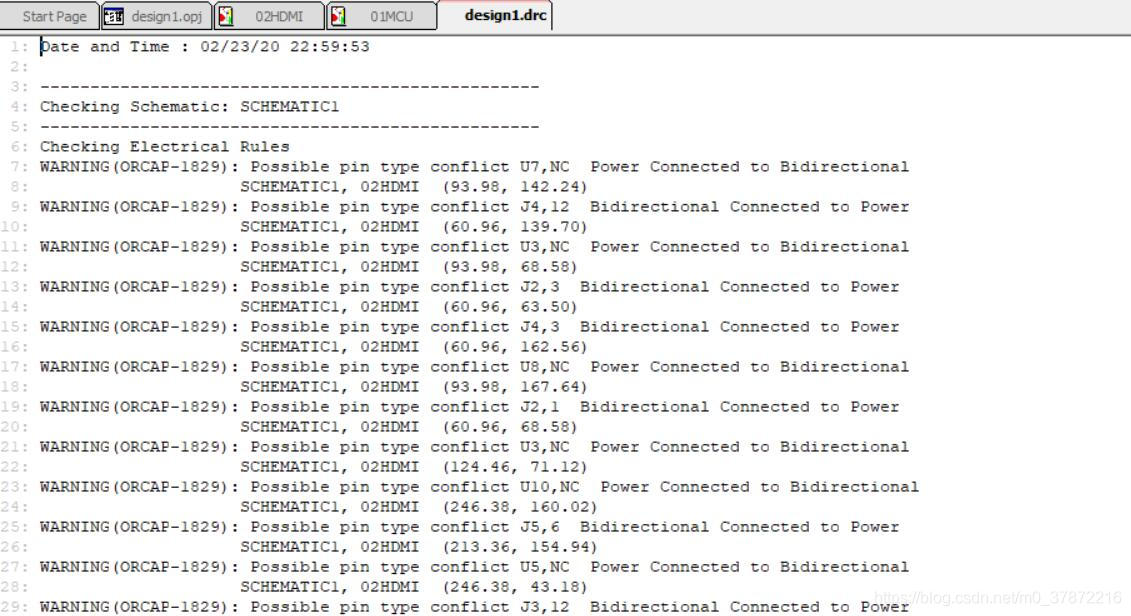

双击点开,如下图所示:

这里可以看到出现了很多的警告,类型是引脚类型遇到问题。这个是完全可以忽略的。在Orcad里认为比如磁珠链接两种地,他会认为这样做不对,电源之间不该相互连接。因此这一堆警告直接无视往下滑。

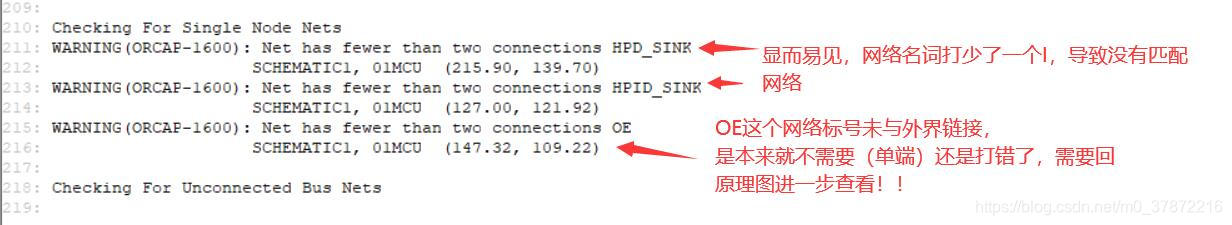

好了真正的错误出现了。在checking for single node nets里面出现了3个警告,这三个警告是货真价实的错误。

从前两个警告可以看到HPD_SINK和HPID_SINK这两个加了网络标号的网络都各只有一个引脚,显而易见,这俩网络按理说是一个,只是其中一个名字一不小心多打个“I”或者少打个“I”。

最后一个警告说明OE这个网络是单端的,按照图中的思路去查就好了。

经检查修改完毕后,再次进行DRC,直到这一部分没有警告为止。

生成网表

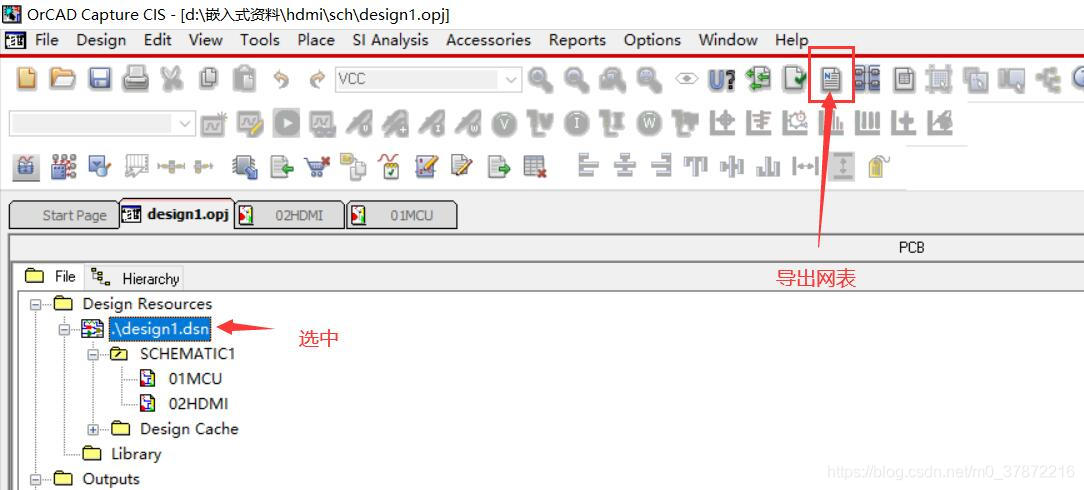

规则检查无误后生成网表。

按下图所示执行:

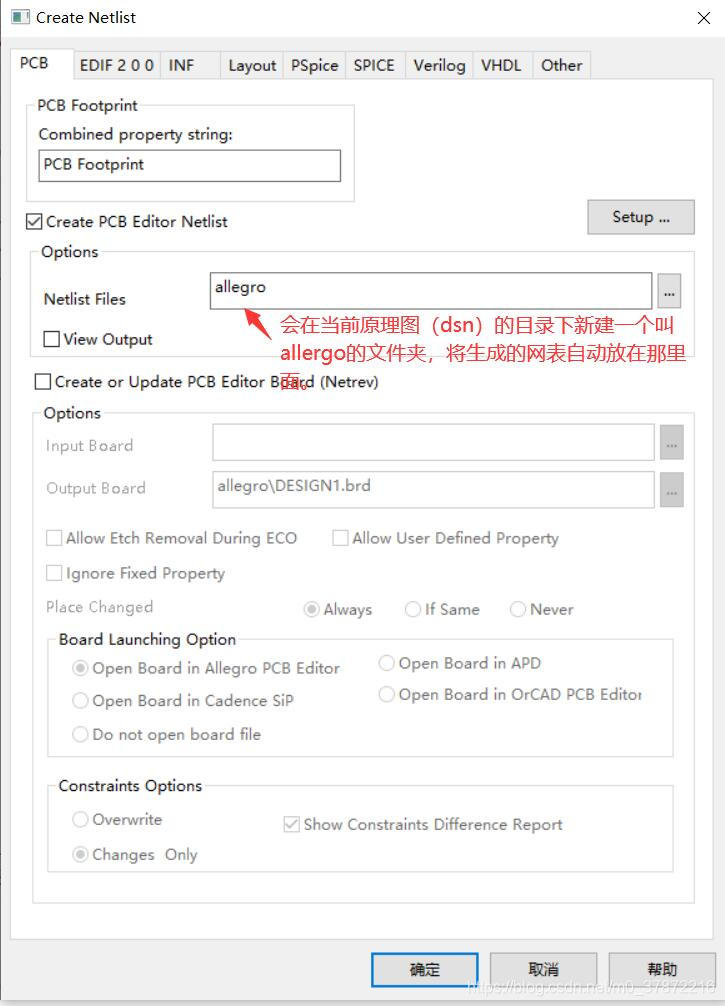

弹出以下窗口:

点击确定,随后在文件夹中可以看见网表文件们:

导入网表

首先需要新建PCB文件。

allegro做PCB的软件是这个:

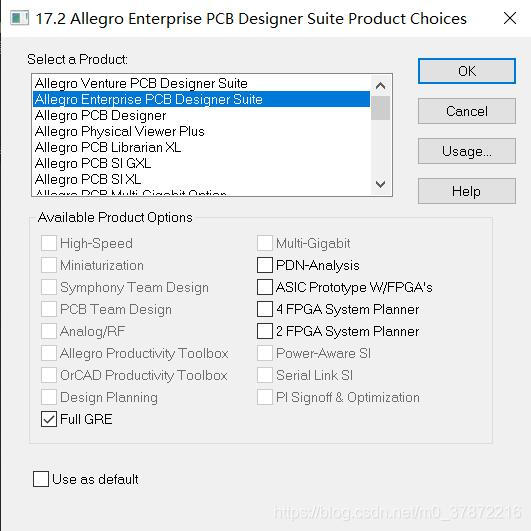

这里注意一下,第一次打开pcb editor需要手动设定软件模式, 设定错误的模式会有些功能不能用!!! 这个当时把我整憨了,怎么别人的功能我没有/怎么我的功能按键是灰色??

这里建议用下面的模式启动:阿里狗企业PCB设计套餐!

可以试试其他版本,会发现一些功能缺失。至于为什么版本之间功能差异大,这个没有查证到原因。

总之按上图的选择启动软件就好了,功能不会缺。

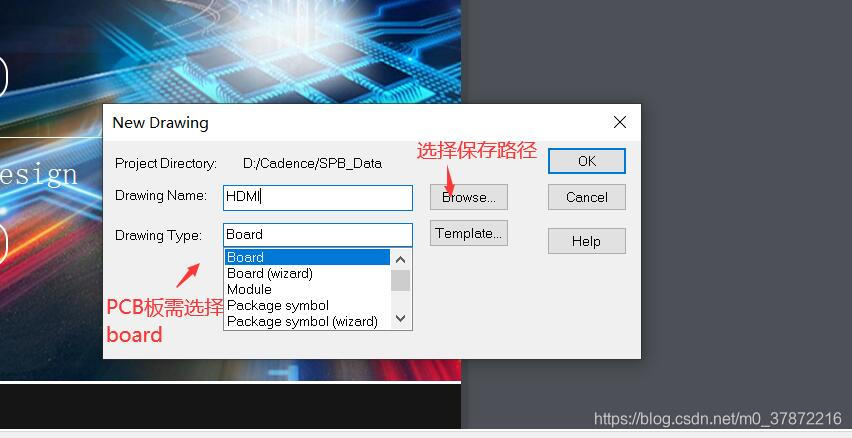

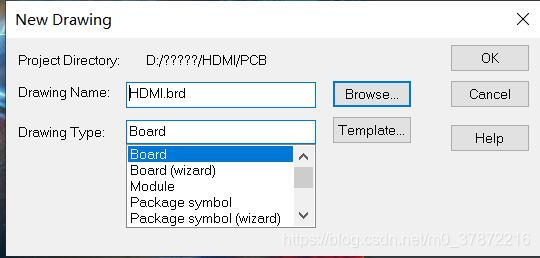

点击左上角File ->New,弹出以下窗口:

按照上图所示命名,并自己选择好保存路径。

界面按上图所示,点击OK就可以创建新的PCB文件。

allegro的pcb文件后缀名是.brd。

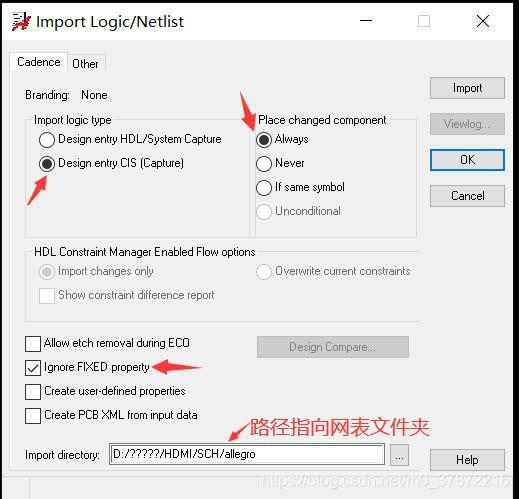

保存完毕,点击File ->import ->logic/Netlist,弹出以下窗口:

按照上图所示勾选内容。因为我们这次的网表是Orcad生成的,等于“内部人员”。所以选择第一栏的Cadence。如果是第三方软件生成的网表,那么需要使用第二栏other。

尤其要注意一下导入的路径,要选单独含有网表文件的文件夹,否则是无法导入的。

我们按照默认情况生成的网表,因此网表文件夹就叫allegro,选择好之后,点击窗口右上角的import即可。

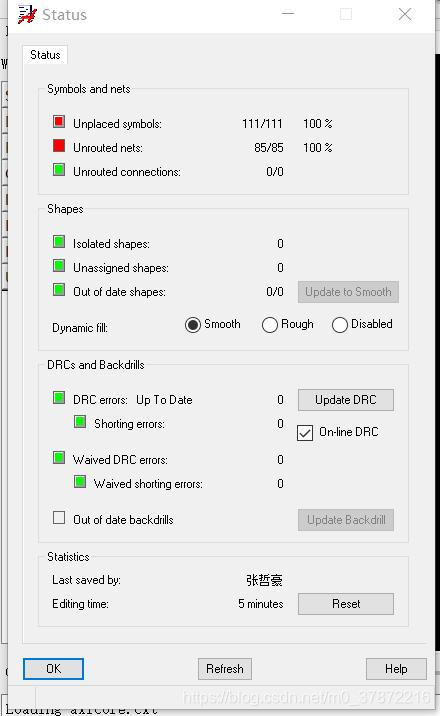

导入完毕后点击屏幕上方的Display ->status。弹出以下窗口,窗口中显示有111个没有安置的器件,有85个没有布线的网络,这就说明导入网表成功了。

如果窗口中未放置的器件与未布线的网络都是0/0的话,说明网表没有导入成功,那就需要重新检查一下,重复执行上面那一步!